ICGOO在线商城 > 集成电路(IC) > 数据采集 - ADCs/DAC - 专用型 > UDA1361TS/N1,112

- 型号: UDA1361TS/N1,112

- 制造商: NXP Semiconductors

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

UDA1361TS/N1,112产品简介:

ICGOO电子元器件商城为您提供UDA1361TS/N1,112由NXP Semiconductors设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 UDA1361TS/N1,112价格参考。NXP SemiconductorsUDA1361TS/N1,112封装/规格:数据采集 - ADCs/DAC - 专用型, ADC, Audio 24 bit 110k Serial 16-SSOP。您可以下载UDA1361TS/N1,112参考资料、Datasheet数据手册功能说明书,资料中有UDA1361TS/N1,112 详细功能的应用电路图电压和使用方法及教程。

NXP USA Inc. 的 UDA1361TS/N1,112 是一款专用型音频信号处理芯片,属于数据采集中的ADC/DAC(模数/数模转换)类别,主要用于音频信号的采集与播放。该芯片集成了立体声ADC和DAC,具备低功耗、高保真音频处理能力,适用于对音质有一定要求且注重能效的便携式音频设备。 典型应用场景包括:便携式音频播放器、多媒体终端、语音记录设备、电话会议系统、车载信息娱乐系统以及消费类电子产品中的音频接口模块。UDA1361TS/N1,112 支持 I²S 数字音频接口和 I²C 控制总线,便于与主控处理器(如MCU或DSP)连接,实现灵活的系统集成。其内置的耳机驱动器可直接驱动耳机负载,简化了外部电路设计。 此外,该芯片具备可编程增益放大器(PGA)、数字音量控制和多种电源管理模式,适合电池供电设备,有效延长续航时间。广泛应用于需要高质量音频输入输出的小型化电子设备中,是中低端音频系统中性价比较高的解决方案之一。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC ADC STEREO AUDIO 24BIT 16SSOP音频模/数转换器 IC ADC STEREO 7712 24BIT |

| 产品分类 | |

| 品牌 | NXP Semiconductors |

| 产品手册 | |

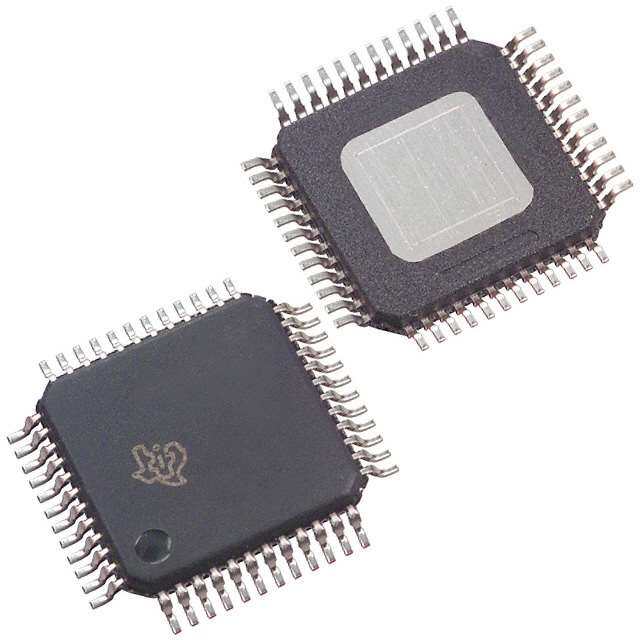

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 音频 IC,音频模/数转换器 IC,NXP Semiconductors UDA1361TS/N1,112- |

| 数据手册 | |

| 产品型号 | UDA1361TS/N1,112 |

| PCN封装 | |

| 产品目录页面 | |

| 产品种类 | 音频模/数转换器 IC |

| 供应商器件封装 | 16-SSOP |

| 其它名称 | 568-1158-5 |

| 分辨率 | 24 bit |

| 分辨率(位) | 24 b |

| 包装 | 管件 |

| 商标 | NXP Semiconductors |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Tube |

| 封装/外壳 | 16-LSSOP(0.175",4.40mm 宽) |

| 封装/箱体 | SSOP-16 |

| 工作温度 | -40°C ~ 85°C |

| 工作电源电压 | 2.4 V to 3.6 V |

| 工厂包装数量 | 1674 |

| 数据接口 | 串行 |

| 标准包装 | 93 |

| 电压-电源 | 2.4 V ~ 3.6 V |

| 电压源 | 模拟和数字 |

| 电源电流 | 10.5 mA |

| 类型 | ADC, 音频 |

| 采样率(每秒) | 110k |

| 零件号别名 | UDA1361TSDK |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

INTEGRATED CIRCUITS DATA SHEET UDA1361TS 96 kHz sampling 24-bit stereo audio ADC Product specification 2002 Nov 25 Supersedes data of 2001 Jan 17

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio UDA1361TS ADC FEATURES General • Low power consumption • 256,384,512 and768f system clock s • 2.4to3.6V power supply • Supports sampling frequency of 5to110kHz • Small package size (SSOP16) • Integrated high-pass filter to cancel DCoffset GENERAL DESCRIPTION • Power-down mode The UDA1361TS is a single chip stereo Analog-to-Digital • Supports 2V(RMS) input signals Converter(ADC) employing bitstream conversion • Easy application techniques. The low power consumption and low voltage • Master or slave operation. requirements make the device eminently suitable for use in low-voltage low-power portable digital audio equipment Multiple format output interface which incorporates recording functions. • I2S-bus and MSB-justified format compatible The UDA1361TS supports the I2S-bus data format and the MSB-justified data format with word lengths of up to • Up to24 significant bits serial output. 24bits. Advanced audio configuration • Stereo single-ended input configuration • High linearity, dynamic range and low distortion. ORDERING INFORMATION PACKAGE TYPE NUMBER NAME DESCRIPTION VERSION UDA1361TS SSOP16 plastic shrink small outline package; 16leads; body width 4.4mm SOT369-1 2002Nov25 2

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS QUICK REFERENCE DATA SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT Supplies V analog supply voltage 2.4 3.0 3.6 V DDA V digital supply voltage 2.4 3.0 3.6 V DDD I analog supply current f =48kHz DDA s operating mode − 10.5 − mA Power-down mode − 0.5 − mA I digital supply current f =48kHz DDD s operating mode − 3.5 − mA Power-down mode − 0.45 − mA T ambient temperature −40 − +85 °C amb Analog V input voltage (RMSvalue) at 0dB(FS) equivalent − 1.1 − V i(rms) at −1dB(FS) signal output − 1.0 − V (THD+N)/S total harmonic distortion-plus-noise f =48kHz s to signal ratio at −1dB − −88 −83 dB at −60dB; A-weighted − −40 −34 dB f =96kHz s at −1dB − −85 −80 dB at −60dB; A-weighted − −40 −37 dB S/N signal-to-noise ratio V =0V; A-weighted i f =48kHz − 100 − dB s f =96kHz − 100 − dB s α channel separation − 100 − dB cs 2002Nov25 3

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS BLOCK DIAGRAM handbook, full pagewidth VDDA VSSA VRP VRN Vref SYSCLK 16 15 5 4 2 8 9 VDDD UDA1361TS 10 VSSD 1 VINL ADC ΣΔ 14 MSSEL DECIMATION CLOCK FILTER CONTROL 7 PWON 3 VINR ADC ΣΔ 13 DATAO 11 DIGITAL DC-CANCELLATION 6 BCK SFOR INTERFACE FILTER 12 WS MGT451 Fig.1 Block diagram. PINNING SYMBOL PIN DESCRIPTION V 1 left channel input INL V 2 reference voltage ref handbook, halfpage VINR 3 right channel input VINL 1 16 VDDA VRN 4 negative reference voltage Vref 2 15 VSSA VRP 5 positive reference voltage VINR 3 14 MSSEL SFOR 6 data format selection input VRN 4 13 DATAO PWON 7 power control input UDA1361TS VRP 5 12 WS SYSCLK 8 system clock 256,384,512or 768f s SFOR 6 11 BCK V 9 digital supply voltage DDD V 10 digital ground PWON 7 10 VSSD SSD BCK 11 bit clock input/output SYSCLK 8 9 VDDD WS 12 word select input/output MGT452 DATAO 13 data output MSSEL 14 master/slave select V 15 analog ground SSA Fig.2 Pin configuration. V 16 analog supply voltage DDA 2002Nov25 4

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS FUNCTIONAL DESCRIPTION Table 1 Application modes using input gain stage System clock MAXIMUM RESISTOR INPUT GAIN INPUT The UDA1361TS accommodates master and slave (12kΩ) SWITCH VOLTAGE modes. The system devices must provide the system clock (RMS) regardless of master or slave mode. In the master mode a system clock frequency of 256f is required. In the slave Present 0dB 2V s mode a system frequency of 256,384,512or768fs is Present 0dB 1V automatically detected (for a system clock of 768f the s Absent 0dB 1V sampling frequency must be limited to 55kHz). The Absent 6dB 0.5V system clock must be locked in frequency to the digital interface input signals. Multiple format output interface Input level The serial interface provides the following data output The overall system gain is proportional to V , or more formats in both master and slave modes DDA accurately the potential difference between the reference (seeFigs3,4and5): voltages VVRP and VVRN. The −1dB input level at which • I2S-bus with data word length of up to 24bits THD+N/S is specified corresponds to −1dB(FS) digital • MSB-justified serial format with data word length of up to output (relative to the full-scale swing). With an input gain 24bits. switch, the input level can be calculated as follows: The master mode drives pins WS (word select; 1f ) and s at 0dB gain: V(–1 dB) = -V----V---R----P----–-----V----V---R----N-- = V (RMS) BCK (bit clock; 64fs). WS and BCK are received in slave i 3 mode. V –V at 6dB gain: V(–1 dB) = -----V---R----P-------------V---R----N-- = V (RMS) Table 2 Master/slave select i 2×3 MASTER/SLAVE MSSEL In applications where a 2V (RMS) input signal is used, a SELECT 12 kΩ resistor must be connected in series with the input L slave mode of the ADC. This forms a voltage divider together with the H master mode internal ADC resistor and ensures that only 1V (RMS) maximum is input to the IC. M (reserved for digital test) Using this application for a 2V (RMS) input signal, the gain Table 3 Select data format switch must be set to 0dB. When a 1V (RMS) input signal is input to the ADC in the same application the gain switch SFOR DATA FORMAT must be set to 6dB. L I2S-bus data format An overview of the maximum input voltage allowed against H MSB-justified data format the presence of an external resistor and the setting of the M (reserved for analog test) gain switch is given in Table1. The power supply voltage is assumed to be 3V. Decimation filter The decimation from64f is performed in two stages. The s first stage realizes a 4th-order sinx/x characteristic. This filter decreases the sample rate by8. The second stage, a FIRfilter, consists of 3half-band filters, each decimating by a factor of2. 2002Nov25 5

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS Table 4 Decimation filter characteristic Mute ITEM CONDITION VALUE(dB) On recovery from Power-down, the serial data output DATAO is held LOW until valid data is available from the Pass-band ripple 0to0.45f ±0.01 s decimation filter. This time tracks with the sampling Pass-band droop 0.45f −0.2 s frequency: Stop band >0.55 f −70 s 12288 Dynamic range 0to0.45 fs >135 t = -------f---------, t=256ms when fs=48kHz. s DCcancellation filter Power-down mode/input voltage control A IIRhigh-pass filter is provided to remove unwanted The PWON pin can control the power saving together with DCcomponents. The filter characteristics are given in the optional gain switch for 2or1V (RMS) input. Table5. The UDA1361TS supports 2V (RMS) input using a series Table 5 DCcancellation filter characteristic resistor of 12kΩ. For the definition of the pin settings for 1or2V (RMS) mode, it is assumed that this resistor is ITEM CONDITION VALUE(dB) present as a default component. Pass-band ripple − none Pass-band gain − 0 Table 6 Power-down/input voltage control Droop at0.00045f −0.031 s PWON POWER-DOWN OR GAIN Attenuation at0.00000036f >40 s L Power-down mode atDC M 0dB gain Dynamic range 0to0.45f >135 s H 6dB gain Serial interface formats handbook, full pWagSewidth LEFT RIGHT 1 2 3 ≥8 1 2 3 ≥8 BCK DATA MSB B2 LSB MSB B2 LSB MSB INPUT FORMAT I2S-BUS WS LEFT RIGHT 1 2 3 ≥8 1 2 3 ≥8 BCK DATA MSB B2 LSB MSB B2 LSB MSB B2 MGT453 MSB-JUSTIFIED FORMAT Fig.3 Serial interface formats. 2002Nov25 6

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS LIMITING VALUES In accordance with the Absolute Maximum Rating System (IEC60134). SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT V supply voltage note1 − 4.0 V DD T maximum crystal temperature − 150 °C xtal(max) T storage temperature −65 +125 °C stg T ambient temperature −40 +85 °C amb V electrostatic handling voltage HBM; note2 −3000 +3000 V es MM; note2 −300 +300 V Notes 1. All supply connections must be made to the same power supply. 2. ESD behaviour is tested in accordance with JEDECII standard: a) Human Body Model (HBM); equivalent to discharging a 100pF capacitor through a 1.5kΩ series resistor. b) Machine Model (MM); equivalent to discharging a 200pF capacitor through a 0.75μH series inductor. THERMAL CHARACTERISTICS SYMBOL PARAMETER CONDITIONS VALUE UNIT R thermal resistance from junction to ambient in free air 130 K/W th(j-a) DCCHARACTERISTICS V =V =3V; T =25°C; all voltages referenced to ground (pins10 and15); unless otherwise specified. DDD DDA amb SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT Supplies V analog supply voltage note1 2.4 3.0 3.6 V DDA V digital supply voltage note1 2.4 3.0 3.6 V DDD I analog supply current f =48kHz DDA s operating mode − 10.5 − mA Power-down mode − 0.5 − mA f =96kHz s operating mode − 10.5 − mA Power-down mode − 0.5 − mA I digital supply current f =48kHz DDD s operating mode − 3.5 − mA Power-down mode − 0.45 − mA f =96kHz s operating mode − 7.0 − mA Power-down mode − 0.65 − mA 2002Nov25 7

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT Digital input pin (SYSCLK) V HIGH-level input voltage 2.0 − 5.5 V IH V LOW-level input voltage −0.5 − +0.8 V IL |I | input leakage current − − 1 μA LI C input capacitance − − 10 pF i Digital 3-level input pins (PWON, SFOR,MSSEL) V HIGH-level input voltage 0.9V − V +0.5 V IH DD DD V MIDDLE-level input 0.4V − 0.6V V IM DD DD voltage V LOW-level input voltage −0.5 − +0.4 V IL Digital input/output pins (BCK,WS) V HIGH-level input voltage 2.0 − 5.5 V IH V LOW-level input voltage −0.5 − +0.8 V IL |I | input leakage current − − 1 μA LI C input capacitance − − 10 pF i V HIGH-level output voltage I =−2 mA 0.85V − − V OH OH DDD V LOW-level output voltage I =2mA − − 0.4 V OL OL Digital output pin (DATAO) V HIGH-level output voltage I =−2mA 0.85V − − V OH OH DDD V LOW-level output voltage I =2mA − − 0.4 V OL OL Analog V reference voltage with respect to V 0.45V 0.5V 0.55V V ref SSA DDA DDA DDA R input resistance − 12 − kΩ i C input capacitance − 20 − pF i Note 1. All power supply connections must be connected to the same external power supply unit. 2002Nov25 8

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS ACCHARACTERISTICS (ANALOG) V =V =3V; f =1kHz; T =25°C; all voltages referenced to ground (pins 10and15); unless otherwise DDD DDA i amb specified. SYMBOL PARAMETER CONDITIONS TYP. MAX. UNIT V input voltage (RMSvalue) at 0dB(FS) equivalent 1.1 − V i(rms) at −1dB(FS) signal output 1.0 − V ⎪ΔV⎪ unbalance between channels <0.1 0.4 dB i (THD+N)/S total harmonic f =48kHz s distortion-plus-noise to signal at −1dB −88 −83 dB ratio at −60dB; A-weighted −40 −34 dB f =96kHz s at −1dB −85 −80 dB at −60dB; A-weighted −40 −37 dB S/N signal-to-noise ratio V =0 V; A-weighted i f =48kHz 100 − dB s f =96kHz 100 − dB s α channel separation 100 − dB cs PSRR power supply rejection ratio f =1kHz; V =30mV(p-p) 30 − dB ripple ripple 2002Nov25 9

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS AC CHARACTERISTICS (DIGITAL) V =V =2.4to3.6V; T =−40 to +85°C; all voltages referenced to ground (pins10 and15); unless otherwise DDD DDA amb specified. SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT System clock timing T system clock cycle f =256f 35 88 780 ns sys sys s f =384f 23 59 520 ns sys s f =512f 17 44 390 ns sys s f =768f 17 30 260 ns sys s t LOW-level system clock pulse width 0.40T − 0.60T ns CWL sys sys t HIGH-level system clock pulse width 0.40T − 0.60T ns CWH sys sys Serial data timing; see Figs4and5 Tcy(CLK)(bit) bit clock period 1 64fs 64fs 64fs Hz f = --------; master mode cy T cy 1 − − 64fs Hz f = --------; slave mode cy T cy t bit clock HIGH time 50 − − ns BCKH t bit clock LOW time 50 − − ns BCKL t rise time − − 20 ns r t fall time − − 20 ns f t data output delay time − − 40 ns d(o)(D)(BCK) (from BCK falling edge) t data output delay time MSB-justified format − − 40 ns d(o)(D)(WS) (from WSedge) t data output hold time 0 − − ns h(o)(D) t word select rise time − − 20 ns r(WS) t word select fall time − − 20 ns f(WS) f word select period 1 1 1 f WS s t word select delay from BCK master mode −40 − +40 ns d(WS)(BCK) t word select set-up time slave mode 20 − − ns su(WS) t word select hold time slave mode 10 − − ns h(WS) 2002Nov25 10

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS handbook, full pagewidth WS tr tBCKH tf td(WS)(BCK) BCK tBCKL td(o)(D)(BCK) Tcy(CLK)(bit) th(o)(D) DATAO MGT454 Fig.4 Serial interface master mode timing. handbook, full pagewidth WS th(WS) tr tBCKH tf tsu(WS) BCK Tcy(CLK)(bit) tBCKL td(o)(D)(WS) th(o)(D) td(o)(D)(BCK) DATAO MGT455 Fig.5 Serial interface slave mode timing. 2002Nov25 11

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS APPLICATION INFORMATION The application information illustrated in Fig.6, is an optimum application environment. Simplification is possible at the cost of some performance degradation. handbook, full pagewidth R3 C11 1 Ω X5 1 16 VDDA 1 nF 47 μF C6 C10 (63 V) (16 V) 47 μF 100 nF (16 V) (63 V) 2 15 C3 C7 47 μF 100 nF VDDD (16 V) (63 V) R7 X3-1 C12 47 kΩ 3 14 X6 X3-2 1 nF 47 μF R6 (63 V) (16 V) 47 kΩ X3-3 4 13 X1-1 C4 C8 X1-2 47 μF 100 nF UDA1361TS X1-3 (16 V) (63 V) R1 220 Ω X1-4 VDDA 5 12 X1-5 X1-6 VDDD X1-7 R12 X4-1 47 kΩ X1-8 6 11 X4-2 X1-9 VDDD X4-3 R471 3kΩ X1-10 R4 X2-1 47 kΩ 7 10 X2-2 R5 C5 C9 X2-3 47 kΩ 47 μF 100 nF (16 V) (63 V) R2 SYSCLK 1 Ω 8 9 VDDD R10 47 Ω VD L1 BLM32A07 VDDD 4R71 Ω1 L2 BLM32A07 VDDA C1 C2 100 μF 100 μF MGU297 (16 V) (16 V) The value of capacitors C11 and C12 can be reduced. Note that changing their value will change the cut-off frequency determined by the capacitor value and the12 kΩ input resistance of the ADC. Fig.6 Application diagram. 2002Nov25 12

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS PACKAGE OUTLINE SSOP16: plastic shrink small outline package; 16 leads; body width 4.4 mm SOT369-1 D E A X c y HE v M A Z 16 9 Q pin 1 index A2 A1 (A 3 ) A θ Lp L 1 8 detail X w M e bp 0 2.5 5 mm scale DIMENSIONS (mm are the original dimensions) UNIT mAax. A1 A2 A3 bp c D(1) E(1) e HE L Lp Q v w y Z(1) θ 0.15 1.4 0.32 0.25 5.3 4.5 6.6 0.75 0.65 0.48 10o mm 1.5 0.00 1.2 0.25 0.20 0.13 5.1 4.3 0.65 6.2 1 0.45 0.45 0.2 0.13 0.1 0.18 0o Note 1. Plastic or metal protrusions of 0.2 mm maximum per side are not included. OUTLINE REFERENCES EUROPEAN ISSUE DATE VERSION IEC JEDEC JEITA PROJECTION 99-12-27 SOT369-1 MO-152 03-02-19 2002Nov25 13

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS SOLDERING • Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a Introduction to soldering surface mount packages smooth laminar wave. This text gives a very brief insight to a complex technology. • For packages with leads on two sides and a pitch (e): A more in-depth account of soldering ICs can be found in – larger than or equal to 1.27mm, the footprint our “Data Handbook IC26; Integrated Circuit Packages” longitudinal axis is preferred to be parallel to the (document order number 939865290011). transport direction of the printed-circuit board; There is no soldering method that is ideal for all surface – smaller than 1.27mm, the footprint longitudinal axis mount IC packages. Wave soldering can still be used for must be parallel to the transport direction of the certain surface mount ICs, but it is not suitable for fine pitch printed-circuit board. SMDs. In these situations reflow soldering is The footprint must incorporate solder thieves at the recommended. downstream end. Reflow soldering • For packages with leads on four sides, the footprint must be placed at a 45° angle to the transport direction of the Reflow soldering requires solder paste (a suspension of printed-circuit board. The footprint must incorporate fine solder particles, flux and binding agent) to be applied solder thieves downstream and at the side corners. to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement. During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be Several methods exist for reflowing; for example, applied by screen printing, pin transfer or syringe convection or convection/infrared heating in a conveyor dispensing. The package can be soldered after the type oven. Throughput times (preheating, soldering and adhesive is cured. cooling) vary between 100and200seconds depending on heating method. Typical dwell time is 4seconds at 250°C. Amildly-activated flux will eliminate the need for removal Typical reflow peak temperatures range from of corrosive residues in most applications. 215to250°C. The top-surface temperature of the packages should preferable be kept below 220°C for Manual soldering thick/large packages, and below 235°C for small/thin packages. Fix the component by first soldering two diagonally-opposite end leads. Use a low voltage (24V or Wave soldering less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10seconds at up to Conventional single wave soldering is not recommended 300°C. for surface mount devices (SMDs) or printed-circuit boards with a high component density, as solder bridging and When using a dedicated tool, all other leads can be non-wetting can present major problems. soldered in one operation within 2to5seconds between 270and320°C. To overcome these problems the double-wave soldering method was specifically developed. If wave soldering is used the following conditions must be observed for optimal results: 2002Nov25 14

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS Suitability of surface mount IC packages for wave and reflow soldering methods SOLDERING METHOD PACKAGE(1) WAVE REFLOW(2) BGA, LBGA, LFBGA, SQFP, TFBGA, VFBGA not suitable suitable HBCC, HBGA, HLQFP, HSQFP, HSOP, HTQFP, HTSSOP, HVQFN, not suitable(3) suitable HVSON, SMS PLCC(4), SO, SOJ suitable suitable LQFP, QFP, TQFP not recommended(4)(5) suitable SSOP, TSSOP, VSO not recommended(6) suitable Notes 1. For more detailed information on the BGA packages refer to the “(LF)BGA Application Note” (AN01026); order a copy from your NXP Semiconductors sales office. 2. All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the maximum temperature (with respect to time) and body size of the package, there is a risk that internal or external package cracks may occur due to vaporization of the moisture in them (the so called popcorn effect). For details, refer to the Drypack information in the “DataHandbook IC26; Integrated Circuit Packages; Section: Packing Methods”. 3. These packages are not suitable for wave soldering. On versions with the heatsink on the bottom side, the solder cannot penetrate between the printed-circuit board and the heatsink. On versions with the heatsink on the top side, the solder might be deposited on the heatsink surface. 4. If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave direction. Thepackage footprint must incorporate solder thieves downstream and at the side corners. 5. Wave soldering is suitable for LQFP, TQFP and QFP packages with a pitch (e) larger than 0.8mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65mm. 6. Wave soldering is suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65mm; itis definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5mm. 2002Nov25 15

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS DATA SHEET STATUS DOCUMENT PRODUCT DEFINITION STATUS(1) STATUS(2) Objective data sheet Development This document contains data from the objective specification for product development. Preliminary data sheet Qualification This document contains data from the preliminary specification. Product data sheet Production This document contains the product specification. Notes 1. Please consult the most recently issued document before initiating or completing a design. 2. The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URLhttp://www.nxp.com. DISCLAIMERS property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Limited warranty and liability ⎯ Information in this Semiconductors products in such equipment or document is believed to be accurate and reliable. applications and therefore such inclusion and/or use is at However, NXP Semiconductors does not give any the customer’s own risk. representations or warranties, expressed or implied, as to the accuracy or completeness of such information and Applications ⎯ Applications that are described herein for shall have no liability for the consequences of use of such any of these products are for illustrative purposes only. information. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the In no event shall NXP Semiconductors be liable for any specified use without further testing or modification. indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost Customers are responsible for the design and operation of savings, business interruption, costs related to the their applications and products using NXP removal or replacement of any products or rework Semiconductors products, and NXP Semiconductors charges) whether or not such damages are based on tort accepts no liability for any assistance with applications or (including negligence), warranty, breach of contract or any customer product design. It is customer’s sole other legal theory. responsibility to determine whether the NXP Semiconductors product is suitable and fit for the Notwithstanding any damages that customer might incur customer’s applications and products planned, as well as for any reason whatsoever, NXP Semiconductors’ for the planned application and use of customer’s third aggregate and cumulative liability towards customer for party customer(s). Customers should provide appropriate the products described herein shall be limited in design and operating safeguards to minimize the risks accordance with the Terms and conditions of commercial associated with their applications and products. sale of NXP Semiconductors. NXP Semiconductors does not accept any liability related Right to make changes ⎯ NXP Semiconductors to any default, damage, costs or problem which is based reserves the right to make changes to information on any weakness or default in the customer’s applications published in this document, including without limitation or products, or the application or use by customer’s third specifications and product descriptions, at any time and party customer(s). Customer is responsible for doing all without notice. This document supersedes and replaces all necessary testing for the customer’s applications and information supplied prior to the publication hereof. products using NXP Semiconductors products in order to Suitability for use ⎯ NXP Semiconductors products are avoid a default of the applications and the products or of not designed, authorized or warranted to be suitable for the application or use by customer’s third party use in life support, life-critical or safety-critical systems or customer(s). NXP does not accept any liability in this equipment, nor in applications where failure or malfunction respect. of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe 2002Nov25 16

NXP Semiconductors Product specification 96 kHz sampling 24-bit stereo audio ADC UDA1361TS Limiting values ⎯ Stress above one or more limiting Quick reference data ⎯ The Quick reference data is an values (as defined in the Absolute Maximum Ratings extract of the product data given in the Limiting values and System of IEC60134) will cause permanent damage to Characteristics sections of this document, and as such is the device. Limiting values are stress ratings only and not complete, exhaustive or legally binding. (proper) operation of the device at these or any other Non-automotive qualified products ⎯ Unless this data conditions above those given in the Recommended sheet expressly states that this specific NXP operating conditions section (if present) or the Semiconductors product is automotive qualified, the Characteristics sections of this document is not warranted. product is not suitable for automotive use. It is neither Constant or repeated exposure to limiting values will qualified nor tested in accordance with automotive testing permanently and irreversibly affect the quality and or application requirements. NXP Semiconductors accepts reliability of the device. no liability for inclusion and/or use of non-automotive Terms and conditions of commercial sale ⎯ NXP qualified products in automotive equipment or Semiconductors products are sold subject to the general applications. terms and conditions of commercial sale, as published at In the event that customer uses the product for design-in http://www.nxp.com/profile/terms, unless otherwise and use in automotive applications to automotive agreed in a valid written individual agreement. In case an specifications and standards, customer (a) shall use the individual agreement is concluded only the terms and product without NXP Semiconductors’ warranty of the conditions of the respective agreement shall apply. NXP product for such automotive applications, use and Semiconductors hereby expressly objects to applying the specifications, and (b) whenever customer uses the customer’s general terms and conditions with regard to the product for automotive applications beyond NXP purchase of NXP Semiconductors products by customer. Semiconductors’ specifications such use shall be solely at No offer to sell or license ⎯ Nothing in this document customer’s own risk, and (c) customer fully indemnifies may be interpreted or construed as an offer to sell products NXP Semiconductors for any liability, damages or failed that is open for acceptance or the grant, conveyance or product claims resulting from customer design and use of implication of any license under any copyrights, patents or the product for automotive applications beyond NXP other industrial or intellectual property rights. Semiconductors’ standard warranty and NXP Semiconductors’ product specifications. Export control ⎯ This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities. 2002Nov25 17

NXP Semiconductors provides High Performance Mixed Signal and Standard Product solutions that leverage its leading RF, Analog, Power Management, Interface, Security and Digital Processing expertise Customer notification This data sheet was changed to reflect the new company name NXP Semiconductors, including new legal definitions and disclaimers. No changes were made to the technical content, except for package outline drawings which were updated to the latest version. Contact information For additional information please visit: http://www.nxp.com For sales offices addresses send e-mail to: salesaddresses@nxp.com © NXP B.V. 2010 All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights. Printed in The Netherlands 753503/02/pp18 Date of release: 2002Nov25 Document order number: 939775010479

Datasheet下载

Datasheet下载