ICGOO在线商城 > SN74GTLPH1645DGVR

- 型号: SN74GTLPH1645DGVR

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

SN74GTLPH1645DGVR产品简介:

ICGOO电子元器件商城为您提供SN74GTLPH1645DGVR由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 提供SN74GTLPH1645DGVR价格参考以及Texas InstrumentsSN74GTLPH1645DGVR封装/规格参数等产品信息。 你可以下载SN74GTLPH1645DGVR参考资料、Datasheet数据手册功能说明书, 资料中有SN74GTLPH1645DGVR详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC BUS XCVR LVTTL-GTLP 56-TVSOP |

| 产品分类 | 逻辑 - 变换器 |

| 品牌 | Texas Instruments |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | SN74GTLPH1645DGVR |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 74GTLPH |

| 产品目录页面 | |

| 传播延迟(最大值) | 5.8ns |

| 位数 | 16 |

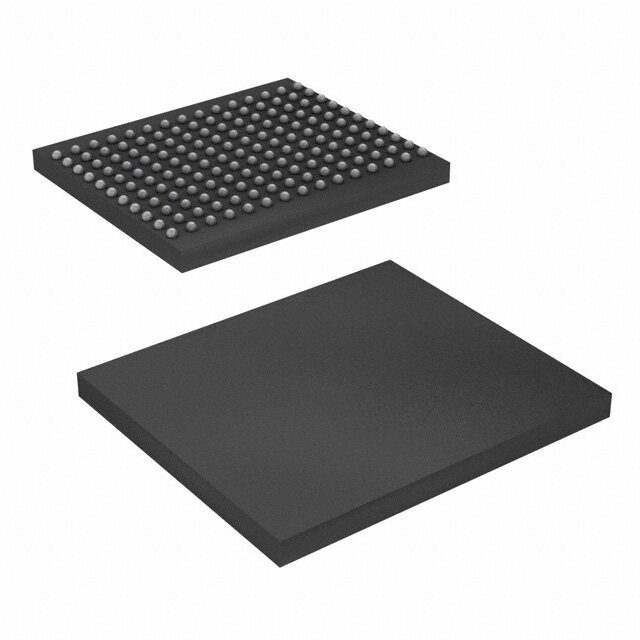

| 供应商器件封装 | 56-TVSOP |

| 其它名称 | 296-12471-6 |

| 包装 | Digi-Reel® |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 56-TFSOP(0.173",4.40mm 宽) |

| 工作温度 | -40°C ~ 85°C |

| 差分-输入:输出 | 无/无 |

| 数据速率 | - |

| 标准包装 | 1 |

| 电压-电源 | 3.15 V ~ 3.45 V |

| 输入类型 | LVTTL |

| 输出/通道数 | 8 |

| 输出类型 | GTLP |

| 通道数 | 2 |

| 逻辑功能 | 变换器,双向 |

PDF Datasheet 数据手册内容提取

SN74GTLPH1645 16-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER www.ti.com SCES290D–OCTOBER1999–REVISEDJUNE2005 FEATURES DGG OR DGV PACKAGE • MemberoftheTexasInstrumentsWidebus™ (TOP VIEW) Family • TI-OPC™CircuitryLimitsRingingon 1DIR 1 56 1OE UnevenlyLoadedBackplanes 1A1 2 55 1B1 • OEC™CircuitryImprovesSignalIntegrityand 1A2 3 54 1B2 ReducesElectromagneticInterference GND 4 53 GND • BidirectionalInterfaceBetweenGTLPSignal 1A3 5 52 1B3 1A4 6 51 1B4 LevelsandLVTTLLogicLevels • LVTTLInterfacesAre5-VTolerant VCC 7 50 VCC GND 8 49 GND • High-DriveGTLPOutputs(100mA) 1A5 9 48 1B5 • LVTTLOutputs(–24mA/24mA) 1A6 10 47 1B6 • VariableEdge-RateControl(ERC)Input GND 11 46 GND SelectsGTLPRiseandFallTimesforOptimal 1A7 12 45 1B7 Data-TransferRateandSignalIntegrityin 1A8 13 44 1B8 DistributedLoads GND 14 43 BIAS VCC • I ,Power-Up3-State,andBIASV Support ERC 15 42 VREF off CC LiveInsertion 2A1 16 41 2B1 • BusHoldonA-PortDataInputs 2A2 17 40 2B2 GND 18 39 GND • DistributedV andGNDPinsMinimize CC 2A3 19 38 2B3 High-SpeedSwitchingNoise 2A4 20 37 2B4 • Latch-UpPerformanceExceeds100mAPer GND 21 36 GND JESD78,ClassII VCC 22 35 VCC 2A5 23 34 2B5 2A6 24 33 2B6 GND 25 32 GND 2A7 26 31 2B7 2A8 27 30 2B8 2DIR 28 29 2OE DESCRIPTION/ORDERING INFORMATION The SN74GTLPH1645 is a high-drive, 16-bit bus transceiver that provides LVTTL-to-GTLP and GTLP-to-LVTTL signal-level translation. It is partitioned as two 8-bit transceivers. The device provides a high-speed interface between cards operating at LVTTL logic levels and a backplane operating at GTLP signal levels. High-speed (about three times faster than standard LVTTL or TTL) backplane operation is a direct result of GTLP's reduced output swing (<1 V), reduced input threshold levels, improved differential input, OEC™ circuitry, and TI-OPC™ circuitry. Improved GTLP OEC and TI-OPC circuits minimize bus-settling time and have been designed and tested using several backplane models. The high drive allows incident-wave switching in heavily loaded backplaneswithequivalentloadimpedancedownto11W . GTLP is the Texas Instruments derivative of the Gunning Transceiver Logic (GTL) JEDEC standard JESD 8-3. The ac specification of the SN74GTLPH1645 is given only at the preferred higher noise-margin GTLP, but the userhastheflexibilityofusingthisdeviceateitherGTL(V =1.2VandV =0.8V)orGTLP (V = 1.5 V and TT REF TT V =1V)signallevels. REF Normally, the B port operates at GTLP signal levels. The A-port and control inputs operate at LVTTL logic levels, but are 5-V tolerant and are compatible with TTL and 5-V CMOS inputs. V is the B-port differential input REF referencevoltage. Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsofTexas Instrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet. Widebus,TI-OPC,OECaretrademarksofTexasInstruments. PRODUCTIONDATAinformationiscurrentasofpublicationdate. Copyright©1999–2005,TexasInstrumentsIncorporated Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarilyincludetestingofallparameters.

SN74GTLPH1645 16-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER www.ti.com SCES290D–OCTOBER1999–REVISEDJUNE2005 DESCRIPTION/ORDERING INFORMATION (CONTINUED) This device is fully specified for live-insertion applications using I , power-up 3-state, and BIAS V . The I off CC off circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down. The power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down, which prevents driver conflict. The BIAS V circuitry precharges and preconditions the B-port input/output CC connections, preventing disturbance of active data on the backplane during card insertion or removal, and permitstruelive-insertioncapability. This GTLP device features TI-OPC circuitry, which actively limits the overshoot caused by improperly terminated backplanes, unevenly distributed cards, or empty slots during low-to-high signal transitions. This improves signal integrity,whichallowsadequatenoisemargintobemaintainedathigherfrequencies. High-drive GTLP backplane interface devices feature adjustable edge-rate control (ERC). Changing the ERC input voltage between GND and V adjusts the B-port output rise and fall times. This allows the designer to CC optimizesystemdata-transferrateandsignalintegritytothebackplaneload. Active bus-hold circuitry holds unused or undriven LVTTL data inputs at a valid logic state. Use of pullup or pulldownresistorswiththebus-holdcircuitryisnotrecommended. When V is between 0 and 1.5 V, the device is in the high-impedance state during power up or power down. CC However, to ensure the high-impedance state above 1.5 V, the output-enable (OE) input should be tied to V CC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver. ORDERINGINFORMATION T PACKAGE(1) ORDERABLEPARTNUMBER TOP-SIDEMARKING A TSSOP–DGG Tapeandreel SN74GTLPH1645DGGR GTLPH1645 –40(cid:176) Cto85(cid:176) C TVSOP–DGV Tapeandreel SN74GTLPH1645DGVR GL45 VFBGA–GQL Tapeandreel SN74GTLPH1645GQLR GL45 (1) Packagedrawings,standardpackingquantities,thermaldata,symbolization,andPCBdesignguidelinesareavailableat www.ti.com/sc/package. 2

SN74GTLPH1645 16-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER www.ti.com SCES290D–OCTOBER1999–REVISEDJUNE2005 GQL PACKAGE (TOP VIEW) 1 2 3 4 5 6 A B C D E F G H J K TERMINALASSIGNMENTS 1 2 3 4 5 6 A 1A2 1A1 1DIR 1OE 1B1 1B2 B 1A4 1A3 GND GND 1B3 1B4 C 1A5 GND V V GND 1B5 CC CC D 1A7 1A6 GND GND 1B6 1B7 E GND 1A8 1B8 BIASV CC F ERC 2A1 2B1 V REF G 2A2 2A3 GND GND 2B3 2B2 H 2A4 GND V V GND 2B4 CC CC J 2A5 2A6 GND GND 2B6 2B5 K 2A7 2A8 2DIR 2OE 2B8 2B7 3

SN74GTLPH1645 16-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER www.ti.com SCES290D–OCTOBER1999–REVISEDJUNE2005 FUNCTIONAL DESCRIPTION The SN74GTLPH1645 is a high-drive (100-mA), 16-bit bus transceiver partitioned as two 8-bit segments and is designedforasynchronouscommunication between data buses. The device transmits data from the A port to the B port or from the B port to the A port, depending on the logic level at the direction-control (DIR) input. OE can beusedtodisablethedevicesothebusesareeffectivelyisolated.Datapolarityisnoninverting. For A-to-B data flow, when OE is low and DIR is high, the B outputs take on the logic value of the A inputs. WhenOEishigh,theoutputsareinthehigh-impedancestate. ThedataflowforBtoAissimilartoAtoB,exceptOEandDIRarelow. FUNCTIONTABLES <br/> OUTPUTCONTROL INPUTS OUTPUT MODE OE DIR H X Z Isolation L L BdatatoAport Truetransparent L H AdatatoBport B-PORTEDGE-RATECONTROL(ERC) INPUTERC OUTPUT LOGIC NOMINAL B-PORT LEVEL VOLTAGE EDGERATE L GND Slow H V Fast CC 4

SN74GTLPH1645 16-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER www.ti.com SCES290D–OCTOBER1999–REVISEDJUNE2005 LOGICDIAGRAM(POSITIVELOGIC)(1) 1 1DIR 56 15 1OE ERC 55 2 1B1 1A1 42 VREF To Seven Other Channels 28 2DIR 29 2OE 41 16 2B1 2A1 To Seven Other Channels (1) PinnumbersshownarefortheDGGandDGVpackages. 5

SN74GTLPH1645 16-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER www.ti.com SCES290D–OCTOBER1999–REVISEDJUNE2005 Absolute Maximum Ratings(1) overoperatingfree-airtemperaturerange(unlessotherwisenoted) MIN MAX UNIT V CC Supplyvoltagerange –0.5 4.6 V BIASV CC A-port,ERC,andcontrolinputs –0.5 7 V Inputvoltagerange(2) V I BportandV –0.5 4.6 REF Voltagerangeappliedtoanyoutputinthe Aport –0.5 7 V V O high-impedanceorpower-offstate(2) Bport –0.5 4.6 Aport 48 I Currentintoanyoutputinthelowstate mA O Bport 200 I CurrentintoanyA-portoutputinthehighstate(3) 48 mA O ContinuouscurrentthrougheachV orGND ±100 mA CC I Inputclampcurrent V <0 –50 mA IK I I Outputclampcurrent V <0 –50 mA OK O DGGpackage 64 q Packagethermalimpedance(4) DGVpackage 48 (cid:176) C/W JA GQLpackage 42 T Storagetemperaturerange –65 150 (cid:176) C stg (1) Stressesbeyondthoselistedunder"absolutemaximumratings"maycausepermanentdamagetothedevice.Thesearestressratings only,andfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunder"recommendedoperating conditions"isnotimplied.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability. (2) Theinputandoutputnegative-voltageratingsmaybeexceedediftheinputandoutputclamp-currentratingsareobserved. (3) ThiscurrentflowsonlywhentheoutputisinthehighstateandV >V . O CC (4) ThepackagethermalimpedanceiscalculatedinaccordancewithJESD51-7. 6

SN74GTLPH1645 16-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER www.ti.com SCES290D–OCTOBER1999–REVISEDJUNE2005 Recommended Operating Conditions(1)(2)(3)(4) MIN NOM MAX UNIT V , CC Supplyvoltage 3.15 3.3 3.45 V BIASV CC GTL 1.14 1.2 1.26 V Terminationvoltage V TT GTLP 1.35 1.5 1.65 GTL 0.74 0.8 0.87 V Referencevoltage V REF GTLP 0.87 1 1.1 Bport V TT V Inputvoltage V I ExceptBport V 5.5 CC Bport V +0.05 REF V High-levelinputvoltage ERC V –0.6 V 5.5 V IH CC CC ExceptBportandERC 2 Bport V –0.05 REF V Low-levelinputvoltage ERC GND 0.6 V IL ExceptBportandERC 0.8 I Inputclampcurrent –18 mA IK I High-leveloutputcurrent Aport –24 mA OH Aport 24 I Low-leveloutputcurrent mA OL Bport 100 D t/D v Inputtransitionriseorfallrate Outputsenabled 10 ns/V D t/D V Power-upramprate 20 m s/V CC T Operatingfree-airtemperature –40 85 (cid:176) C A (1) AllunusedinputsofthedevicemustbeheldatV orGNDtoensureproperdeviceoperation.RefertotheTIapplicationreport, CC ImplicationsofSloworFloatingCMOSInputs,literaturenumberSCBA004. (2) ProperconnectionsequenceforuseoftheB-portI/OprechargefeatureisGNDandBIASV =3.3Vfirst,I/Osecond,andV =3.3V CC CC last,becausetheBIASV prechargecircuitryisdisabledwhenanyV pinisconnected.ThecontrolandV inputscanbe CC CC REF connectedanytime,butnormallyareconnectedduringtheI/Ostage.IfB-portprechargeisnotrequired,anyconnectionsequenceis acceptablebut,generally,GNDisconnectedfirst. (3) V andR canbeadjustedtoaccommodatebackplaneimpedancesifthedcrecommendedI ratingsarenotexceeded. TT TT OL (4) V canbeadjustedtooptimizenoisemargins,butnormallyistwo-thirdsV .TI-OPCcircuitryisenabledintheA-to-Bdirectionandis REF TT activatedwhenV >0.7VaboveV .IfoperatedintheA-to-Bdirection,V shouldbesettowithin0.6VofV tominimizecurrent TT REF REF TT drain. 7

SN74GTLPH1645 16-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER www.ti.com SCES290D–OCTOBER1999–REVISEDJUNE2005 Electrical Characteristics overrecommendedoperatingfree-airtemperaturerangeforGTLP(unlessotherwisenoted) PARAMETER TESTCONDITIONS MIN TYP(1) MAX UNIT V V =3.15V, I =–18mA –1.2 V IK CC I V =3.15Vto3.45V, I =–100m A V –0.2 CC OH CC V Aport I =–12mA 2.4 V OH OH V =3.15V CC I =–24mA 2 OH V =3.15Vto3.45V, I =100m A 0.2 CC OL Aport I =12mA 0.4 OL V =3.15V CC I =24mA 0.5 OL V V OL I =10mA 0.2 OL Bport V =3.15V I =64mA 0.4 CC OL I =100mA 0.55 OL I Controlinputs V =3.45V, V =0or5.5V ±10 m A I CC I Aport V =V 10 I (2) V =3.45V O CC m A OZH CC Bport V =1.5V 10 O I (2) AandBports V =3.45V, V =GND –10 m A OZL CC O I (3) Aport V =3.15V, V =0.8V 75 m A BHL CC I I (4) Aport V =3.15V, V =2V –75 m A BHH CC I I (5) Aport V =3.45V, V =0toV 500 m A BHLO CC I CC I (6) Aport V =3.45V, V =0toV –500 m A BHHO CC I CC Outputshigh 40 V =3.45V,I =0, CC O I AorBport V (A-portorcontrolinputs)=V orGND, Outputslow 40 mA CC I CC V (Bport)=V orGND I TT Outputsdisabled 40 D I (7) VCC=3.45V,OneA-portorcontrolinputatVCC–0.6V, 1.5 mA CC OtherA-portorcontrolinputsatV orGND CC C Controlinputs V =3.15Vor0 4 5 pF i I Aport V =3.15Vor0 6.5 7.5 O C pF io Bport V =1.5Vor0 9.5 11 O (1) AlltypicalvaluesareatV =3.3V,T =25(cid:176) C. CC A (2) ForI/Oports,theparametersI andI includetheinputleakagecurrent. OZH OZL (3) Thebus-holdcircuitcansinkatleasttheminimumlowsustainingcurrentatV max.I shouldbemeasuredafterloweringV toGND IL BHL IN andthenraisingittoV max. IL (4) Thebus-holdcircuitcansourceatleasttheminimumhighsustainingcurrentatV min.I shouldbemeasuredafterraisingV toV IH BHH IN CC andthenloweringittoV min. IH (5) AnexternaldrivermustsourceatleastI toswitchthisnodefromlowtohigh. BHLO (6) AnexternaldrivermustsinkatleastI toswitchthisnodefromhightolow. BHHO (7) ThisistheincreaseinsupplycurrentforeachinputthatisatthespecifiedTTLvoltagelevel,ratherthanV orGND. CC Hot-Insertion Specifications for A Port overrecommendedoperatingfree-airtemperaturerange PARAMETER TESTCONDITIONS MIN MAX UNIT I V =0, BIASV =0, V orV =0to5.5V 10 m A off CC CC I O I V =0to1.5V, V =0.5Vto3V, OE=0 ±30 m A OZPU CC O I V =1.5Vto0, V =0.5Vto3V, OE=0 ±30 m A OZPD CC O 8

SN74GTLPH1645 16-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER www.ti.com SCES290D–OCTOBER1999–REVISEDJUNE2005 Live-Insertion Specifications for B Port overrecommendedoperatingfree-airtemperaturerange PARAMETER TESTCONDITIONS MIN MAX UNIT I V =0, BIASV =0, V orV =0to1.5V 10 m A off CC CC I O I V =0to1.5V, BIASV =0, V =0.5Vto1.5V,OE=0 ±30 m A OZPU CC CC O I V =1.5Vto0, BIASV =0, V =0.5Vto1.5V,OE=0 ±30 m A OZPD CC CC O V =0to3.15V 5 mA CC I (BIASV ) BIASV =3.15Vto3.45V, V (Bport)=0to1.5V CC CC V =3.15Vto3.45V CC O 10 m A CC V V =0, BIASV =3.3V, I =0 0.95 1.05 V O CC CC O I V =0, BIASV =3.15Vto3.45V, V (Bport)=0.6V –1 m A O CC CC O Switching Characteristics overrecommendedrangesofsupplyvoltageandoperatingfree-airtemperature, V =1.5VandV =1VforGTLP(seeFigure1) TT REF FROM TO PARAMETER EDGERATE(1) MIN TYP(2) MAX UNIT (INPUT) (OUTPUT) t 3.9 7.2 PLH A B Slow ns t 3.1 8.4 PHL t 2.6 5.7 PLH A B Fast ns t 2.1 5.8 PHL t 4.1 7.3 en OE B Slow ns t 4 9.4 dis t 2.9 5.9 en OE B Fast ns t 4 6.9 dis Slow 3 t Risetime,Boutputs(20%to80%) ns r Fast 1.5 Slow 4 t Falltime,Boutputs(80%to20%) ns f Fast 2.5 t 0.5 6.7 PLH B A ns t 1.2 4.5 PHL t 1.1 6.3 en OE A ns t 1.7 5.1 dis (1) Slow(ERC=GND)andFast(ERC=V ) CC (2) AlltypicalvaluesareatV =3.3V,T =25(cid:176) C. CC A 9

SN74GTLPH1645 16-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER www.ti.com SCES290D–OCTOBER1999–REVISEDJUNE2005 PARAMETER MEASUREMENT INFORMATION 6 V 1.5 V 500 W S1 Open From Output 12.5 W Under Test GND TEST S1 From Output Test (seCeL N= o5t0e pAF) 500 W ttPPLLHZ//ttPPHZLL O6p Ven UndeCrL T =e s3t0 pF Point tPHZ/tPZH GND (see Note A) LOAD CIRCUIT FOR A OUTPUTS LOAD CIRCUIT FOR B OUTPUTS 3 V Input 1.5 V 1.5 V 0 V tPLH tPHL VOH Output 1 V 1 V 3 V VOL Output 1.5 V 1.5 V VOLTAGE WAVEFORMS Control PROPAGATION DELAY TIMES 0 V (A port to B port) tPZL tPLZ Output 1.5 V 3 V Waveform 1 Input 1 V 1 V S1 at 6 V 1.5 V VOL + 0.3 V 0 V (see Note B) VOL tPLH tPHL tPZH tPHZ VOH Output VOH Output 1.5 V 1.5 V Waveform 2 1.5 V VOH − 0.3 V S1 at GND VOL (see Note B) ≈0 V VOLTAGE WAVEFORMS VOLTAGE WAVEFORMS PROPAGATION DELAY TIMES ENABLE AND DISABLE TIMES (B port to A port) (A port) NOTES: A. CL includes probe and jig capacitance. B. Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control. C. All input pulses are supplied by generators having the following characteristics: PRR ≈ 10 MHz, ZO = 50 W , tr ≈(cid:0)2 ns, tf ≈(cid:0)2 ns. D. The outputs are measured one at a time, with one transition per measurement. Figure1.LoadCircuitsandVoltageWaveforms 10

SN74GTLPH1645 16-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER www.ti.com SCES290D–OCTOBER1999–REVISEDJUNE2005 Distributed-Load Backplane Switching Characteristics The preceding switching characteristics table shows the switching characteristics of the device into a lumped load (Figure 1). However, the designer's backplane application probably is a distributed load. The physical representation is shown in Figure 2. This backplane, or distributed load, can be approximated closely to a resistor inductance capacitance (RLC) circuit, as shown in Figure 3. This device has been designed for optimum performance in this RLC circuit. The following switching characteristics table shows the switching characteristics of the device into the RLC load, to help the designer better understand the performance of the GTLP device in thistypicalbackplane.Seewww.ti.com/sc/gtlpformoreinformation. 1.5 V 1.5 V W2 0.25” 1” ZO = 50 W 1” 0.25” W2 2 2 Conn. Conn. Conn. Conn. 1” 1” 1” 1” Rcvr Rcvr Rcvr Drvr Slot 1 Slot 2 Slot 19 Slot 20 Figure2.High-DriveTestBackplane 1.5 V 11 W From Output LL = 14 nH Test Under Test Point CL = 18 pF Figure3.High-DriveRLCNetwork 11

SN74GTLPH1645 16-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE BUS TRANSCEIVER www.ti.com SCES290D–OCTOBER1999–REVISEDJUNE2005 Switching Characteristics overrecommendedrangesofsupplyvoltageandoperatingfree-airtemperature, V =1.5VandV =1VforGTLP(seeFigure3) TT REF FROM TO PARAMETER EDGERATE(1) TYP(2) UNIT (INPUT) (OUTPUT) t 4.9 PLH A B Slow ns t 4.9 PHL t 3.7 PLH A B Fast ns t 3.7 PHL t 5.1 en OE B Slow ns t 5.4 dis t 4.1 en OE B Fast ns t 4.1 dis Slow 2 t Risetime,Boutputs(20%to80%) ns r Fast 1.2 Slow 2.5 t Falltime,Boutputs(80%to20%) ns f Fast 1.8 (1) Slow(ERC=GND)andFast(ERC=V ) CC (2) AlltypicalvaluesareatV =3.3V,T =25(cid:176) C.AllvaluesarederivedfromTI-SPICEmodels. CC A 12

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 PACKAGING INFORMATION Orderable Device Status Package Type Package Pins Package Eco Plan Lead/Ball Finish MSL Peak Temp Op Temp (°C) Device Marking Samples (1) Drawing Qty (2) (6) (3) (4/5) 74GTLPH1645DGGRG4 ACTIVE TSSOP DGG 56 2000 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 GTLPH1645 & no Sb/Br) SN74GTLPH1645DGGR ACTIVE TSSOP DGG 56 2000 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 GTLPH1645 & no Sb/Br) SN74GTLPH1645DGVR ACTIVE TVSOP DGV 56 2000 Green (RoHS NIPDAU Level-1-260C-UNLIM -40 to 85 GL45 & no Sb/Br) (1) The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs. LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. (2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free". RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption. Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement. (3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device. (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device. (6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width. Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release. Addendum-Page 1

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis. Addendum-Page 2

PACKAGE MATERIALS INFORMATION www.ti.com 12-Aug-2013 TAPE AND REEL INFORMATION *Alldimensionsarenominal Device Package Package Pins SPQ Reel Reel A0 B0 K0 P1 W Pin1 Type Drawing Diameter Width (mm) (mm) (mm) (mm) (mm) Quadrant (mm) W1(mm) SN74GTLPH1645DGGR TSSOP DGG 56 2000 330.0 24.4 8.6 15.6 1.8 12.0 24.0 Q1 SN74GTLPH1645DGVR TVSOP DGV 56 2000 330.0 24.4 6.8 11.7 1.6 12.0 24.0 Q1 PackMaterials-Page1

PACKAGE MATERIALS INFORMATION www.ti.com 12-Aug-2013 *Alldimensionsarenominal Device PackageType PackageDrawing Pins SPQ Length(mm) Width(mm) Height(mm) SN74GTLPH1645DGGR TSSOP DGG 56 2000 367.0 367.0 45.0 SN74GTLPH1645DGVR TVSOP DGV 56 2000 367.0 367.0 45.0 PackMaterials-Page2

MECHANICAL DATA MPDS006C – FEBRUARY 1996 – REVISED AUGUST 2000 DGV (R-PDSO-G**) PLASTIC SMALL-OUTLINE 24 PINS SHOWN 0,23 0,40 0,07 M 0,13 24 13 0,16 NOM 4,50 6,60 4,30 6,20 Gage Plane 0,25 0°–(cid:1)8° 0,75 1 12 0,50 A Seating Plane 0,15 1,20 MAX 0,08 0,05 PINS ** 14 16 20 24 38 48 56 DIM A MAX 3,70 3,70 5,10 5,10 7,90 9,80 11,40 A MIN 3,50 3,50 4,90 4,90 7,70 9,60 11,20 4073251/E 08/00 NOTES: A. All linear dimensions are in millimeters. B. This drawing is subject to change without notice. C. Body dimensions do not include mold flash or protrusion, not to exceed 0,15 per side. D. Falls within JEDEC: 24/48 Pins – MO-153 14/16/20/56 Pins – MO-194 • POST OFFICE BOX 655303 DALLAS, TEXAS 75265

PACKAGE OUTLINE DGG0056A TSSOP - 1.2 mm max height SCALE 1.200 SMALL OUTLINE PACKAGE C 8.3 SEATING PLANE TYP 7.9 A PIN 1 ID 0.1 C AREA 54X 0.5 56 1 14.1 2X 13.9 13.5 NOTE 3 28 29 0.27 B 6.2 56X 0.17 1.2 MAX 6.0 0.08 C A B (0.15) TYP 0.25 SEE DETAIL A GAGE PLANE 0.15 0.75 0 - 8 0.05 0.50 DETAIL A TYPICAL 4222167/A 07/2015 NOTES: 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side. 4. Reference JEDEC registration MO-153. www.ti.com

EXAMPLE BOARD LAYOUT DGG0056A TSSOP - 1.2 mm max height SMALL OUTLINE PACKAGE 56X (1.5) SYMM 1 56 56X (0.3) 54X (0.5) (R0.05) TYP SYMM 28 29 (7.5) LAND PATTERN EXAMPLE SCALE:6X SOOPLEDNEINRG MASK METAL MSOELTDAEL RU NMDAESRK SOOPLEDNEINRG MASK 0.05 MAX 0.05 MIN ALL AROUND ALL AROUND NON SOLDER MASK SOLDER MASK DEFINED DEFINED SOLDER MASK DETAILS 4222167/A 07/2015 NOTES: (continued) 5. Publication IPC-7351 may have alternate designs. 6. Solder mask tolerances between and around signal pads can vary based on board fabrication site. www.ti.com

EXAMPLE STENCIL DESIGN DGG0056A TSSOP - 1.2 mm max height SMALL OUTLINE PACKAGE 56X (1.5) SYMM 1 56 56X (0.3) 54X (0.5) (R0.05) TYP SYMM 28 29 (7.5) SOLDER PASTE EXAMPLE BASED ON 0.125 mm THICK STENCIL SCALE:6X 4222167/A 07/2015 NOTES: (continued) 7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations. 8. Board assembly site may have different recommendations for stencil design. www.ti.com

IMPORTANTNOTICEANDDISCLAIMER TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources. TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated

Datasheet下载

Datasheet下载

.jpg)