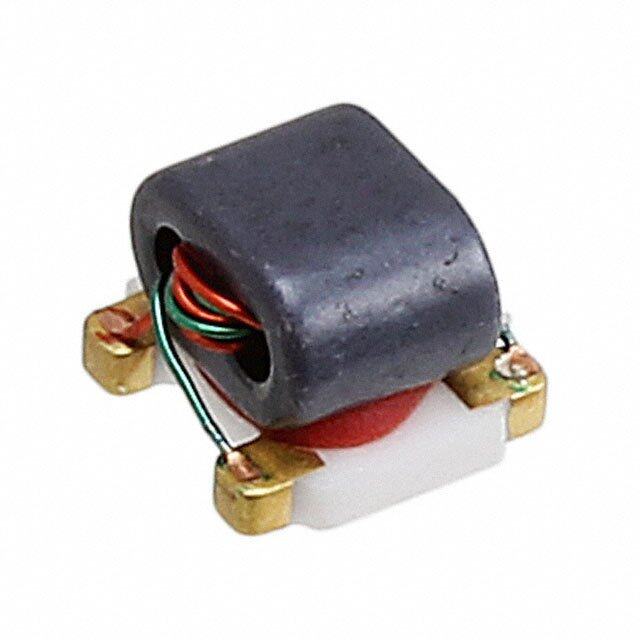

图片仅供参考

详细数据请看参考数据手册

- 型号: DS1020-50

- 制造商: Maxim

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

产品简介:

ICGOO电子元器件商城为您提供DS1020-50由Maxim设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 DS1020-50价格参考。MaximDS1020-50封装/规格:未分类, 暂无。您可以下载DS1020-50参考资料、Datasheet数据手册功能说明书,资料中有DS1020-50 详细功能的应用电路图电压和使用方法及教程。

DS1020-50 是 Maxim Integrated(现属 Analog Devices)推出的 5 级可编程延迟线,标称延迟为 50 ns(典型值),具有 TTL 兼容输入/输出、单电源供电(+5V)、低抖动和高重复精度等特点。其主要应用场景包括: - 数字系统时序校准:用于补偿 PCB 走线、逻辑器件或时钟分配路径中的传播延迟差异,确保多路信号(如地址/数据/控制信号)同步到达目标芯片(如 FPGA、ASIC 或存储器),避免建立/保持时间违例。 - 脉冲宽度调节与波形整形:通过级联或选通不同抽头,实现窄脉冲生成、延时触发、去抖动(如按键或开关信号)及时钟边沿对齐(如将时钟上升沿与数据有效窗口中心对齐)。 - 测试与测量设备:在ATE(自动测试设备)或逻辑分析仪中,作为可调延迟单元,用于精确控制激励信号时序或校准通道间延迟偏差。 - 通信接口时序适配:在早期并行总线(如ISA、PCI 辅助电路)或定制接口中,协调不同时序特性的器件间通信,提升系统稳定性。 需注意:DS1020-50 为较早期器件(已停产),现多被更灵活的可编程延迟芯片(如 AD9508)或 FPGA 内部延迟单元替代;设计中应评估供货状态,并注意其固定步进(约10 ns/级)和温度/电压敏感性,必要时加入温补或校准机制。

产品参数

图文手册

常见问题

DS1020-50 相关产品

猜你喜欢

最新产品推荐

其他制造商