ICGOO在线商城 > 集成电路(IC) > PMIC - AC-DC 转换器,离线开关 > VIPER17HD

- 型号: VIPER17HD

- 制造商: STMicroelectronics

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

VIPER17HD产品简介:

ICGOO电子元器件商城为您提供VIPER17HD由STMicroelectronics设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 VIPER17HD价格参考。STMicroelectronicsVIPER17HD封装/规格:PMIC - AC-DC 转换器,离线开关, Converter Offline Flyback Topology 115kHz 16-SO。您可以下载VIPER17HD参考资料、Datasheet数据手册功能说明书,资料中有VIPER17HD 详细功能的应用电路图电压和使用方法及教程。

STMicroelectronics的VIPER17HD是一款高性能、高集成度的离线式开关电源(AC-DC转换器)芯片,广泛应用于需要高效、紧凑和低成本电源解决方案的场景。以下是其主要应用场景: 1. 消费电子设备 - 充电器和适配器:适用于手机、平板电脑、蓝牙耳机等便携式设备的充电器或USB适配器。 - 家电产品:如智能音箱、小型厨房电器(电水壶、咖啡机)、遥控器、风扇等,提供稳定的低功耗电源。 - LED照明驱动:用于驱动LED灯泡、灯带或其他照明设备,支持恒流/恒压输出。 2. 工业应用 - 传感器供电:为各种工业传感器(如温度、湿度、压力传感器)提供稳定电源。 - 物联网(IoT)设备:为智能家居、工业自动化中的IoT节点供电,满足低功耗需求。 - 小型控制器:如PLC模块、继电器板等,提供高效的电源转换。 3. 医疗设备 - 便携式医疗设备:如电子体温计、血糖仪、脉搏血氧仪等,要求低功耗和高效率的电源方案。 - 辅助设备:如家用制氧机、小型按摩器等,提供可靠的电源支持。 4. 通信设备 - 网络设备:如路由器、交换机、网桥的小型电源模块。 - 无线模块:为Wi-Fi、蓝牙、Zigbee等无线通信模块供电。 5. 其他应用 - 电池充电管理:用于NiMH、Li-ion等电池充电器中,实现高效充电功能。 - 玩具和游戏设备:为电子玩具、手柄等提供稳定的电源。 - 安防设备:如监控摄像头、门铃等,需要长时间稳定运行的电源。 特点与优势 VIPER17HD具有高集成度,内置高压MOSFET、PWM控制器和保护电路,能够简化设计并减少外部元件数量。其工作电压范围宽(85V~265V AC),适合全球电网输入;同时具备低待机功耗、高效率和多种保护功能(如过载保护、短路保护、过热保护等),非常适合对能效和可靠性要求较高的应用场景。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC OFFLINE CONV PWM OVP 16SOIC交流/直流转换器 Off-Line High Volt Converter |

| 产品分类 | |

| 品牌 | STMicroelectronics |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 电源管理 IC,交流/直流转换器,STMicroelectronics VIPER17HDVIPer™ plus |

| 数据手册 | |

| 产品型号 | VIPER17HD |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=30015 |

| 产品种类 | 交流/直流转换器 |

| 供应商器件封装 | 16-SO |

| 其它有关文件 | http://www.st.com/web/catalog/sense_power/FM142/CL1454/SC432/SS1635/PF204720?referrer=70071840 |

| 功率(W) | 12W |

| 包装 | 管件 |

| 占空比-最大 | 80 % |

| 参考设计库 | http://designs.digikey.com/library/4294959902/4294959891/509http://designs.digikey.com/library/4294959904/4294959863/457http://designs.digikey.com/library/4294959904/4294959863/445http://designs.digikey.com/library/4294959904/4294959862/423 |

| 商标 | STMicroelectronics |

| 安装风格 | SMD/SMT |

| 封装 | Tube |

| 封装/外壳 | 16-SOIC(0.154",3.90mm 宽) |

| 封装/箱体 | SO-16 |

| 工作温度 | -40°C ~ 150°C |

| 工作温度范围 | - 40 C to + 150 C |

| 工厂包装数量 | 1000 |

| 开关频率 | 115 kHz |

| 拓扑结构 | Flyback |

| 标准包装 | 50 |

| 特色产品 | http://www.digikey.cn/product-highlights/cn/zh/stmicroelectronics-viperplus-converters/3895 |

| 电压-击穿 | 800V |

| 电压-输入 | 8.5 V ~ 23.5 V |

| 电压-输出 | - |

| 电源电流 | 1.8 mA |

| 类型 | Offline Converter |

| 系列 | VIPER17 |

| 绝缘 | Isolated |

| 视频文件 | http://www.digikey.cn/classic/video.aspx?PlayerID=1364138032001&width=640&height=455&videoID=61449184001 |

| 输入/电源电压—最大值 | 23.5 V |

| 输入/电源电压—最小值 | 8.5 V |

| 输出功率 | 10 W |

| 输出电压 | 800 V |

| 输出电流 | 420 mA |

| 输出端数量 | 1 Output |

| 输出隔离 | 隔离 |

| 配用 | /product-detail/zh/STEVAL-ISA124V1/497-14516-ND/4759388/product-detail/zh/STEVAL-ILL017V1/497-9050-ND/2122341/product-detail/zh/STEVAL-ISA062V1/497-9007-ND/2092935/product-detail/zh/STEVAL-ISA060V1/497-8513-ND/2019969 |

| 频率范围 | 103kHz ~ 127kHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

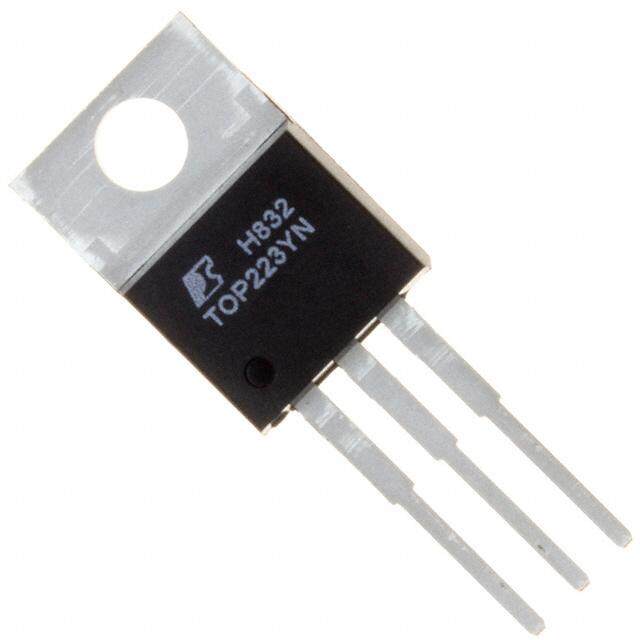

VIPER17 Energy saving VIPerPlus: HV switching regulator for flyback converter Datasheet - production data Limiting current with adjustable set point Adjustable and accurate overvoltage protection On-board soft-start Safe auto-restart after a fault condition Hysteresis thermal shutdown Applications Adapters for PDA, camcorders, shavers, cellular phones, videogames Auxiliary power supply for LCD/PDP TV, monitors, audio systems, computer, Figure 1: Typical topology industrial systems, LED driver, No el-cap LED driver SMPS for set-top boxes, DVD players and recorders, white goods Description The device is an off-line converter with an 800 V rugged power section, a PWM control, two levels of overcurrent protection, overvoltage and overload protections, hysteresis thermal protection, soft-start and safe auto-restart after any fault condition removal. The burst mode operation and the device’s very low consumption meet the standby energy saving regulations. Features Advance frequency jittering reduces EMI filter cost. Brown-out function protects the switch 800 V avalanche rugged power section mode power supply when the rectified input PWM operation with frequency jittering for voltage level is below the normal minimum level low EMI specified for the system. The high voltage startup Operating frequency: circuit is embedded in the device. 60 kHz for L type 115 kHz for H type Standby power < 30 mW at 265 V AC Table 1: Device summary Order code Package Packing VIPER17LN / VIPER17HN DIP-7 Tube VIPER17HD / VIPER17LD Tube SO16 narrow VIPER17HDTR / VIPER17LDTR Tape and reel February 2017 DocID14419 Rev 11 1/31 This is information on a product in full production. www.st.com

Contents VIPER17 Contents 1 Block diagram .................................................................................. 3 2 Typical power .................................................................................. 3 3 Pin settings ...................................................................................... 4 4 Electrical data .................................................................................. 5 4.1 Maximum ratings ............................................................................... 5 4.2 Thermal data ..................................................................................... 5 4.3 Electrical characteristics .................................................................... 6 5 Typical electrical characteristics.................................................. 10 6 Typical circuit ................................................................................ 13 7 Operation descriptions ................................................................. 14 7.1 Power section and gate driver ......................................................... 14 7.2 High voltage startup generator ........................................................ 14 7.3 Power-up and soft-startup ............................................................... 14 7.4 Power down operation .................................................................... 17 7.5 Auto restart operation ...................................................................... 17 7.6 Oscillator ......................................................................................... 17 7.7 Current mode conversion with adjustable current limit set point ..... 18 7.8 Overvoltage protection (OVP) ......................................................... 18 7.9 About CONT pin .............................................................................. 20 7.10 Feed-back and overload protection (OLP) ...................................... 20 7.11 Burst-mode operation at no load or very light load .......................... 23 7.12 Brown-out protection ....................................................................... 23 7.13 2nd level overcurrent protection and hiccup mode .......................... 25 8 Package information ..................................................................... 26 8.1 SO16 narrow package information .................................................. 26 8.2 DIP-7 package information .............................................................. 28 9 Revision history ............................................................................ 30 2/31 DocID14419 Rev 11

VIPER17 Block diagram 1 Block diagram Figure 2: Block diagram 2 Typical power Table 2: Typical power 230 VAC 85-265 VAC Part number Adapter (1) Open frame (2) Adapter (1) Open frame (2) 9 W 10 W 5 W 6 W Notes: (1)Typical continuous power in non ventilated enclosed adapter measured at 50 °C ambient. (2)Maximum practical continuous power in an open frame design at 50 °C ambient, with adequate heat sinking. DocID14419 Rev 11 3/31

Pin settings VIPER17 3 Pin settings Figure 3: Connection diagram (top view) The copper area for heat dissipation has to be designed under the DRAIN pins. Table 3: Pin description Pin n. Name Function DIP-7 SO16 This pin represents the device ground and the source of the power 1 1...2 GND section. Not available for user. This pin is mechanically connected to the - 4 N.A. controller die pad of the frame. In order to improve the noise immunity, is highly recommended connect it to GND (pin 1-2). Supply voltage of the control section. This pin also provides the charging 2 5 VDD current of the external capacitor during startup time. Control pin. The following functions can be selected: 1. current limit set point adjustment. The internal set default value of the cycle-by-cycle current limit can be reduced by connecting to ground an external resistor. 3 6 CONT 2. output voltage monitoring. A voltage exceeding VOVP threshold (see Table 8: "Controller section ") shuts the IC down reducing the device consumption. This function is strobed and digitally filtered for high noise immunity. Control input for duty cycle control. Internal current generator provides bias current for loop regulation. A voltage below the threshold VFBbm 4 7 FB activates the burst-mode operation. A level close to the threshold VFBlin means that we are approaching the cycle-by-cycle over-current set point. Brownout protection input with hysteresis. A voltage below the threshold VBRth shuts down (not latch) the device and lowers the power 5 10 BR consumption. Device operation restarts as the voltage exceeds the threshold VBRth + VBRhyst. It can be connected to ground when not used. High voltage drain pin. The built-in high voltage switched startup bias 7,8 13-16 DRAIN current is drawn from this pin too. Pins connected to the metal frame to facilitate heat dissipation. 4/31 DocID14419 Rev 11

VIPER17 Electrical data 4 Electrical data 4.1 Maximum ratings Table 4: Absolute maximum ratings Value Symbol Pin (DIP-7) Parameter Unit Min. Max. VDRAIN 7, 8 Drain-to-source (ground) voltage 800 V Repetitive avalanche energy EAV 7, 8 2 mJ (limited by TJ = 150 °C) Repetitive avalanche current IAR 7, 8 1 A (limited by TJ = 150 °C) IDRAIN 7, 8 Pulse drain current 2.5 A Control input pin voltage VCONT 3 -0.3 Self limited V (with ICONT = 1 mA) VFB 4 Feed-back voltage -0.3 5.5 V Brown-out input pin voltage VBR 5 -0.3 Self limited V (with IBR = 0.5 mA) VDD 2 Supply voltage (IDD = 25 mA) -0.3 Self limited V IDD 2 Input current 25 mA Power dissipation at TA < 40 °C (DIP-7) 1 W PTOT Power dissipation at TA < 60 °C (SO16N) 1 W TJ Operating junction temperature range -40 150 °C TSTG Storage temperature -55 150 °C ESD(HBM) 1 to 8 Human body model 4 kV ESD(CDM) 1 to 8 Charge device model 1.5 kV 4.2 Thermal data Table 5: Thermal data Max. value Max. value Symbol Parameter Unit SO16N DIP-7 Thermal resistance junction pin RthJP 35 40 °C/W (dissipated power = 1 W) Thermal resistance junction ambient RthJA 110 110 °C/W (dissipated power = 1 W) Thermal resistance junction ambient RthJA (dissipated power = 1 W) (1) 80 90 °C/W Notes: (1)When mounted on a standard single side FR4 board with 100 mm2 (0.155 sq in) of Cu (35 µm thick). DocID14419 Rev 11 5/31

Electrical data VIPER17 4.3 Electrical characteristics (T = -25 to 125 °C, V = 14 V)a J DD Table 6: Power section Symbol Parameter Test condition Min. Typ. Max. Unit IDRAIN = 1 mA VBVDSS Break-down voltage VFB = GND 800 V TJ = 25 °C VDRAIN = 640 V 60 µA VFB = GND IOFF OFF state drain current VDRAIN = 800 V 75 µA VFB = GND IDRAIN = 0.2 A, VFB = 3 V 20 24 Ω VBR = GND, TJ = 25 °C RDS(on) Drain-source on state resistance IDRAIN = 0.2 A VFB = 3 V 40 48 Ω VBR = GND TJ = 125 °C Effective (energy related) output COSS capacitance VDRAIN = 0 to 640 V 10 pF Table 7: Supply section Symbol Parameter Test condition Min. Typ. Max. Unit Voltage VDRAIN_START Drain-source start voltage 60 80 100 V VDRAIN = 120 V VBR = GND -2 -3 -4 mA VFB = GND VDD = 4 V IDDch Startup charging current VDRAIN = 120 V VBR = GND -0.4 -0.6 -0.8 mA VFB = GND VDD = 4 V after fault. VDD Operating voltage range After turn-on 8.5 23.5 V VDDclamp VDD clamp voltage IDD = 20 mA 23.5 V VDDon VDD startup threshold VDRAIN = 120 V 13 14 15 V VDDoff VthDrDe suhnodlde r voltage shutdown VVBFBR == GGNNDD 7.5 8 8.5 V VDRAIN = 120 V VDD(RESTART) VDD restart voltage threshold VBR = GND 4 4.5 5 V VFB = GND a Adjust VDD above VDDon startup threshold before settings to 14 V. 6/31 DocID14419 Rev 11

VIPER17 Electrical data Symbol Parameter Test condition Min. Typ. Max. Unit Current VFB = GND Operating supply current, not FSW = 0 kHz IDD0 switching VBR = GND, 0.9 mA VDD = 10 V VDRAIN = 120 V 1.8 mA FSW = 60 kHz IDD1 Operating supply current, switching VDRAIN = 120 V 2 mA FSW = 115 kHz Operating supply current, with IDD_FAULT protection tripping 400 µA Operating supply current with IDD_OFF VDD = 7 V 270 µA VDD < VDD_off Table 8: Controller section Symbol Parameter Test condition Min. Typ. Max. Unit Feed-back pin VFBolp Overload shut down threshold 4.5 4.8 5.2 V VFBlin Linear dynamics upper limit 3.2 3.3 3.4 V VFBbm Burst mode threshold Voltage falling 0.4 0.45 0.6 V VFBbmhys Burst mode hysteresis Voltage rising 50 mV VFB = 0.3 V -150 -200 -280 uA IFB Feed-back sourced current 3.3 V < VFB < 4.8 V -3 uA RFB(DYN) Dynamic resistance VFB < 3.3 V 12 19 kΩ HFB ΔVFB / ΔID 3 8 V/A CONT pin VCONT_l Low level clamp voltage ICONT = -100 µA 0.5 V VCONT_h High level clamp voltage ICONT = 1 mA 5 5.5 6 V Current limitation VFB = 4 V IDlim Max drain current limitation (1) ICONT = -10 µA 0.38 0.4 0.42 A TJ = 25 °C tSS Soft-start time 8.5 ms TON_MIN Minimum turn ON time 220 400 480 ns td Propagation delay (2) 100 ns tLEB Leading edge blanking (2) 300 ns Peak drain current during burst ID_BM mode VFB = 0.6 V 90 mA DocID14419 Rev 11 7/31

Electrical data VIPER17 Symbol Parameter Test condition Min. Typ. Max. Unit Oscillator section FOSC VVIIPPEERR1177LH VVDFBD == 1o pVe rating voltage range 15043 16105 16267 kkHHzz VIPER17L ±4 kHz FD Modulation depth VIPER17H ±8 kHz FM Modulation frequency 250 Hz DMAX Maximum duty cycle 70 80 % Overcurrent protection (2nd OCP) IDMAX Second over current threshold (2) 0.6 A Overvoltage protection VOVP Overvoltage protection threshold 2.7 3 3.3 V TSTROBE Overvoltage protection strobe time 2.2 µs Brown out protection VBRth Brown out threshold Voltage falling 0.41 0.45 0.49 V VBRhyst Voltage hysteresis above VBRth 50 mV IBRhyst Current hysteresis 7 12 µA VBRclamp Clamp voltage IBR = 250 µA 3 V VDIS Brown out disable voltage 50 150 mV Thermal shutdown TSD Thermal shutdown temperature (2) 150 160 °C THYST Thermal shutdown hysteresis (2) 30 °C Notes: (1)IDlim @ VDD lower than 10 V can range between -5 % and +15 %. (2)Specification assured by design, characterization and statistical correlation. 8/31 DocID14419 Rev 11

VIPER17 Electrical data Figure 4: Minimum turn-on time test circuit Figure 5: Brown out threshold test circuit Figure 6: OVP threshold test circuit Adjust V above V startup threshold before settings to 14 V. DD DDon DocID14419 Rev 11 9/31

Typical electrical characteristics VIPER17 5 Typical electrical characteristics Figure 7: Current limit vs TJ Figure 8: Switching frequency vs TJ Figure 9: Drain start voltage vs TJ Figure 10: HFB vs TJ Figure 11: Brown out threshold vs TJ Figure 12: Brown out hysteresis vs TJ 10/31 DocID14419 Rev 11

VIPER17 Typical electrical characteristics Figure 14: Operating supply current Figure 13: Brown out hysteresis current vs TJ (no switching) vs TJ Figure 16: Current limit vs RLIM Figure 15: Operating supply current (switching) vs TJ Figure 17: Power MOSFET on-resistance vs TJ Figure 18: Power MOSFET break down voltage vs TJ DocID14419 Rev 11 11/31

Typical electrical characteristics VIPER17 Figure 19: Thermal shutdown 12/31 DocID14419 Rev 11

VIPER17 Typical circuit 6 Typical circuit Figure 20: Min-features flyback application Figure 21: Full-features flyback application DocID14419 Rev 11 13/31

Operation descriptions VIPER17 7 Operation descriptions VIPER17 is a high-performance low-voltage PWM controller chip with an 800 V, avalanche rugged power section. The controller includes: the oscillator with jittering feature, the startup circuits with soft-start feature, the PWM logic, the current limit circuit with adjustable set point, the second over current circuit, the burst mode management, the brown-out circuit, the UVLO circuit, the auto-restart circuit and the thermal protection circuit. The current limit set-point is set by the CONT pin. The burst mode operation guaranties high performance in the stand-by mode and helps in the energy saving norm accomplishment. All the fault protections are built in auto restart mode with very low repetition rate to prevent IC's over heating. 7.1 Power section and gate driver The power section is implemented with an avalanche ruggedness N-channel MOSFET, which guarantees safe operation within the specified energy rating as well as high dv/dt capability. The power section has a BV of 800 V min. and a typical R of 20 Ω at DSS DS(on) 25 °C. The integrated SenseFET structure allows a virtually loss-less current sensing. The gate driver is designed to supply a controlled gate current during both turn-on and turn- off in order to minimize common mode EMI. Under UVLO conditions an internal pull-down circuit holds the gate low in order to ensure that the Power section cannot be turned on accidentally. 7.2 High voltage startup generator The HV current generator is supplied through the DRAIN pin and it is enabled only if the input bulk capacitor voltage is higher than V threshold, 80 V typically. When DRAIN_START DC the HV current generator is ON, the I current (3 mA typical value) is delivered to the DDch capacitor on the V pin. In case of auto restart mode after a fault event, the I current is DD DDch reduced to 0.6 mA, in order to have a slow duty cycle during the restart phase. 7.3 Power-up and soft-startup If the input voltage rises up till the device start threshold, V , the V voltage DRAIN_START DD begins to grow due to the I current (see Table 7: "Supply section ") coming from the DDch internal high voltage startup circuit. If the V voltage reaches V threshold (see Table 7: DD DDon "Supply section ") the power MOSFET starts switching and the HV current generator is turned OFF. See Figure 23: "Timing diagram: normal power-up and power-down sequences". The IC is powered by the energy stored in the capacitor on the VDD pin, C , until when VDD the self-supply circuit (typically an auxiliary winding of the transformer and a steering diode) develops a voltage high enough to sustain the operation. C capacitor must be sized enough to avoid fast discharge and keep the needed voltage VDD value higher than V threshold. In fact, a too low capacitance value could terminate the DDoff switching operation before the controller receives any energy from the auxiliary winding. 14/31 DocID14419 Rev 11

VIPER17 Operation descriptions The following formula can be used for the V capacitor calculation: DD Equation 1 𝐼 ×𝑡 𝐷𝐷𝑐ℎ 𝑆𝑆𝑎𝑢𝑥 𝐶 = 𝑉𝐷𝐷 𝑉 −𝑉 𝐷𝐷𝑜𝑛 𝐷𝐷𝑜𝑓𝑓 The t is the time needed for the steady state of the auxiliary voltage. This time is SSaux estimated by applicator according to the output stage configurations (transformer, output capacitances, etc.). During the converter startup time, the drain current limitation is progressively increased to the maximum value. In this way the stress on the secondary diode is considerably reduced. It also helps to prevent transformer saturation. The soft-start time lasts 8.5 ms and the feature is implemented for every attempt of startup converter or after a fault. Figure 22: IDD current during startup and burst mode DocID14419 Rev 11 15/31

Operation descriptions VIPER17 Figure 23: Timing diagram: normal power-up and power-down sequences Figure 24: Soft-start: timing diagram 16/31 DocID14419 Rev 11

VIPER17 Operation descriptions 7.4 Power down operation At converter power down, the system loses regulation as soon as the input voltage is so low that the peak current limitation is reached. The V voltage drops and when it falls DD below the V threshold (see Table 7: "Supply section ") the power MOSFET is switched DDoff OFF, the energy transfers to the IC interrupted and consequently the V voltages DD decreases, Figure 23: "Timing diagram: normal power-up and power-down sequences". Later, if the V is lower than V (see Table 7: "Supply section "), the startup IN DRAIN_START sequence is inhibited and the power down completed. This feature is useful to prevent converter’s restart attempts and ensures monotonic output voltage decay during the system power down. 7.5 Auto restart operation If after a converter power down, the V is higher than V the startup sequence is IN DRAIN_START, not inhibited and will be activated only when the V voltage drops down the V DD DD(RESTART) threshold (see Table 7: "Supply section "). This means that the HV startup current generator restarts the V capacitor charging only when the V voltage drops below DD DD V . The scenario above described is for instance a power down because of a fault DD(RESTART) condition. After a fault condition, the charging current, I , is 0.6 mA (typ.) instead of the 3 DDch mA (typ.) of a normal startup converter phase. This feature together with the low V threshold ensures that, after a fault, the restart attempts of the IC has a very DD(RESTART) long repetition rate and the converter works safely with extremely low power throughput. The Figure 25: "Timing diagram: behavior after short circuit" shows the IC behavioral after a short circuit event. Figure 25: Timing diagram: behavior after short circuit 7.6 Oscillator The switching frequency is internally fixed to 60 kHz or 115 kHz. In both case the switching frequency is modulated by approximately ±4 kHz (60 kHz version) or ±8 kHz (115 kHz version) at 250 Hz (typical) rate, so that the resulting spread-spectrum action distributes the energy of each harmonic of the switching frequency over a number of side-band harmonics having the same energy on the whole but smaller amplitudes. DocID14419 Rev 11 17/31

Operation descriptions VIPER17 7.7 Current mode conversion with adjustable current limit set point The device is a current mode converter: the drain current is sensed and converted in voltage that is applied to the non inverting pin of the PWM comparator. This voltage is compared with the one on the feed-back pin through a voltage divider on cycle by cycle basis.The VIPER17 has a default current limit value, I , that the designer can adjust DLIM according the electrical specification, by the R resistor connected to the CONT see LIM Figure 16: "Current limit vs RLIM". The CONT pin has a minimum current sunk needed to activate the I adjustment: without DLIM R or with high R (i.e. 100 KΩ) the current limit is fixed to the default value (see I , LIM LIM DLIM Table 8: "Controller section "). 7.8 Overvoltage protection (OVP) The VIPER17has integrated the logic for the monitor of the output voltage using as input signal the voltage V during the OFF time of the power MOSFET. This is the time when CONT the voltage from the auxiliary winding tracks the output voltage, through the turn ratio 𝑁𝐴𝑈𝑋 𝑁𝑆𝐸𝐶 The CONT pin has to be connected to the auxiliary winding through the diode D and the OVP resistors R and R as shows the Figure 27: "CONT pin configuration". When, during OVP LIM the OFF time, the voltage V exceeds, four consecutive times, the reference voltage CONT V (see Table 8: "Controller section ") the overvoltage protection will stop the power OVP MOSFET and the converter enters the auto-restart mode. In order to bypass the noise immediately after the turn off of the power MOSFET, the voltage V is sampled inside a short window after the time T , see Table 8: CONT STROBE "Controller section " and the Figure 26: "OVP timing diagram". The sampled signal, if higher than V , trigger the internal OVP digital signal and increments the internal counter. OVP The same counter is reset every time the signal OVP is not triggered in one oscillator cycle. Referring to the Figure 21: "Full-features flyback application", the resistors divider ratio k OVP will be given by: Equation 2 𝑉 𝑂𝑉𝑃 𝐾 = 𝑂𝑉𝑃 𝑁 𝐴𝑈𝑋∙(𝑉 +𝑉 )−𝑉 𝑁 𝑂𝑈𝑇𝑂𝑉𝑃 𝐷𝑆𝐸𝐶 𝐷𝐴𝑈𝑋 𝑆𝐸𝐶 Equation 3 𝑅 𝐿𝐼𝑀 𝐾 = 𝑂𝑉𝑃 𝑅 +𝑅 𝐿𝐼𝑀 𝑂𝑉𝑃 18/31 DocID14419 Rev 11

VIPER17 Operation descriptions Where: V is the OVP threshold (see Table 8: "Controller section ") OVP V is the converter output voltage value to activate the OVP (set by designer) OUT OVP N is the auxiliary winding turns AUX N is the secondary winding turns SEC V is the secondary diode forward voltage DSEC V is the auxiliary diode forward voltage DAUX R together R make the output voltage divider OVP LIM Than, fixed R according to the desired I , the R can be calculating by: LIM, DLIM OVP Equation 4 1−𝐾 𝑂𝑉𝑃 𝑅 =𝑅 × 𝑂𝑉𝑃 𝐿𝐼𝑀 𝐾 𝑂𝑉𝑃 The resistor values will be such that the current sourced and sunk by the CONT pin be within the rated capability of the internal clamp. Figure 26: OVP timing diagram DocID14419 Rev 11 19/31

Operation descriptions VIPER17 7.9 About CONT pin Referring to the Figure 27: "CONT pin configuration", through the CONT pin, the below features can be implemented: 1. Current Limit set point 2. Over voltage protection on the converter output voltage The Table 9: "CONT pin configurations" referring to the Figure 27: "CONT pin configuration", lists the external components needed to activate one or plus of the CONT pin functions. Figure 27: CONT pin configuration Table 9: CONT pin configurations Function / component RLIM (1) ROVP DAUX IDlim reduction See Figure 16: "Current limit vs RLIM" No No OVP ≥ 80 KΩ See Equation 4 Yes IDlim reduction + OVP See Figure 16: "Current limit vs RLIM" See Equation 4 Yes Notes: (1)RLIM has to be fixed before of ROVP. 7.10 Feed-back and overload protection (OLP) The VIPER17 is a current mode converter: the feedback pin controls the PWM operation, controls the burst mode and actives the overload protection. Figure 28: "FB pin configuration (minimal) " and Figure 29: " FB pin configuration ( two poles and one zero)" show the internal current mode structure. With the feedback pin voltage between V and V , see Table 8: "Controller section ", FBbm FBlin the drain current is sensed and converted in voltage that is applied to the non inverting pin of the PWM comparator. See Figure 2: "Block diagram". This voltage is compared with the one on the feedback pin through a voltage divider on cycle by cycle basis. When these two voltages are equal, the PWM logic orders the switch off of the power MOSFET. The drain current is always limited to I value. Dlim 20/31 DocID14419 Rev 11

VIPER17 Operation descriptions In case of overload the feedback pin increases in reaction to this event and when it goes higher than V , the PWM comparator is disabled and the drain current is limited to I by FBlin Dlim the OCP comparator, see Figure 2: "Block diagram". When the feedback pin voltage reaches the threshold V an internal current generator FBlin starts to charge the feedback capacitor (C ) and when the feedback voltage reaches the FB V threshold, the converter is turned off and the startup phase is activated with reduced FBolp value of I to 0.6 mA. See Table 7: "Supply section ". DDch During the first startup phase of the converter, after the soft-startup time, t , the output SS voltage could force the feedback pin voltage to rise up to the V threshold that switches FBolp off the converter itself. To avoid this event, the appropriate feedback network has to be selected according to the output load. More the network feedback fixes the compensation loop stability. The Figure 28: "FB pin configuration (minimal) " and Figure 29: " FB pin configuration ( two poles and one zero)" show the two different feedback networks. The time from the over load detection (V = V ) to the device shutdown (V = V ) FB FBlin FB FBolp can be calculating by C value (see Figure 28: "FB pin configuration (minimal) " and FB Figure 29: " FB pin configuration ( two poles and one zero)"), using the formula: Equation 5 𝑉 −𝑉 𝐹𝐵𝑜𝑙𝑝 𝐹𝐵𝑙𝑖𝑛 𝑇 −𝑑𝑒𝑙𝑎𝑦 =𝐶 × 𝑂𝐿𝑃 𝐹𝐵 3𝜇𝐴 In the Figure 28: "FB pin configuration (minimal) ", the capacitor connected to FB pin (C ) FB is used as part of the circuit to compensate the feedback loop but also as element to delay the OLP shut down owing to the time needed to charge the capacitor (see Equation 5). After the startup time, t , during which the feedback voltage is fixed at V , the output SS FBlin capacitor could not be at its nominal value and the controller interpreter this situation as an over load condition. In this case, the OLP delay helps to avoid an incorrect device shut down during the startup. Owing to the above considerations, the OLP delay time must be long enough to by-pass the initial output voltage transient and check the over load condition only when the output voltage is in steady state. The output transient time depends from the value of the output capacitor and from the load. When the value of the C capacitor calculated for the loop stability is too low and cannot FB ensure enough OLP delay, an alternative compensation network can be used and it is showed in Figure 29: " FB pin configuration ( two poles and one zero)". Using this alternative compensation network, two poles (f , f ) and one zero (f ) are PFB PFB1 ZFB introduced by the capacitors C and C and the resistor R . FB FB1 FB1 The capacitor C introduces a pole (f ) at higher frequency than f and f . This pole FB PFB ZB PFB1 is usually used to compensate the high frequency zero due to the ESR (Equivalent Series Resistor) of the output capacitance of the fly-back converter. The mathematical expressions of these poles and zero frequency, considering the scheme in Figure 29: " FB pin configuration ( two poles and one zero)" are reported by the equations below: Equation 6 1 𝑓 = 𝑍𝐹𝐵 2∙𝜋∙𝐶 ∙𝑅 𝐹𝐵1 𝐹𝐵1 DocID14419 Rev 11 21/31

Operation descriptions VIPER17 Equation 7 𝑅 +𝑅 𝐹𝐵(𝐷𝑌𝑁) 𝐹𝐵1 𝑓 = 𝑃𝐹𝐵1 2∙𝜋∙𝐶 ∙(𝑅 ∙𝑅 ) 𝐹𝐵 𝐹𝐵(𝐷𝑌𝑁) 𝐹𝐵1 Equation 8 1 𝑓 = 𝑃𝐹𝐵1 2∙𝜋∙𝐶 ∙(𝑅 +𝑅 ) 𝐹𝐵1 𝐹𝐵1 𝐹𝐵(𝐷𝑌𝑁) The R is the dynamic resistance seen by the FB pin. FB(DYN) The C capacitor fixes the OLP delay and usually C results much higher than C . The FB1 FB1 FB Equation 5 can be still used to calculate the OLP delay time but C has to be considered FB1 instead of C . Using the alternative compensation network, the designer can satisfy, in all FB case, the loop stability and the enough OLP delay time alike. Figure 28: FB pin configuration (minimal) Figure 29: FB pin configuration ( two poles and one zero) 22/31 DocID14419 Rev 11

VIPER17 Operation descriptions 7.11 Burst-mode operation at no load or very light load When the load decrease the feedback loop reacts lowering the feedback pin voltage. If it falls down the burst mode threshold, V , the power MOSFET is not more allowed to be FBbm switched on. After the MOSFET stops, as a result of the feedback reaction to the energy delivery stop, the feedback pin voltage increases and exceeding the level, V + V , FBbm FBbmhys the power MOSFET starts switching again. The burst mode thresholds are reported on Table 8: "Controller section " and Figure 30: "Burst mode timing diagram, light load management" shows this behavior. Systems alternates period of time where power MOSFET is switching to period of time where power MOSFET is not switching; this device working mode is the burst mode. The power delivered to output during switching periods exceeds the load power demands; the excess of power is balanced from not switching period where no power is processed. The advantage of burst mode operation is an average switching frequency much lower then the normal operation working frequency, up to some hundred of hertz, minimizing all frequency related losses. During the burst-mode the drain current peak is clamped to the level, I , reported on Table 8: "Controller section ". D_BM Figure 30: Burst mode timing diagram, light load management 7.12 Brown-out protection Brown-out protection is a not-latched shutdown function activated when a condition of mains under voltage is detected. The Brown-out comparator is internally referenced to V BRth threshold, see Table 8: "Controller section ", and disables the PWM if the voltage applied at the BR pin is below this internal reference. Under this condition the power MOSFET is turned off. Until the Brown out condition is present, the V voltage continuously oscillates DD between the V and the UVLO thresholds, as shown in the timing diagram of Figure 31: DDon "Brown-out protection: BR external setting and timing diagram". A voltage hysteresis is present to improve the noise immunity. The switching operation is restarted as the voltage on the pin is above the reference plus the before said voltage hysteresis. See Figure 5: "Brown out threshold test circuit". The Brown-out comparator is provided also with a current hysteresis, I . The designer BRhyst has to set the rectified input voltage above which the power MOSFET starts switching after brown out event, V , and the rectified input voltage below which the power MOSFET is INon switched off, V . Thanks to the I , see Table 8: "Controller section ", these two INoff BRhyst thresholds can be set separately. DocID14419 Rev 11 23/31

Operation descriptions VIPER17 Figure 31: Brown-out protection: BR external setting and timing diagram Fixed the V and the V levels, with reference to Figure 31: "Brown-out protection: BR INon INoff external setting and timing diagram", the following relationships can be established for the calculation of the resistors R and R : H L Equation 9 𝑉 𝑉 −𝑉 −𝑉 𝑉 𝐵𝑅ℎ𝑦𝑠𝑡 𝐼𝑁𝑜𝑛 𝐼𝑁𝑜𝑓𝑓 𝐵𝑅ℎ𝑦𝑠𝑡 𝐵𝑅𝑡ℎ 𝑅 = + × 𝐿 𝐼 𝑉 −𝑉 𝐼 𝐵𝑅ℎ𝑦𝑠𝑡 𝐼𝑁𝑜𝑓𝑓 𝐵𝑅𝑡ℎ 𝐵𝑅ℎ𝑦𝑠𝑡 Equation 10 𝑉 −𝑉 −𝑉 𝑅 𝐼𝑁𝑜𝑛 𝐼𝑁𝑜𝑓𝑓 𝐵𝑅ℎ𝑦𝑠𝑡 𝐿 𝑅 = × 𝐻 𝐼 𝑉 𝐵𝑅ℎ𝑦𝑠𝑡 𝑅 + 𝐵𝑅ℎ𝑦𝑠𝑡 𝐿 𝐼 𝐵𝑅ℎ𝑦𝑠𝑡 For a proper operation of this function, V must be less than the peak voltage at IN on minimum mains and V less than the minimum voltage on the input bulk capacitor at IN off minimum mains and maximum load. The BR pin is a high impedance input connected to high value resistors, thus it is prone to pick up noise, which might alter the OFF threshold when the converter operates or gives origin to undesired switch-off of the device during ESD tests. It is possible to bypass the pin to ground with a small film capacitor (e.g. 1-10 nF) to prevent any malfunctioning of this kind. If the brown-out function is not used the BR pin has to be connected to GND, ensuring that the voltage is lower than the minimum of V threshold (50 mV, see Table 8: "Controller DIS section "). In order to enable the brown-out function the BR pin voltage has to be higher than the maximum of V threshold (150 mV, see Table 8: "Controller section "). DIS 24/31 DocID14419 Rev 11

VIPER17 Operation descriptions 7.13 2nd level overcurrent protection and hiccup mode The VIPER17 is protected against short circuit of the secondary rectifier, short circuit on the secondary winding or a hard-saturation of fly-back transformer. Such as anomalous condition is invoked when the drain current exceed the threshold I (see Table 8: DMAX "Controller section "). To distinguish a real malfunction from a disturbance (e.g. induced during ESD tests) a “warning state” is entered after the first signal trip. If in the subsequent switching cycle the signal is not tripped, a temporary disturbance is assumed and the protection logic will be reset in its idle state; otherwise if the I threshold is exceeded for two consecutive DMAX switching cycles a real malfunction is assumed and the power MOSFET is turned OFF. The shutdown condition is latched as long as the device is supplied. While it is disabled, no energy is transferred from the auxiliary winding; hence the voltage on the V capacitor DD decays till the V under voltage threshold (V ), which clears the latch. DD DDoff The startup HV current generator is still off, until V voltage goes below its restart voltage, DD V . After this condition the V capacitor is charged again by 600 µA current, and DD(RESTART) DD the converter switching restarts if the V occurs. If the fault condition is not removed the DDon device enters in auto-restart mode. This behavioral results in a low-frequency intermittent operation (Hiccup-mode operation), with very low stress on the power circuit. See the timing diagram of Figure 32: "Hiccup-mode OCP: timing diagram". Figure 32: Hiccup-mode OCP: timing diagram DocID14419 Rev 11 25/31

Package information VIPER17 8 Package information In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark. 8.1 SO16 narrow package information Figure 33: SO16 narrow package outline 26/31 DocID14419 Rev 11

VIPER17 Package information Table 10: SO16 narrow mechanical data mm Dim. Min. Typ. Max. A 1.75 A1 0.1 0.25 A2 1.25 b 0.31 0.51 c 0.17 0.25 D 9.8 9.9 10 E 5.8 6 6.2 E1 3.8 3.9 4 e 1.27 h 0.25 0.5 L 0.4 1.27 k 0 8 ccc 0.1 DocID14419 Rev 11 27/31

Package information VIPER17 8.2 DIP-7 package information Figure 34: DIP-7 package outline 28/31 DocID14419 Rev 11

VIPER17 Package information Table 11: DIP-7 package mechanical data Dim. mm Notes Min. Typ. Max. A 5.33 A1 0.38 A2 2.92 3.30 4.95 b 0.36 0.46 0.56 b2 1.14 1.52 1.78 c 0.20 0.25 0.36 D 9.02 9.27 10.16 E 7.62 7.87 8.26 E1 6.10 6.35 7.11 e 2.54 eA 7.62 eB 10.92 L 2.92 3.30 3.81 M(1)(2) 2.508 6 - 8 N 0.40 0.50 0.60 N1 0.60 O(2)(3) 0.548 7 - 8 Notes: (1) Creepage distance > 800 V. (2) Creepage distance as shown in the 664-1 CEI / IEC standard. (3) Creepage distance 250 V. General package performance The leads size is comprehensive of the thickness of the leads finishing material. Dimensions do not include mold protrusion, not to exceed 0,25 mm in total (both side). Package outline exclusive of metal burrs dimensions. Datum plane “H” coincident with the bottom of lead, where lead exits body. Ref. POA MOTHER doc. 0037880. DocID14419 Rev 11 29/31

Revision history VIPER17 9 Revision history Table 12: Document revision history Date Revision Changes 14-Feb-2008 1 Initial release 19-Feb-2008 2 Updated: Figure 1 on page 1, Figure 3 on page 4 21-Jul-2008 3 Added new SO16 package 30-Sep-2008 4 Updated Equation 9, Equation 10 16-Jan-2009 5 Updated Chapter 7.13 on page 27 Updated application paragraph in coverpage and Table 8 on page 20-Jul-2009 6 8 14-Jun-2010 7 Updated Figure 3 on page 4 and Table 3 on page 4 Updated Table 8: Controller section. 23-Jul-2013 8 Minor text changes. 30-Aug-2013 9 Modified the footnote in Table 8: Controller section. Modified the title and the features in cover page. Updated Section 3: Pin settings, Section 4.1: Maximum ratings, 20-May-2014 10 Section 4.3: Electrical characteristics. Minor text changes. Updated Table 5: "Thermal data", Table 7: "Supply section " and 16-Feb-2017 11 Table 8: "Controller section ". Minor text changes. 30/31 DocID14419 Rev 11

VIPER17 IMPORTANT NOTICE – PLEASE READ CAREFULLY STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST’s terms and conditions of sale in place at the time of order acknowledgement. Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers’ products. No license, express or implied, to any intellectual property right is granted by ST herein. Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product. ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners. Information in this document supersedes and replaces information previously supplied in any prior versions of this document. © 2017 STMicroelectronics – All rights reserved DocID14419 Rev 11 31/31

Mouser Electronics Authorized Distributor Click to View Pricing, Inventory, Delivery & Lifecycle Information: S TMicroelectronics: VIPER17HN VIPER17LN VIPER17HDTR VIPER17LDTR VIPER17HD VIPER17LD

Datasheet下载

Datasheet下载