ICGOO在线商城 > 射频/IF 和 RFID > RFID,RF 接入,监控 IC > TRF7970ARHBT

- 型号: TRF7970ARHBT

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

TRF7970ARHBT产品简介:

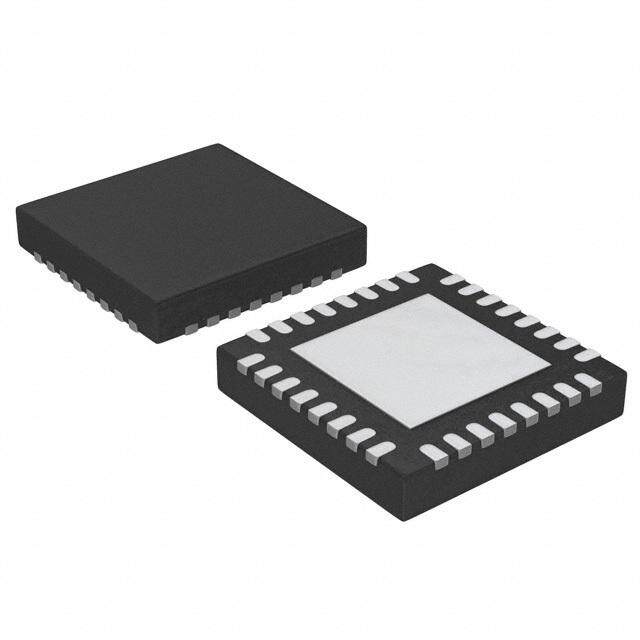

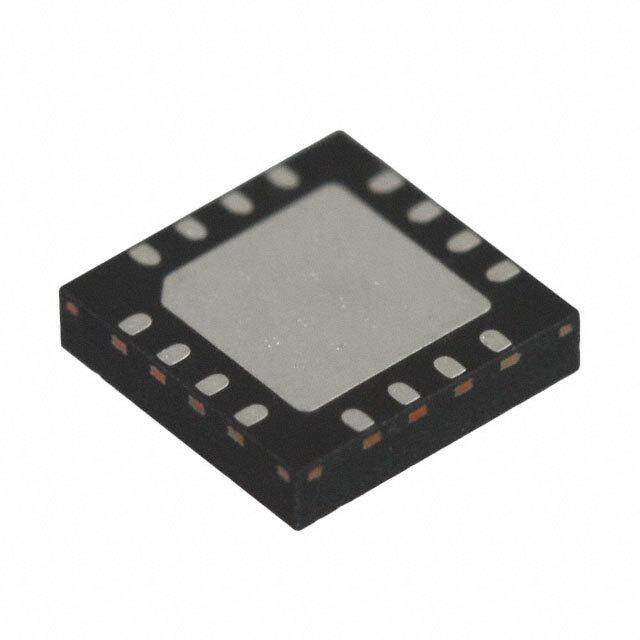

ICGOO电子元器件商城为您提供TRF7970ARHBT由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 TRF7970ARHBT价格参考¥47.57-¥69.52。Texas InstrumentsTRF7970ARHBT封装/规格:RFID,RF 接入,监控 IC, RFID Reader/Transponder IC 13.56MHz ISO 14443, ISO 15693, ISO 18000-3 SPI 2.7V ~ 5.5V 32-VFQFN Exposed Pad。您可以下载TRF7970ARHBT参考资料、Datasheet数据手册功能说明书,资料中有TRF7970ARHBT 详细功能的应用电路图电压和使用方法及教程。

TRF7970ARHBT是德州仪器(Texas Instruments)推出的一款高度集成的多协议RFID和近场通信(NFC)收发器芯片,属于RFID、RF接入及监控IC类别。该芯片支持ISO/IEC 14443A/B、ISO/IEC 15693、Felica以及NFC Forum标准,适用于13.56MHz高频RFID系统。 其典型应用场景包括:智能门禁系统、公共交通票务系统(如公交卡、地铁卡读写器)、便携式支付终端(POS)、工业自动化设备的身份识别模块、医疗设备中的患者信息管理、电子产品中的安全认证与数据交换,以及智能家居中的NFC配对功能等。此外,TRF7970ARHBT还可用于资产跟踪、文档安全管理及消费类电子产品的无线配置连接。 该芯片采用小型化RHBT封装,具备低功耗特性,适合电池供电设备;同时支持SPI和I2C接口,便于与主控MCU连接,具备良好的系统集成性。其内置的模拟前端和自动防冲突功能提升了通信可靠性,广泛应用于需要非接触式数据传输和身份识别的中高端嵌入式系统中。

| 参数 | 数值 |

| 产品目录 | |

| 描述 | IC RFID/NFC AFE 13.56MHZ 32QFNRFID应答器 Fully Int 13.56MHz RFID/NFC Xcvr |

| DevelopmentKit | TRF7970AEVM |

| 产品分类 | RFID IC集成电路 - IC |

| 品牌 | Texas Instruments |

| 产品手册 | http://www.ti.com/litv/slos743k |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | RF集成电路,RFID应答器,Texas Instruments TRF7970ARHBT- |

| 数据手册 | |

| 产品型号 | TRF7970ARHBT |

| RF类型 | NFC,FeliCa |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=30386http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=30389 |

| 产品种类 | RFID应答器 |

| 供应商器件封装 | 32-VQFN(5x5) |

| 其它名称 | 296-29476-1 |

| 制造商产品页 | http://www.ti.com/general/docs/suppproductinfo.tsp?distId=10&orderablePartNumber=TRF7970ARHBT |

| 包装 | 剪切带 (CT) |

| 参考设计库 | http://www.digikey.com/rdl/4294959884/4294959883/799 |

| 商标 | Texas Instruments |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | 32-VFQFN 裸露焊盘 |

| 封装/箱体 | VQFN-32 |

| 工作温度范围 | - 40 C to + 110 C |

| 工厂包装数量 | 250 |

| 最大工作温度 | + 110 C |

| 最小工作温度 | - 40 C |

| 标准包装 | 1 |

| 特性 | ISO14443-A,ISO14443-B,ISO15693,ISO18000-3 |

| 系列 | TRF7970A |

| 配用 | /product-detail/zh/TRF7970AEVM/296-29475-ND/2745223 |

| 频率 | 13.56MHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Product Order Technical Tools & Support & Reference Folder Now Documents Software Community Design TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 TRF7970A Multiprotocol Fully Integrated 13.56-MHz RFID and Near Field Communication (NFC) Transceiver IC 1 Device Overview 1.1 Features 1 • SupportsNearFieldCommunication(NFC) • ProgrammableOutputPower:+20dBm(100mW), StandardsNFCIP-1(ISO/IEC18092)andNFCIP‑2 +23dBm(200mW) (ISO/IEC21481) • ProgrammableI/OVoltageLevelsFrom1.8VDC • CompletelyIntegratedProtocolHandlingfor to5.5VDC ISO/IEC15693,ISO/IEC18000-3,ISO/IEC14443 • ProgrammableSystemClockFrequencyOutput AandB,andFeliCa™ (RF,RF/2,RF/4)from13.56-MHzor27.12-MHz • IntegratedEncoders,Decoders,andDataFraming CrystalorOscillator forNFCInitiator,ActiveandPassiveTarget • IntegratedVoltageRegulatorOutputforOther OperationforAllThreeBitRates(106kbps, SystemComponents(MCU,Peripherals, 212kbps,424kbps),andCardEmulation Indicators),20mA(Max) • RFFieldDetectorWithProgrammableWake-up • ProgrammableModulationDepth LevelsforNFCPassiveTransponderEmulation • DualReceiverArchitectureWithRSSIfor Operation Eliminationof"ReadHoles"andAdjacentReader • RFFieldDetectorforNFCPhysicalCollision SystemorAmbientIn-BandNoiseDetection Avoidance • ProgrammablePowerModesforUltraLow-Power • IntegratedStateMachineforISO/IEC14443A SystemDesign(PowerDown<1µA) Anticollision(BrokenBytes)Operation • ParallelorSPIInterface(With127-ByteFIFO) (TransponderEmulationorNFCPassiveTarget) • TemperatureRange:–40°Cto110°C • InputVoltageRange:2.7VDCto5.5VDC • 32-PinQFNPackage(5mm× 5mm) 1.2 Applications • MobileDevices(Tablets,Handsets) • Short-RangeWirelessCommunicationTasks • SecurePairing(Bluetooth®,Wi-Fi®,OtherPaired (FirmwareUpdates) WirelessNetworks) • ProductIdentificationorAuthentication • PublicTransportorEventTicketing • MedicalEquipmentorConsumables • PassportorPayment(POS)ReaderSystems • AccessControl,DigitalDoorLocks • SharingofElectronicBusinessCards 1.3 Description The TRF7970A device is an integrated analog front end (AFE) and multiprotocol data-framing device for a 13.56-MHz NFC/RFIDsystemsupportingallthreeNFCoperationmodes – reader/writer,peer-to-peer,and card emulation according to ISO/IEC 14443 A and B, Sony FeliCa, ISO/IEC 15693, NFCIP-1 (ISO/IEC 18092), and NFCIP-2 (ISO/IEC 21481). Built-in programming options make the device suitable forawiderangeofapplicationsforNFC,proximity,andvicinityidentificationsystems. The device is configured by selecting the desired protocol in the control registers. Direct access to all controlregistersallowsfinetuningofvariousreaderparametersasneeded. The TRF7970A device supports data rates up to 848 kbps with all framing and synchronization tasks for the ISO protocols onboard. The TRF7970A device also supports reader and writer mode for NFC Forum tag types 1, 2, 3, 4, and 5. Other standards and even custom protocols can be implemented by using one of the direct modes the device offers. These direct modes let the user fully control the AFE and also gain access to the raw subcarrier data or the unframed, but already ISO-formatted, data and the associated (extracted)clocksignal. 1 An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectualpropertymattersandotherimportantdisclaimers.PRODUCTIONDATA.

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com The receiver system has a dual-input receiver architecture to maximize communication robustness. The receivers also include various automatic and manual gain control options. The received signal strength fromtransponders,ambientsources,orinternallevelsisavailableintheRSSIregister. A SPI or parallel interface can be used for the communication between the MCU and the TRF7970A device. When the built-in hardware encoders and decoders are used, transmit and receive functions use a 127-byte FIFO register. For direct transmit or receive functions, the encoders or decoders can be bypassedsotheMCUcanprocessthedatainrealtime. The TRF7970A device supports a wide supply voltage range of 2.7 V to 5.5 V and data communication levelsfrom1.8Vto5.5VfortheMCUI/Ointerface. The transmitter has selectable output power levels of 100 mW (+20 dBm) or 200 mW (+23 dBm) equivalent into a 50-Ω load when using a 5-V supply and supports OOK and ASK modulation with selectablemodulationdepth. The built-in programmable auxiliary voltage regulator delivers up to 20 mA to supply an MCU and additionalexternalcircuitswithinthereadersystem. Integrated RF field detector with programmable wake-up levels, eight selectable power modes, and ultra- lowpoweroperationenableeasydevelopmentofrobustandcost-efficientdesignsforlongbatterylife. Start evaluating the TRF7970A multiprotocol transceiver IC with the TRF7970AEVM, TRF7970ATB, or DLP-7970ABP. DeviceInformation PARTNUMBER PACKAGE BODYSIZE TRF7970ARHB VQFN(32) 5mm×5mm 2 DeviceOverview Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 1.4 Functional Block Diagram Figure1-1showstheblockdiagram. VDD_I/O RX_IN1 MUX PAhmapsleituadned Gain (RASUSXI) Logic I/O_0 Detector State I/O_1 RF Level Control Detector Logic I/O_2 RX_IN2 RSSI (Control I/O_3 (External) Registersand Phaseand (RMSaSinI) CoLmogmica)nd Level II//OO__45 Amplitude Gain Sh Detector anFdilAteGrC Digitizer MCU ifter I/O_6 VDD_PA Interface I/O_7 ISO Protocol Decoder IRQ Handling SYS_CLK TX_OUT Transmitter Framing Bit 127-Byte Analog Front End Framing FIFO DATA_CLK VIN Serial Conversion VDD_A VSS_PA CRC and Parity BAND_GAP EN VSS_A EN2 Digital Control VDD_RF ASK/OOK State Machine MOD Voltage SupplyRegulator Systems VSS_RF (SupplyRegulatorsand ReferenceVoltages) VDD_X OSC_IN VSS Crystal or Oscillator OSC_OUT Timing System VSS_D Copyright © 2017,Texas Instruments Incorporated Figure1-1.BlockDiagram Copyright©2011–2017,TexasInstrumentsIncorporated DeviceOverview 3 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com Table of Contents 1 DeviceOverview......................................... 1 6.8 Transmitter–DigitalSection........................ 30 1.1 Features.............................................. 1 6.9 Transmitter–ExternalPowerAmplifierand ................................. ........................................... Subcarrier Detector 31 1.2 Applications 1 ............ ............................................ 6.10 TRF7970AICCommunicationInterface 31 1.3 Description 1 ............................. ............................ 6.11 TRF7970AInitialization 49 1.4 FunctionalBlockDiagram 3 2 Revision History......................................... 5 6.12 SpecialDirectModeforImprovedMIFARE™ ......................................... Compatibility 50 3 DeviceCharacteristics.................................. 7 .......................................... 6.13 NFCModes 50 ..................................... 3.1 RelatedProducts 7 ............ 6.14 DirectCommandsfromMCUtoReader 52 4 TerminalConfigurationandFunctions.............. 8 ................................. 6.15 RegisterDescription 56 .......................................... 4.1 PinDiagram 8 7 Applications,Implementation,andLayout........ 76 ................................... 4.2 SignalDescriptions 8 7.1 TRF7970AReaderSystemUsingSPIWithSS 5 Specifications........................................... 10 Mode................................................ 76 5.1 AbsoluteMaximumRatings ........................ 10 7.2 Layout Considerations.............................. 77 5.2 ESDRatings........................................ 10 7.3 ImpedanceMatchingTX_Out(Pin5)to50Ω...... 77 5.3 RecommendedOperatingConditions............... 10 7.4 ReaderAntennaDesignGuidelines ................ 78 5.4 ElectricalCharacteristics............................ 11 8 DeviceandDocumentationSupport............... 79 5.5 ThermalResistanceCharacteristics................ 12 8.1 GettingStartedandNextSteps..................... 79 5.6 Switching Characteristics........................... 12 8.2 Device Nomenclature............................... 79 6 DetailedDescription................................... 13 8.3 ToolsandSoftware................................. 80 6.1 Overview............................................ 13 8.4 DocumentationSupport............................. 80 6.2 SystemBlockDiagram.............................. 16 8.5 CommunityResources.............................. 81 6.3 PowerSupplies...................................... 16 8.6 Trademarks.......................................... 81 6.4 Receiver–AnalogSection.......................... 22 8.7 ElectrostaticDischargeCaution..................... 81 6.5 Receiver–DigitalSection........................... 23 8.8 Glossary............................................. 81 ................................... 6.6 OscillatorSection 28 9 Mechanical,Packaging,andOrderable 6.7 Transmitter–AnalogSection....................... 29 Information.............................................. 82 4 TableofContents Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 2 Revision History NOTE:Pagenumbersforpreviousrevisionsmaydifferfrompagenumbersinthecurrentversion. ChangesfromApril18,2014toMarch27,2017 Page • CorrectedthedesignationofISO/IECstandardsthroughoutdocument;forexample,changedISO14443to ISO/IEC14443........................................................................................................................ 1 • ChangedthecontentsofSection1.3,Description............................................................................... 1 • AddedSection3.1,RelatedProducts ............................................................................................. 7 • MovedT fromSection5.2toSection5.1,AbsoluteMaximumRatings.................................................. 10 STG • MovedSection5.2andchangedtitlefromHandlingRatingstoESDRatings.............................................. 10 • AddedV andV toSection5.4,ElectricalCharacteristics ................................................................ 11 OL OH • ChangedtheTYPvalueofthef parameterfrom8to4MHzinSection5.4,ElectricalCharacteristics ....... 11 D_CLKmax • Throughoutdocument,removedsupportforapplicationcontrolofAutomaticGainControl(AGC)andReceiver GainAdjust,becausethesefeaturesweredesignedfortestfunctionalityandnotforproductionuse.................. 13 • AddedNFCType5tagstosupportedlistinSection6.1.1,RFIDandNFCOperation–ReaderandWriter........... 13 • Removedtheparagraphthatstarted"Thedesiredsystemofoperation(bitrate)isachievedby..."from Section6.1.2,NFCDeviceOperation–Initiator................................................................................ 14 • Removedtheparagraphthatstarted"Thedesiredsystemofoperation(bitrate)isachievedby..."from Section6.1.3,NFCDeviceOperation–Target................................................................................. 14 • Throughoutdocument,changed"tag"emulationoremulatorto"card"emulationoremulator........................... 14 • Addedthesentencethatstarts"Forinteroperabilitypurposes,TIrecommends..."inthefirstbulletedlistitemin Section6.1.3,NFCDeviceOperation–Target................................................................................. 15 • ChangedPOLLINGtoSENSF_REQinthebulletedlistitemthatstarts"Ifthefirstcommandisa SENSF_REQ..."anddeletedthesentencethatstarted"ThePOLLINGresponseissentin..."inSection6.1.3, NFCDeviceOperation–Target................................................................................................... 15 • Updatedthebulletedlistitemthatstarts"IfthefirstcommandisATR_REQ..."inSection6.1.3,NFCDevice Operation–Target ................................................................................................................. 15 • Changed"codedasISO14443"to"SENSB_REQ"inthebulletedlistitemthatstarts"Ifthefirstcommandisa SENSB_REQ..."inSection6.1.3,NFCDeviceOperation–Target.......................................................... 15 • Changed"FeliCa"to"peer-to-peer"inSection6.1.3.1,ActiveTarget,andSection6.1.3.2,PassiveTarget........... 15 • Updatedtheparagraphthatstarts"ThetransmissionofaresponsemustoccurafterRFcollisionavoidance..."in Section6.1.3.1,ActiveTarget .................................................................................................... 15 • Updatedtheparagraphthatstarts"Thetransmitsysteminpassivetargetmode..."inSection6.1.3.2,Passive Target................................................................................................................................. 15 • UpdatedthedescriptioninSection6.1.3.3,CardEmulation.................................................................. 16 • Addedthesentencethatstarts"ForapplicationsinwhichtheTRF7970Amaybesubjected..."inthesecond paragraphofSection6.3,PowerSupplies....................................................................................... 16 • ChangedV toV inthelastsentencethatreads"TheV outputcurrentshouldnotexceed20mA."in DD_A DD_X DD_X theNOTEinAnalogSupplyRegulator:V ................................................................................... 17 DD_A • Removedtheparagraphthatstarted"TheRFpoweramplifierregulator..."fromDigitalSupplyRegulator:V .... 17 DD_X • Changed250mVto400mVin"...a"DeltaVoltage"of400mVbelowV ...".............................................. 17 IN • Addedtheparagraphthatstarts"AsV isincreased,thesystem..."inSection6.3.2,SupplyRegulator DD_RF Settings .............................................................................................................................. 19 • Removedtheparagraphsthatstarted"Themainreceiveralsohas..."and"Bydefault,theAGCwindow comparator..."fromSection6.4.2,ReceiverGainandFilterStages ........................................................ 22 • ChangedTable6-5tomatchTable6-37......................................................................................... 23 • UpdatedSection6.5,Receiver–DigitalSection,toclarifyandremoveduplicatecontent................................ 23 • UpdatedthedescriptioninSection6.5.1.2,ExternalRSSI.................................................................... 27 • Removed"EquivalentSeriesResistance"fromTable6-9,MinimumCrystalRecommendations........................ 29 • Removedmentionof3-wireSPIandreplaced"IRQ"with"SlaveSelect"inthefirstparagraphofSection6.10.1, GeneralIntroduction................................................................................................................ 31 • UpdatedthedescriptionofFIFOlevelinterruptsinSection6.10.1.4,FIFOOperation.................................... 35 • Added"butrecommended"to"ItisoptionalbutrecommendedtoreadtheFIFOStatusregister..."in Section6.10.3,ReceptionofAirInterfaceData................................................................................. 37 • ChangedthetitleofSection6.10.4,DataTransmissionFromMCUtoTRF7970A........................................ 38 • Removedthesentencethatstarted"Thechoiceofoneofthesemodesoveranother..."fromSection6.10.5, SerialInterfaceCommunication(SPI)............................................................................................ 38 • Updatedtheparagraphthatstarts"TIrecommendsresettingtheFIFOafterreceivingdata..."in Copyright©2011–2017,TexasInstrumentsIncorporated RevisionHistory 5 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com Section6.10.5.1,SerialInterfaceModeWithSlaveSelect(SS).............................................................. 43 • AddedtheNOTEthatstarts"Anadditionaldirectmode..."inSection6.10.6,DirectMode............................... 44 • AddedSection6.11,TRF7970AInitialization ................................................................................... 49 • ChangedtheapplicationreportthatisreferencedinSection6.12,SpecialDirectModeforImprovedMIFARE™ Compatibility......................................................................................................................... 50 • ChangedPOLLINGtoSENSF_REQandupdateddescriptioninthelistitemthatstarts"Ifthefirstcommandisa SENSF_REQ..."..................................................................................................................... 51 • Updatedthedescriptioninthelistitemthatstarts"IfthefirstcommandisATR_REQ..."................................. 51 • CorrecteddescriptionofB1Irq_colinTable6-18,IRQStatusRegister(0x0C)forNFCandCardEmulation Operation:changedfrom"(asdefinedinregister0x01)"to"(asdefinedinregister0x10)" .............................. 52 • RemovedmentionofcollisionavoidancecommandsfromSection6.13.2,Initiator........................................ 52 • AddedandupdatedcommentsinTable6-19,AddressandCommandWordBitDistribution............................ 52 • Removedcommandcode0x15,CloseSlotSequence,fromTable6-19,AddressandCommandWordBit Distribution .......................................................................................................................... 52 • Addedthesentencethatstarts"ThiscommandshouldbesentafteraSoftwareInitializationcommand..."in Section6.14.1.1,Idle(0x00)....................................................................................................... 53 • ChangedthedescriptioninSection6.14.1.3,InitialRFCollisionAvoidance(0x04)....................................... 54 • ChangedthedescriptioninSection6.14.1.4,ResponseRFCollisionAvoidance(0x05)................................. 54 • ChangedthedescriptioninSection6.14.1.5,ResponseRFCollisionAvoidance(0x06,n=0)......................... 54 • Added"ThisisusedbytheISO/IEC15693protocol"toSection6.14.1.11,TransmitNextTimeSlot(0x14).......... 55 • CorrecteddescriptionofB1Irq_colinTable6-43,IRQStatusRegister(0x0C):changedfrom"(asdefinedin register0x01)"to"(asdefinedinregister0x10)" ............................................................................... 67 • ChangedthedescriptionofB5:B3inTable6-47from"...AuxiliaryRSSIrepresentsthesignallevelatRX_IN2"to "...AuxiliaryRSSIrepresentsthesignallevelatRX_IN1"...................................................................... 69 • RemovedformerSection7.1,TRF7970AReaderSystemUsingParallelMicrocontrollerInterface..................... 76 • ChangedFigure7-1,ApplicationSchematic–SPIWithSSModeMCUInterface ........................................ 76 • UpdatedthedescriptioninSection7.1.2,Schematic .......................................................................... 76 • AddedSection8.1,GettingStartedandNextSteps ........................................................................... 79 • AddedSection8.2,DeviceNomenclature....................................................................................... 79 • AddedSection8.3,ToolsandSoftware.......................................................................................... 80 • UpdatedSection8.4,DocumentationSupport.................................................................................. 80 6 RevisionHistory Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 3 Device Characteristics Table3-1liststhesupportedmodesofoperationforthe TRF7970Adevice. Table3-1.SupportedModesofOperation P2PINITIATORORREADER/WRITER CARDEMULATION P2PTARGET BITRATE BITRATE BITRATE TECHNOLOGY TECHNOLOGY TECHNOLOGY (kbps) (kbps) (kbps) NFC-AandNFC-B 106,212,424, (ISO/IEC14443AandB) 848(1) NFC-A,NFC-B 106 NFC-A 106 NFC-F(JIS:X6319-4) 212,424 N/A N/A NFC-F 212,424 NFC-V(ISO/IEC15693) 6.7,26.7 N/A N/A N/A N/A (1) 848kbpsappliestoreader/writermodeonly. 3.1 Related Products Forinformationaboutotherdevicesinthisfamilyofproductsorrelatedproducts,seethefollowinglinks. ProductsforTIWirelessConnectivity Connect more with the industry’s broadest wireless connectivity portfolio. ProductsforNFC/RFID TI provides one of the industry’s most differentiated NFC and RFID product portfolios and is your solution to meet a broad range of NFC connectivity and RFID identificationneeds. CompanionProductsforTRF7970A Review products that are frequently purchased or used with this product. ReferenceDesignsforTRF7970A The TI Designs Reference Design Library is a robust reference design library that spans analog, embedded processor, and connectivity. Created by TI experts to help you jump start your system design, all TI Designs include schematic or block diagrams, BOMs, and design files to speed your time to market. Search and download designsat ti.com/tidesigns. Copyright©2011–2017,TexasInstrumentsIncorporated DeviceCharacteristics 7 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com 4 Terminal Configuration and Functions 4.1 Pin Diagram Figure4-1showsthepinoutforthe32-pinRHBpackage. VDD_X OSC_IN OSC_OUT VSS_D EN SYS_CLK DATA_CLK EN2 32 31 30 29 28 27 26 25 VDD_A 1 24 I/O_7 VIN 2 23 I/O_6 VDD_RF 3 22 I/O_5 VDD_PA 4 21 I/O_4 Pad TX_OUT 5 20 I/O_3 VSS_PA 6 19 I/O_2 VSS_RX 7 18 I/O_1 RX_IN1 8 17 I/O_0 9 10 11 12 13 14 15 16 RX_IN2 VSS BG ASK/OO IRQ MOD VSS_A VDD_I/O K Figure4-1.32-PinRHBPackage(TopView) 4.2 Signal Descriptions Table4-1describesthesignals. Table4-1.TerminalFunctions TERMINAL TYPE (1) DESCRIPTION NAME NO. V 1 OUT Internalregulatedsupply(2.7Vto3.4V)foranalogcircuitry DD_A V 2 SUP Externalsupplyinputtochip(2.7Vto5.5V) IN V 3 OUT Internalregulatedsupply(2.7Vto5V),normallyconnectedtoV (pin4) DD_RF DD_PA V 4 INP SupplyforPA;normallyconnectedexternallytoV (pin3) DD_PA DD_RF TX_OUT 5 OUT RFoutput(selectableoutputpower,100mWor200mW,withV =5V) DD V 6 SUP NegativesupplyforPA;normallyconnectedtocircuitground SS_PA V 7 SUP NegativesupplyforRXinputs;normallyconnectedtocircuitground SS_RX RX_IN1 8 INP MainRXinput RX_IN2 9 INP AuxiliaryRXinput V 10 SUP Chipsubstrateground SS BAND_GAP 11 OUT Bandgapvoltage(V =1.6V);internalanalogvoltagereference BG SelectionbetweenASKandOOKmodulation(0=ASK,1=OOK)fordirectmode0or1. ASK/OOK 12 BID Canbeconfiguredasanoutputtoprovidethereceivedanalogsignaloutput. (1) SUP=Supply,INP=Input,BID=Bidirectional,OUT=Output 8 TerminalConfigurationandFunctions Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 Table4-1.TerminalFunctions(continued) TERMINAL TYPE (1) DESCRIPTION NAME NO. IRQ 13 OUT Interruptrequest INP Externaldatamodulationinputfordirectmode0or1 MOD 14 OUT Subcarrierdigitaldataoutput(seeregisters0x1Aand0x1B) V 15 SUP Negativesupplyforinternalanalogcircuits;connectedtoGND SS_A V 16 INP SupplyforI/Ocommunications(1.8VtoV )levelshifter.V shouldbeneverexceeded. DD_I/O IN IN I/O_0 17 BID I/Opinforparallelcommunication I/O_1 18 BID I/Opinforparallelcommunication I/Opinforparallelcommunication I/O_2 19 BID TXenable(inspecialdirectmode) I/Opinforparallelcommunication I/O_3 20 BID TXdata(inspecialdirectmode) I/Opinforparallelcommunication I/O_4 21 BID SlaveselectsignalinSPImode I/Opinforparallelcommunication I/O_5 22 BID Dataclockoutputindirectmode1andspecialdirectmode I/Opinforparallelcommunication I/O_6 23 BID MISOforserialcommunication(SPI) Serialbitdataoutputindirectmode1orsubcarriersignalindirectmode0 I/Opinforparallelcommunication. I/O_7 24 BID MOSIforserialcommunication(SPI) Selectionofpowerdownmode.IfEN2isconnectedtoV ,thenV isactiveduringpower EN2 25 INP IN DD_X downmode2(forexample,tosupplytheMCU). DATA_CLK 26 INP DataclockinputforMCUcommunication(parallelandserial) IfEN=1(EN2=don'tcare)thesystemclockforMCUisconfigured.Dependingonthecrystal thatisused,optionsareasfollows(seeregister0x09): SYS_CLK 27 OUT 13.56-MHzcrystal:Off,3.39MHz,6.78MHz,or13.56MHz 27.12-MHzcrystal:Off,6.78MHz,13.56MHz,or27.12MHz IfEN=0andEN2=1,thensystemclockissetto60kHz EN 28 INP Chipenableinput(IfEN=0,thenchipisinsleeporpower-downmode). V 29 SUP Negativesupplyforinternaldigitalcircuits SS_D OSC_OUT 30 OUT Crystaloroscillatoroutput INP Crystaloroscillatorinput OSC_IN 31 OUT Crystaloscillatoroutput Internallyregulatedsupply(2.7Vto3.4V)fordigitalcircuitandexternaldevices(forexample, V 32 OUT DD_X anMCU) ThermalPad PAD SUP Chipsubstrateground Copyright©2011–2017,TexasInstrumentsIncorporated TerminalConfigurationandFunctions 9 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com 5 Specifications 5.1 Absolute Maximum Ratings(1) (2) overoperatingfree-airtemperaturerange(unlessotherwisenoted) MIN MAX UNIT V Inputvoltagerange –0.3 6 V IN I MaximumcurrentV 150 mA IN IN Anycondition 140 °C T Maximumoperatingvirtualjunctiontemperature J Continuousoperation,long-termreliability(3) 125 °C T Storagetemperature –55 150 °C STG (1) StressesbeyondthoselistedunderAbsoluteMaximumRatingsmaycausepermanentdamagetothedevice.Thesearestressratings onlyandfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderRecommendedOperating Conditionsarenotimplied.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability. (2) AllvoltagevaluesarewithrespecttosubstrategroundterminalV . SS (3) Themaximumjunctiontemperatureforcontinuousoperationislimitedbypackageconstraints.Operationabovethistemperaturemay resultinreducedreliabilityorlifetimeofthedevice. 5.2 ESD Ratings VALUE UNIT Human-bodymodel(HBM),perANSI/ESDA/JEDECJS-001,allpins(1) ±2000 V Charged-devicemodel(CDM),perJEDECspecificationJESD22-C101,all V(ESD) Electrostaticdischarge pins(2) ±500 V Machinemodel(MM) ±200 V (1) JEDECdocumentJEP155statesthat500-VHBMallowssafemanufacturingwithastandardESDcontrolprocess.Pinslistedas±2000 Vmayactuallyhavehigherperformance. (2) JEDECdocumentJEP157statesthat250-VCDMallowssafemanufacturingwithastandardESDcontrolprocess.Pinslistedas±500V mayactuallyhavehigherperformance. 5.3 Recommended Operating Conditions overoperatingfree-airtemperaturerange(unlessotherwisenoted) MIN TYP MAX UNIT V Operatinginputvoltage 2.7 5 5.5 V IN T Operatingambienttemperature –40 25 110 °C A T Operatingvirtualjunctiontemperature –40 25 125 °C J I/Olines,IRQ,SYS_CLK,DATA_CLK, 0.2× V Inputvoltage,logiclow V IL EN,EN2,ASK/OOK,MOD V DD_I/O I/Olines,IRQ,SYS_CLK,DATA_CLK, 0.8× V Inputvoltagethreshold,logichigh V IH EN,EN2,ASK/OOK,MOD V DD_I/O 10 Specifications Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 5.4 Electrical Characteristics TYPoperatingconditionsareT =25°C,VIN=5V,full-powermode(unlessotherwisenoted) A MINandMAXoperatingconditionsareoverrecommendedrangesofsupplyvoltageandoperatingfree-airtemperature (unlessotherwisenoted) PARAMETER TESTCONDITIONS MIN TYP MAX UNIT 0.2× V Low-leveloutputvoltage V OL V DD_I/O 0.8× V High-leveloutputvoltage V OH V DD_I/O Allbuildingblocksdisabled,including I Supplycurrentinpowerdownmode1 supply-voltageregulators;measuredafter 0.5 5 µA PD1 500-mssettlingtime(EN=0,EN2=0) TheSYS_CLKgeneratorandV DD_X Supplycurrentinpowerdownmode2 remainactivetosupportexternalcircuitry; I 120 200 µA PD2 (sleepmode) measuredafter100-mssettlingtime (EN=0,EN2=1) Oscillatorrunning,supply-voltage I Supplycurrentinstand-bymode regulatorsinlow-consumptionmode 1.9 3.5 mA STBY (EN=1,EN2=x) Supplycurrentwithoutantennadriver Oscillator,regulators,RXandAGC I 10.5 14 mA ON1 current active,TXisoff Oscillator,regulators,RXandAGCand I Supplycurrent,TX(halfpower) 70 78 mA ON2 TXactive,P =100mW OUT Oscillator,regulators,RXandAGCand I Supplycurrent,TX(fullpower) 130 150 mA ON3 TXactive,P =200mW OUT V Power-on-resetvoltage InputvoltageatV 1.4 2 2.6 V POR IN V Bandgapvoltage(pin11) Internalanalogreferencevoltage 1.5 1.6 1.7 V BG Regulatedoutputvoltageforanalog V V =5V 3.1 3.4 3.8 V DD_A circuitry(pin1) IN V Regulatedsupplyforexternalcircuitry Outputvoltagepin32,V =5V 3.1 3.4 3.8 V DD_X IN I MaximumoutputcurrentofV Outputcurrentpin32,V =5V 20 mA VDD_Xmax DD_X IN Half-powermode,V =2.7Vto5.5V 8 12 R Antennadriveroutputresistance (1) IN Ω RFOUT Full-powermode,V =2.7Vto5.5V 4 6 IN R RX_IN1andRX_IN2inputresistance 4 10 20 kΩ RFIN MaximumRFinputvoltageatRX_IN1 V V shouldnotexceedV 3.5 V RF_INmax andRX_IN2 RF_INmax IN pp MinimumRFinputvoltageatRX_IN1 fSUBCARRIER=424kHz 1.4 2.5 VRF_INmin andRX_IN2(inputsensitivity)(2) f =848kHz 2.1 3 mVpp SUBCARRIER f SYS_CLKfrequency Inpowermode2,EN=0,EN2=1 25 60 120 kHz SYS_CLK f Carrierfrequency Definedbyexternalcrystal 13.56 MHz C Timeuntiloscillatorstablebitisset tCRYSTAL Crystalrun-intime (register0x0F)(3) 3 ms fD_CLKmax MaximumDATA_CLKfrequency(4) Dlineepse,nTdIsreocnocmampaecnidtisve2loMaHdzo(4n)theI/O 2 4 10 MHz R OutputresistanceI/O_0toI/O_7 500 800 Ω OUT R OutputresistanceR 200 400 Ω SYS_CLK SYS_CLK (1) Antennadriveroutputresistance (2) MeasuredwithsubcarriersignalatRX_IN1orRX_IN2andmeasuredthedigitaloutputatMODpinwithregister0x1Abit6=1. (3) Dependsonthecrystalparametersandcomponents (4) TIrecommendsaDATA_CLKspeedof2MHz.Higherdataclockdependsonthecapacitiveload.MaximumSPIclockspeedshouldnot exceed10MHz.Thisclockspeedisacceptableonlywhenexternalcapacitiveloadislessthan30pF.MISOdriverhasatypicaloutput resistanceof400Ω(12-nstimeconstantwhen30-pFloadused). Copyright©2011–2017,TexasInstrumentsIncorporated Specifications 11 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com 5.5 Thermal Resistance Characteristics POWERRATING(2) PACKAGE θ θ (1) JC JA T ≤25°C T ≤85°C A A RHB(32pin) 31°C/W 36.4°C/W 2.7W 1.1W (1) ThisdatawastakenusingtheJEDECstandardhigh-KtestPCB. (2) Powerratingisdeterminedwithajunctiontemperatureof125°C.Thisisthetemperatureatwhichdistortionstartstoincrease substantially.ThermalmanagementofthefinalPCBshouldstrivetokeepthejunctiontemperatureatorbelow125°Cforbest performanceandlong-termreliability. 5.6 Switching Characteristics TYPoperatingconditionsareT =25°C,VIN=5V,full-powermode(unlessotherwisenoted) A MINandMAXoperatingconditionsareoverrecommendedrangesofsupplyvoltageandoperatingfree-airtemperature (unlessotherwisenoted) PARAMETER TESTCONDITIONS MIN TYP MAX UNIT DATA_CLKtimehighorlow,onehalfofDATA_CLKat Dependsoncapacitiveloadonthe tLO/HI 50%dutycycle I/Olines(1) 250 62.5 50 ns t Slaveselectleadtime,slaveselectlowtoclock 200 ns STE,LEAD t Slaveselectlagtime,lastclocktoslaveselecthigh 200 ns STE,LAG Slaveselectdisabletime,slaveselectrisingedgeto t 300 ns STE,DIS nextslaveselectfallingedge t MOSIinputdatasetuptime 15 ns SU,SI t MOSIinputdataholdtime 15 ns HD,SI t MISOinputdatasetuptime 15 ns SU,SO t MISOinputdataholdtime 15 ns HD,SO DATA_CLKedgetoMISOvalid, t MISOoutputdatavalidtime 30 50 75 ns VALID,SO C ≤30pF L (1) TIrecommendsaDATA_CLKspeedof2MHz.Higherdataclockdependsonthecapacitiveload.MaximumSPIclockspeedshouldnot exceed10MHz.Thisclockspeedisacceptableonlywhenexternalcapacitiveloadislessthan30pF.MISOdriverhasatypicaloutput resistanceof400Ω(12-nstimeconstantwhen30-pFloadused). 12 Specifications Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 6 Detailed Description 6.1 Overview 6.1.1 RFID and NFC Operation – Reader and Writer The TRF7970A is a high-performance 13.56-MHz HF RFID and NFC transceiver IC composed of an integrated analog front end (AFE) and a built-in data framing engine for ISO/IEC 15693, ISO/IEC 14443 A and B, and FeliCa. This includes data rates up to 848 kbps for ISO/IEC 14443 with all framing and synchronization tasks on board (in default mode). The TRF7970A also supports NFC tag type 1, 2, 3, 4, and 5 operations. This architecture lets the customer build a complete cost-effective yet high-performance multiprotocol13.56-MHzRFID andNFCsystemtogetherwithalow-costmicrocontroller. Other standards and even custom protocols can be implemented by using either of the direct modes that the device offers. These direct modes (0 and 1) allow the user to fully control the analog front end (AFE) and also gain access to the raw subcarrier data or the unframed but already ISO formatted data and the associated(extracted)clocksignal. The receiver system has a dual input receiver architecture. The receivers also include various automatic and manual gain control options. The received input bandwidth can be selected to cover a broad range of inputsubcarriersignaloptions. The received signal strength from transponders, ambient sources, or internal levels is available through the RSSI register. The receiver output is selectable among a digitized subcarrier signal and any of the integrated subcarrier decoders. The selected subcarrier decoder delivers the data bit stream and the data clockasoutputs. The TRF7970A also includes a receiver framing engine. This receiver framing engine performs the CRC or parity check, removes the EOF and SOF settings, and organizes the data in bytes for ISO/IEC 14443 A and B, ISO/IEC 15693, and FeliCa protocols. Framed data is then accessible to the microcontroller (MCU) througha127-byteFIFOregister. V DD VDD_X VDD_I/O VDD TX_OUT Matching Parallel MCU TRF7970A RX_IN 1 or SPI (MSP430 orARM) RX_IN2 V V XIN SS IN Crystal 13.56 MHz Supply: 2.7 V to 5.5 V Figure6-1.ApplicationBlockDiagram A parallel or serial interface (SPI) can be used for the communication between the MCU and the TRF7970A reader. When the built-in hardware encoders and decoders are used, transmit and receive functions use a 127-byte FIFO register. For direct transmit or receive functions, the encoders and decoders can be bypassed so that the MCU can process the data in real time. The TRF7970A supports data communication voltage levels from 1.8 V to 5.5 V for the MCU I/O interface. The transmitter has selectable output-power levels of 100 mW (+20 dBm) or 200 mW (+23 dBm) equivalent into a 50-Ω load whenusinga5-Vsupply. Copyright©2011–2017,TexasInstrumentsIncorporated DetailedDescription 13 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com ThetransmittersupportsOOKandASKmodulationwithselectablemodulationdepth.The TRF7970Aalso includes a data transmission engine that comprises low-level encoding for ISO/IEC 15693, ISO/IEC 14443 A and B, and FeliCa. Included with the transmit data coding is the automatic generation of Start Of Frame (SOF),EndOfFrame(EOF),CyclicRedundancyCheck(CRC),andparitybits. Several integrated voltage regulators ensure a proper power-supply noise rejection for the complete readersystem.Thebuilt-inprogrammableauxiliaryvoltageregulatorV (pin32),isabletodeliverupto DD_X 20mAtosupplyamicrocontrollerandadditionalexternalcircuitswithinthereadersystem. 6.1.2 NFC Device Operation – Initiator The transmitting system includes an RF level detector (programmable level) which is used for initial (or response) RF collision avoidance. The RF collision avoidance sequence is started by sending a direct command. If successful, the NFC initiator can send the data or commands, the MCU has loaded in the FIFO register. The coding of this data is done by hardware coders in ISO/IEC 14443 A and B, or FeliCa format. The coders also provide CRC and parity bits (if required) and automatically add preambles, SOF, EOF,andsynchronizationbytesasdefinedbyselectedprotocol. The receiver system offers the same analog features (AGC, AM or PM, bandwidth selection, and so on) as described previously in RFID and NFC reader and writer description. The system comprises integrated decoders for passive targets (ISO/IEC 14443 A or ISO/IEC 14443 B tag or FeliCa) or active targets (ISO/IEC 14443 A or ISO/IEC 14443 B reader or FeliCa). For all this options, the system also supports framing including CRC and parity check and removal of SOF, EOF, and synchronization bytes as specifiedbytheselectedprotocol. 6.1.3 NFC Device Operation – Target The activation of NFC target is done when a sufficient RF field level is detected on the antenna. The level neededforwake-upisselectableandisstoredinanonvolatileregister. When the activation occurs, the system performs automatic power-up and waits for the first command to be received. Based on this command, the system knows if it should operate as passive or active target and at what bit rate. After activation, the receiver system offers the same analog features (for example, AGC,AM/PM,andbandwidthselection)asinthecaseofanRFIDreader. When used as the NFC target, the chip is typically in a power down or standby mode. If EN2 = H, the chip keeps the supply system on. If EN2 = L and EN = L, the chip is in complete power down. To operate as NFC target or card emulator, the MCU must load a value different from zero (0) in the Target Detection Level register (B0-B2) to enable the RF measurement system (supplied by VEXT, so it can also operate during complete power down and consume only 3.5 µA). The RF measurement constantly monitors the RF signal on the antenna input. When the RF level on the antenna input exceeds the level defined in the inTargetDetectionLevelregister,thechipisautomaticallyactivated(ENisinternallyforcedhigh). When the voltage supply system and the oscillator are started and are stable, osc_ok goes high (B6 of RSSI Level and Oscillator Status register) and IRQ is sent with bit B2 = 1 of IRQ register (field change). Bit B7 NFC Target Protocol in register directly displays the status of RF level detection (running constantly also during normal operation). This informs the MCU that the chip should start operation as NFC TARGET device. When the first command from the INITIATOR is received, another IRQ sent with B6 (RX start) set in the IRQ register. The MCU must set EN = H (confirm the power up) in the time between the two IRQs, because the internal power-up ends after the second IRQ. The type and coding of the first initiator (or reader in the case of a card emulator) command defines the communication protocol type that the target must use. Therefore, the communication protocol type is available in the NFC Target Protocol register immediatelyafterreceivingthefirstcommand. 14 DetailedDescription Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 BasedonthefirstcommandfromtheINITIATOR,thefollowingactionsaretaken: • If the first command is SENS_REQ or ALL_REQ, the TARGET must enter the SDD protocol for 106- kbps passive communication to begin; afterward, the baud rate can be changed to 212 kbps or 424 kbps, which is determined by the NFC initiator device. If bit B5 in the NFC Target Detection Level register is not set, the MCU handles the SDD and the command received is send to FIFO. For interoperability purposes, TI recommends allowing the MCU to handle the SDD process rather than use the TRF7970A Auto-SDD feature to ensure interoperability with other NFC devices. If the RF field is turned off (B7 in NFC Target Protocol register is low) at any time, the system sends an IRQ to the MCU with bit B2 (RF field change) in the IRQ register set high. This informs the MCU that the procedure was aborted and the system must be reset. The clock extractor is automatically activated in thismode. • If the command is SENS_REQ or ALL_REQ and the card emulation bit in ISO Control register is set, the system emulates an ISO/IEC 14443 A or ISO/IEC 14443 B tag. The procedure does not differ from the one previously described for the case of a passive target at 106 kbps. The clock extractor is automaticallyactivatedinthismode. • If the first command is a SENSF_REQ, the system becomes the TARGET in passive communication using212kbpsor424kbps.TheSDDisrelativelysimpleandishandledbytheMCUdirectly. • If the first command is ATR_REQ, the system operates as an active TARGET using the same communication speed and bit coding as used by the INITIATOR. Again, all of the replies are handled by the MCU. The MCU should handle the timing requirements for collision avoidance. This is done by usingexternalRSSItodetectexternalRFfieldsbeforeenablingRFontheTRF7970A. • If the first command is a SENSB_REQ request and the card emulation bit is set in the ISO Control register,thesystementersISO/IEC14443Bemulationmode.Theanticollisionmustbehandledbythe MCU,andthechipprovidesallphysicallevelcoding,decoding,andframingforthisprotocol. 6.1.3.1 ActiveTarget If the first command received by the RF interface defines the system as an active target, then the receiver selects the appropriate data decoders (ISO/IEC 14443 A or ISO/IEC 14443 B reader or peer-to-peer) and framing option. Only the raw (decoded) data is forwarded to the MCU through the FIFO. SOF, EOF, preamble,syncbytes,CRC,andparitybytesarecheckedbytheframeranddiscarded. The transmission of a response must occur after RF collision avoidance has been processed. The recommended method for RF collision avoidance is to use external RSSI to detect any external RF field. If successful, the NFC initiator can send the data that the MCU has loaded in the FIFO register. The coding ofthisdataisdonebyhardwarecoderseitherinISO/IEC14443Aformat(106-kbpssystem)orinpeer-to- peer format for (212-kbps and 424-kbps systems). The coders also provide CRC and parity bits (if required) and automatically add preambles, SOF, EOF, and synchronization bytes as defined by selected protocol. 6.1.3.2 PassiveTarget IfthefirstcommandreceivedbytheRFinterfacedefinesthesystemasapassivetarget,thenthereceiver selects the appropriate data decoders (ISO/IEC 14443 A or ISO/IEC 14443 B reader or peer-to-peer) and framing option. Again, only the raw (decoded) data is forwarded to the MCU through the FIFO; SOF, EOF, preamble, sync bytes, CRC, and parity bytes are checked by the framer and discarded. The receiver workssameasinthecaseofanactivetarget. The transmit system in passive target mode differs from active target and operates similar to the standard tag. There is no RF collision avoidance sequence, and encoders are used to code the data for ISO/IEC 14443 A or ISO/IEC 14443 B tag (at 106 kbps, to start) or peer-to-peer (at 212 kbps, to start) format. The coding system adds all of the SOF, EOF, CRC, parity bits, and synchronization bytes that are requiredbyprotocol.Theresponseistransmittedover-the-airwithamethodknownasloadmodulation. Copyright©2011–2017,TexasInstrumentsIncorporated DetailedDescription 15 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com 6.1.3.3 CardEmulation The chip can enter this mode by setting appropriate option bits. The chip can emulate ISO/IEC 14443 A and B card types. For ISO/IEC 14443 A and B, the emulation supports 106-kbps data rate to start. For ISO/IEC 14443 A, the anticollision algorithm can be performed using an internal state machine, which relieves the MCU of any real-time tasks; however, this method can present interoperability challenges with other NFC devices due to timing requirements. To ensure best interoperability, TI recommends allowing the MCU to manage the anticollision process, instead. The unique ID required for anticollision is provided bytheMCUafterwakeupofthesystem. 6.2 System Block Diagram Figure6-2showsablockdiagramofthe TRF7970A. VDD_I/O RX_IN1 MUX PAhmapsleituadned Gain (RASUSXI) Logic I/O_0 Detector State I/O_1 RF Level Control Detector Logic I/O_2 RX_IN2 RSSI (Control I/O_3 (External) Registersand Phaseand (RMSaSinI) CoLmogmica)nd Level II//OO__45 Amplitude Gain Sh Detector anFdilAteGrC Digitizer MCU ifter I/O_6 VDD_PA Interface I/O_7 ISO Protocol Decoder IRQ Handling SYS_CLK TX_OUT Transmitter Framing Bit 127-Byte Analog Front End Framing FIFO DATA_CLK VIN Serial Conversion VDD_A VSS_PA CRC and Parity BAND_GAP EN VSS_A EN2 Digital Control VDD_RF ASK/OOK State Machine MOD Voltage SupplyRegulator Systems VSS_RF (SupplyRegulatorsand ReferenceVoltages) VDD_X OSC_IN VSS Crystal or Oscillator OSC_OUT Timing System VSS_D Copyright © 2017,Texas Instruments Incorporated Figure6-2.SystemBlockDiagram 6.3 Power Supplies The TRF7970A positive supply input V (pin 2) sources three internal regulators with output voltages IN V , V and V . All regulators use external bypass capacitors for supply noise filtering and must DD_RF DD_A DD_X be connected as indicated in reference schematics. These regulators provide a high power supply reject ratio(PSRR)asrequiredforRFIDreadersystems.AllregulatorsaresuppliedbyV (pin2). IN The regulators are not independent and have common control bits in register 0x0B for output voltage setting. The regulators can be configured to operate in either automatic or manual mode (register 0x0B, bit 7). The automatic regulator setting mode ensures an optimal compromise between PSRR and the highest possible supply voltage for RF output (to ensure maximum RF power output). The manual mode allows the user to manually configure the regulator settings. For applications in which the TRF7970A may besubjectedtoexternalnoise,manuallyreducingtheregulatorsettingscanimproveRFperformance. 16 DetailedDescription Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 6.3.1 Supply Arrangements RegulatorSupplyInput:V IN The positive supply at V (pin 2) has an input voltage range of 2.7 V to 5.5 V. V provides the supply IN IN input sources for three internal regulators with the output voltages V , V , and V . External DD_RF DD_A DD_X bypasscapacitorsforsupplynoisefilteringmustbeused(perreferenceschematics). NOTE V mustbethehighestvoltagesuppliedtotheTRF7970A. IN RFPowerAmplifierRegulator:V DD_RF The V (pin 3) regulator is supplying the RF power amplifier. The voltage regulator can be set for DD_RF either 5-V or 3-V operation. External bypass capacitors for supply noise filtering must be used (per reference schematics). When configured for 5-V manual-operation, the V output voltage can be set DD_RF from 4.3 V to 5 V in 100-mV steps. In 3-V manual-operation, the output can be programmed from 2.7 V to 3.4 V in 100-mV steps. The maximum output current capability for 5-V operation is 150 mA and for 3-V operationis100mA. AnalogSupplyRegulator:V DD_A Regulator V (pin 1) supplies the analog circuits of the device. The output voltage setting depends on DD_A the input voltage and can be set for 5-V and 3-V operation. When configured for 5-V manual-operation, the output voltage is fixed at 3.4 V. External bypass capacitors for supply noise filtering must be used (per reference schematics). When configured for 3-V manual-operation, the V output can be set from 2.7 V DD_A to3.4Vin100-mVsteps(seeTable6-2). NOTE The configuration of V and V regulators are not independent from each other. The DD_A DD_X V outputcurrentshouldnotexceed20mA. DD_X DigitalSupplyRegulator:V DD_X The digital supply regulator V (pin 32) provides the power for the internal digital building blocks and DD_X can also be used to supply external electronics within the reader system. When configured for 3-V operation, the output voltage can be set from 2.7 to 3.4 V in 100-mV steps. External bypass capacitors for supplynoisefilteringmustbeused(perreferenceschematics). NOTE The configuration of the V and V regulators are not independent from each other. DD_A DD_X TheV outputcurrentshouldnotexceed20mA. DD_X By default, the regulators are set in automatic regulator setting mode. In this mode, the regulators are automatically set every time the system is activated by setting EN input High or each time the automatic regulator setting bit, B7 in register 0x0B is set to a 1. The action is started on the 0 to 1 transition. This means that, if the user wants to rerun the automatic setting from a state in which the automatic setting bit isalreadyhigh,theautomaticsettingbit(B7inregister0x0B)shouldbechanged:1-0-1. By default, the regulator setting algorithm sets the regulator outputs to a "Delta Voltage" of 400 mV below V ,butnothigherthan5VforV and3.4VforV andV . IN DD_RF DD_A DD_A Copyright©2011–2017,TexasInstrumentsIncorporated DetailedDescription 17 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com PowerAmplifierSupply:V DD_PA The power amplifier of the TRF7970A is supplied through V (pin 4). The positive supply pin for the DD_PA RFpoweramplifierisexternallyconnectedtotheregulatoroutputV (pin3). DD_RF I/OLevelShifterSupply:V DD_I/O The TRF7970A has a separate supply input V (pin 16) for the built-in I/O level shifter. The supported DD_I/O input voltage ranges from 1.8 V to V , not exceeding 5.5 V. Pin 16 is used to supply the I/O interface pins IN (I/O_0 to I/O_7), IRQ, SYS_CLK, and DATA_CLK pins of the reader. In typical applications, V is DD_I/O directly connected to V , while V also supplies the MCU. This ensures that the I/O signal levels of DD_X DD_X theMCUmatchthelogiclevelsoftheTRF7970A. NegativeSupplyConnections:V ,V ,V ,V ,V SS SS_TX SS_RX SS_A SS_PA ThenegativesupplyconnectionsV ofeachfunctionalblockareallexternallyconnectedtoGND. SS_X The substrate connection is V (pin 10), the analog negative supply is V (pin 15), the logic negative SS SS_A supply is V (pin 29), the RF output stage negative supply is V (pin 6), and the negative supply for SS_D SS_PA theRFreceiverV (pin7). SS_RX 18 DetailedDescription Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 6.3.2 Supply Regulator Settings The input supply voltage mode of the reader needs to be selected. This is done in the Chip Status Control register (0x00). Bit 0 in register 0x00 selects between 5-V or 3-V input supply voltage. The default configuration is 5 V, which reflects an operating supply voltage range of 4.3 V to 5.5 V. If the supply voltageisbelow4.3V,the3-Vconfigurationshouldbeused. As V is increased, the system can become more susceptible to noise coupling on the RX lines. For DD_RF minimum noise coupling, TI recommends using the value of 0x00. For improved range, higher V DD_RF voltages may be set, but complete system testing is required to determine the value which provides optimalperformance. The various regulators can be configured to operate in automatic or manual mode. This is done in the RegulatorandI/OControlregister(0x0B),asshowninTable6-1 andTable6-2. Table6-1.SupplyRegulatorSetting:5-VSystem REGISTER OPTIONBITSSETTINGINREGULATORCONTROLREGISTER(1) ADDRESS COMMENTS (hex) B7 B6 B5 B4 B3 B2 B1 B0 AutomaticMode(default) 0B 1 x x x x x 0 0 Automaticregulatorsetting400-mVdifference ManualMode 0B 0 x x x x 1 1 1 VDD_RF=5V,VDD_A=3.4V,VDD_X=3.4V 0B 0 x x x x 1 1 0 VDD_RF=4.9V,VDD_A=3.4V,VDD_X=3.4V 0B 0 x x x x 1 0 1 VDD_RF=4.8V,VDD_A=3.4V,VDD_X=3.4V 0B 0 x x x x 1 0 0 VDD_RF=4.7V,VDD_A=3.4V,VDD_X=3.4V 0B 0 x x x x 0 1 1 VDD_RF=4.6V,VDD_A=3.4V,VDD_X=3.4V 0B 0 x x x x 0 1 0 VDD_RF=4.5V,VDD_A=3.4V,VDD_X=3.4V 0B 0 x x x x 0 0 1 VDD_RF=4.4V,VDD_A=3.4V,VDD_X=3.4V 0B 0 x x x x 0 0 0 VDD_RF=4.3V,VDD_A=3.4V,VDD_X=3.4V (1) x=Don'tcare Table6-2.SupplyRegulatorSetting:3-VSystem REGISTER OPTIONBITSSETTINGINREGULATORCONTROLREGISTER(1) ADDRESS COMMENTS (hex) B7 B6 B5 B4 B3 B2 B1 B0 AutomaticMode(default) 0B 1 x x x x x 0 0 Automaticregulatorsetting400-mVdifference ManualMode 0B 0 x x x x 1 1 1 VDD_RF=3.4V,VDD_A=3.4V,VDD_X=3.4V 0B 0 x x x x 1 1 0 VDD_RF=3.3V,VDD_A=3.3V,VDD_X=3.3V 0B 0 x x x x 1 0 1 VDD_RF=3.2V,VDD_A=3.2V,VDD_X=3.2V 0B 0 x x x x 1 0 0 VDD_RF=3.1V,VDD_A=3.1V,VDD_X=3.1V 0B 0 x x x x 0 1 1 VDD_RF=3.0V,VDD_A=3.0V,VDD_X=3.0V 0B 0 x x x x 0 1 0 VDD_RF=2.9V,VDD_A=2.9V,VDD_X=2.9V 0B 0 x x x x 0 0 1 VDD_RF=2.8V,VDD_A=2.8V,VDD_X=2.8V 0B 0 x x x x 0 0 0 VDD_RF=2.7V,VDD_A=2.7V,VDD_X=2.7V (1) x=Don'tcare Theregulatorconfigurationfunctionadjuststheregulatoroutputsbydefaultto400mVbelowV level,but IN not higher than 5 V for V , 3.4 V for V and V . This ensures the highest possible supply DD_RF DD_A DD_X voltagefortheRFoutputstagewhilemaintaininganadequatePSRR(powersupplyrejectionratio). Copyright©2011–2017,TexasInstrumentsIncorporated DetailedDescription 19 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com 6.3.3 Power Modes The chip has several power states, which are controlled by two input pins (EN and EN2) and several bits inthechipstatuscontrolregister(0x00)(seeTable6-3andTable6-4). Table6-3.3.3-VOperationPowerModes(1) CHIP REGULATOR STATUS TYPICAL TYPICAL CONTROL SYS_CLK SYS_CLK MODE EN2 EN CONTROL REGISTER TRANSMITTER RECEIVER (13.56MHz) (60kHz) VDD_X CURRENT POWER REGISTER (mA) OUT(dBm) (0x0B) (0x00) Powerdown 0 0 XX XX OFF OFF OFF OFF OFF <0.001 - Sleepmode 1 0 XX XX OFF OFF OFF ON ON 0.120 - Standbymodeat+3.3VDC X 1 80 00 OFF OFF ON X ON 2 - Mode1at+3.3VDC X 1 00 00 OFF OFF ON X ON 3 - Mode2at+3.3VDC X 1 02 00 OFF ON ON X ON 9 - Mode3(halfpower)at X 1 30 07 ON ON ON X ON 53 14.5 +3.3VDC Mode4(fullpower)at X 1 20 07 ON ON ON X ON 67 17 +3.3VDC (1) X=Don'tcare Table6-4.5-VOperationPowerModes(1) CHIP REGULATOR STATUS TYPICAL TYPICAL CONTROL SYS_CLK SYS_CLK MODE EN2 EN CONTROL REGISTER TRANSMITTER RECEIVER (13.56MHz) (60kHz) VDD_X CURRENT POWER REGISTER (mA) OUT(dBm) (0x0B) (0x00) Powerdown 0 0 XX XX OFF OFF OFF OFF OFF <0.001 - Sleepmode 1 0 XX XX OFF OFF OFF ON ON 0.120 - Standbymodeat+5VDC X 1 81 07 OFF OFF ON X ON 3 - Mode1at+5VDC X 1 01 07 OFF OFF ON X ON 5 - Mode2at+5VDC X 1 03 07 OFF ON ON X ON 10.5 - Mode3(halfpower)at X 1 31 07 ON ON ON X ON 70 20 +5VDC Mode4(fullpower)at X 1 21 07 ON ON ON X ON 130 23 +5VDC (1) X=Don'tcare Table 6-3 and Table 6-4 show the configuration for the different power modes when using a 3.3-V or 5-V system supply, respectively. The main reader enable signal is pin EN. When EN is set high, all of the reader regulators are enabled, the 13.56-MHz oscillator is running and the SYS_CLK (output clock for externalmicrocontroller)isalsoavailable. TheinputpinEN2hastwofunctions: • A direct connection from EN2 to V to ensure the availability of the regulated supply V and an IN DD_X auxiliary clock signal (60 kHz, SYS_CLK) for an external MCU. This mode (EN = 0, EN2 = 1) is intended for systems in which the MCU is also being supplied by the reader supply regulator (V ) DD_X and the MCU clock is supplied by the SYS_CLK output of the reader. This allows the MCU supply and clocktobeavailableduringsleepmode. • EN2 enables the start-up of the reader system from complete power down (EN = 0, EN2 = 0). In this case the EN input is being controlled by the MCU (or other system device) that is without supply voltage during complete power down (thus unable to control the EN input). A rising edge applied to the EN2input(whichhasanapproximately1-Vthresholdlevel)startsthereadersupplysystemand13.56- MHzoscillator(identicaltoconditionEN=1). When user MCU is controlling EN and EN2, a delay of 1 ms between EN and EN2 must be used. If the MCU controls only EN, TI recommends connecting EN2 to either V or GND, depending on the IN applicationMCUrequirementsforV andSYS_CLK. DD_X 20 DetailedDescription Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 VIN 2ms SS 5ms EN2 6ms EN Figure6-3.NominalStart-upSequenceUsingSPIWithSS(MCUControlsEN2) VIN 5ms EN2 6ms EN Figure6-4.NominalStart-upSequenceUsingParallel(MCUControlsEN2) This start-up mode lasts until all of the regulators have settled and the 13.56-MHz oscillator has stabilized. IftheENinputissethigh(EN=1)bytheMCU(orothersystemdevice),thereaderstaysactive.IftheEN input is not set high (EN = 0) within 100 µs after the SYS_CLK output is switched from auxiliary clock (60 kHz) to high-frequency clock (derived from the crystal oscillator), the reader system returns to complete Power-Down Mode 1. This option can be used to wake-up the reader system from complete Power Down (PDMode1)byusingapushbuttonswitchorbysendingasinglepulse. After the reader EN line is high, the other power modes are selected by control bits within the chip status controlregister(0x00).ThepowermodeoptionsandstatesarelistedinTable6-3. When EN is set high (or on rising edge of EN2 and then confirmed by EN = 1) the supply regulators are activated and the 13.56-MHz oscillator is started. When the supplies are settled and the oscillator frequency is stable, the SYS_CLK output is switched from the auxiliary frequency of 60 kHz to the 13.56- MHz frequency derived from the crystal oscillator. At this point, the reader is ready to communicate and performtherequiredtasks.Whenthisoccurs,osc_ok(B6)oftheRSSILevelandOscillatorStatusregister is set. The MCU can then program the Chip Status Control register 0x00 and select the operation mode byprogrammingtheadditionalregisters. • Standby Mode (bit 7 = 1 of register 0x00), the reader is capable of recovering to full operation in 100µs. • Mode 1 (active mode with RF output disabled, bit 5 = 0 and bit 1 = 0 of register 0x00) is a low power modewhichallowsthereadertorecovertofulloperationwithin25 µs. • Mode 2 (active mode with only the RF receiver active, bit 1 = 1 of register 0x00) can be used to measure the external RF field (as described in RSSI measurements paragraph) if reader-to-reader anticollisionisimplemented. • Modes 3 and 4 (active modes with the entire RF section active, bit 5 = 1 of register 0x00) are the normalmodesusedfornormaltransmitandreceiveoperations. Copyright©2011–2017,TexasInstrumentsIncorporated DetailedDescription 21 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com 6.4 Receiver – Analog Section 6.4.1 Main and Auxiliary Receivers The TRF7970A has two receiver inputs: RX_IN1 (pin 8) and RX_IN2 (pin 9). Each of the input is connected to an external capacitive voltage divider to ensure that the modulated signal from the tag is available on at least one of the two inputs. This architecture eliminates any possible communication holes thatmayoccurfromthetagtothereader. The two RX inputs (RX_IN1 and RX_IN2) are multiplexed into two receivers - the main receiver and the auxiliary receiver. Only the main receiver is used for reception, the auxiliary receiver is used for signal quality monitoring. Receiver input multiplexing is controlled by bit B3 in the Chip Status Control register (address0x00). Afterstart-up,RX_IN1ismultiplexedtothemainreceiverwhichiscomposedofanRFenvelopedetection, first gain and band-pass filtering stage, second gain and filtering stage with AGC. Only the main receiver is connected to the digitizing stage which output is connected to the digital processing block. The main receiver also has an RSSI measuring stage, which measures the strength of the demodulated signal (subcarriersignal). The primary function of the auxiliary receiver is to monitor the RX signal quality by measuring the RSSI of the demodulated subcarrier signal (internal RSSI). After start-up, RX_IN2 is multiplexed to the auxiliary receiver.TheauxiliaryreceiverhasanRFenvelopedetectionstage,firstgainandfilteringwithAGCstage andfinallytheauxiliaryRSSIblock. The default MUX setting is RX_IN1 connected to the main receiver and RX_IN2 connected to the auxiliary receiver.Todeterminethesignalquality,theresponsefromthetagisdetectedbythe"main"(pinRX_IN1) and "auxiliary" (pin RX_IN2) RSSI. Both values measured and stored in the RSSI Levels and Oscillator Status register (address 0x0F). The MCU can read the RSSI values from the TRF7970A RSSI register andmakethedecisionifswappingtheinput-signalsispreferableornot.SettingB3inChipStatusControl register (address 0x00) to 1 connects RX_IN1 (pin 8) to the auxiliary received and RX_IN2 (pin 9) to the mainreceiver. ThemainandauxiliaryreceiverinputstagesareRFenvelopedetectors.TheRFamplitudeatRX_IN1and RX_IN2 should be approximately 3 VPP for a V supply level greater than 3.3 V. If the V level is lower, IN IN theRFinputpeak-to-peakvoltagelevelshouldnotexceedtheV level. IN 6.4.2 Receiver Gain and Filter Stages The first gain and filtering stage has a nominal gain of 15 dB with an adjustable band-pass filter. The band-pass filter has programmable 3-dB corner frequencies between 110 kHz to 450 kHz for the high- pass filter and 570 kHz to 1500 kHz for the low-pass filter. After the band-pass filter, there is another gain- and-filteringstagewithanominalgainof8dBandwithfrequencycharacteristicsidenticaltothefirstband- passstage. The internal filters are configured automatically depending on the selected ISO communication standard in the ISO Control register (address 0x01). If required, additional fine tuning can be done by writing directly totheRXSpecialSettingregisters(address0x0A). Table 6-5 shows the various settings for the receiver analog section. Setting B4, B5, B6, and B7 to 0 results in a band-pass characteristic of 240 kHz to 1.4 MHz, which is appropriate for ISO/IEC 14443 B 106kbps,ISO/IEC14443AandBdataratesof212kbpsand424kbps,andFeliCa424kbps. 22 DetailedDescription Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 Table6-5.RXSpecialSettingRegister(0x0A) Function:Setsthegainsandfiltersdirectly Default:0x40atPOR=HorEN=L,andateachwritetotheISOControlregister(0x01).WhenbitsB7,B6,B5andB4areallzero,the filtersaresetforISO/IEC14443B(240kHzto1.4MHz). Bit Name Function Description B7 C212 Band-pass110kHzto570kHz Appropriatefor212-kHzsubcarriersystem(FeliCa) B6 C424 Band-pass200kHzto900kHz Appropriatefor424-kHzsubcarrierusedinISO/IEC15693 AppropriateforManchester-coded848-kHzsubcarrierusedin B5 M848 Band-pass450kHzto1.5MHz ISO/IEC14443AandB Band-pass100kHzto1.5MHz Appropriateforhighestbitrate(848kbps)usedinhigh-bit-rate B4 hbt Gainreducedfor18dB ISO/IEC14443 B3 gd1 00=Gainreduction0dB 01=Gainreductionfor5dB SetstheRXgainreductionandreducessensitivity B2 gd2 10=Gainreductionfor10dB 11=Gainreductionfor15dB B1 Reserved B0 Reserved 6.5 Receiver – Digital Section The output of the TRF7970A analog receiver block is a digitized subcarrier signal and is the input to the digital receiver block, which consists of two sections that partly overlap. The digitized subcarrier signal is a digital representation of the modulation signal on the RF envelope. The two sections of the digital receiver blockaretheprotocolbitdecodersectionandtheframinglogic section. The protocol bit decoder section converts the subcarrier coded signal into a serial bit stream and a data clock. The decoder logic is designed for maximum error tolerance. This tolerance lets the decoder section successfully decode even partly corrupted subcarrier signals that would otherwise be lost due to noise or interference. The framing logic section formats the serial bit stream data from the protocol bit decoder stage into data bytes. During the formatting process, special signals such as the start of frame (SOF), end of frame (EOF), start of communication, and end of communication are automatically removed. The parity bits and CRC bytes are also checked and removed. The end result is "clean or raw" data that is sent to the 127- byte FIFO register where it can be read by the external microcontroller system. Providing the data this way, in conjunction with the timing register settings of the TRF7970A, means that the firmware developer does not need to know the finer details of the ISO protocols to create a very robust application, especially inlow-costplatformsinwhichcodespaceisatapremiumandhighperformanceisstillrequired. The start of the receive operation (successfully received SOF) sets the IRQ flags in the IRQ Status register (0x0C). The end of the receive operation is signaled to the external system MCU by setting pin 13 (IRQ) to high. When data is received in the FIFO, an interrupt is sent to the MCU to signal that there is data to be read from the FIFO. The FIFO Status register (0x1C) should be used to provide the number of bytes that should be clocked out during the actual FIFO read. Additionally, an interrupt is sent to the MCU when the received data occupies 75% of the FIFO capacity to signal that the data should be removed from the FIFO. By default, that interrupt is triggered once the received data packet is longer than 124 bytes.ThissettingcanbemodifiedintheAdjustableFIFOIRQLevelsregister(0x14). Any error in the data format, parity, or CRC is detected and notified to the external system by setting pin 13 (IRQ) to high. The source condition of the interrupt is available in the IRQ Status register (0x0C). Section 6.15.3.3.1 describes the bit coding description of this register. The information in the IRQ Status register differs if the chip is configured as an RFID reader or as an NFC device (including card emulation). Section6.13 describesNFCoperation. Copyright©2011–2017,TexasInstrumentsIncorporated DetailedDescription 23 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com The framing section also supports bit-collision detection as specified in ISO/IEC 14443 A and ISO/IEC 15693. When a bit collision is detected, an interrupt request is sent and a flag is set in the IRQ Status register (0x0C). For ISO/IEC 14443 A specifically, the position of the bit collision is written in two registers: partly in the Collision Position register (0x0E) and partly in the Collision Position and Interrupt Maskregister(0x0D)(bitsB6andB7). This collision position is presented as sequential bit number, where the count starts immediately after the start bit. This means a collision in the first bit of a UID would give the value 00 0001 0000 in these registers when their contents are combined after being read (the count starts with 0 and the first 16 bits arethecommandcodeandthenumberofvalidbits[NVB]byte). Thereceivesectionalsocontainstwotimers. The RX wait time timer is controlled by the value in the RX Wait Time register (0x08). This timer defines the time interval after the end of the transmit operation during which the receive decoders are not active (held in reset state). This prevents false detections resulting from transients following the transmit operation. The value of the RX Wait Time register (0x08) defines the time in increments of 9.44 µs. This register is preset at every write to the ISO Control register (0x01) according to the minimum tag response timedefinedbyeachstandard. The RX no response timer is controlled by the RX No Response Wait Time register (0x07). This timer measures the time from the start of the slot in the anticollision sequence until the start of tag response. If thereisnotagresponseinthedefinedtime,aninterruptrequestissentandaflagissetintheIRQStatus register(0x0C).Thisenablestheexternalcontrollertoberelievedofthetaskofdetectingemptyslots.The wait time is stored in the register in increments of 37.76 µs. This register is also preset automatically for everynewprotocolselection. The main register controlling the digital part of the receiver is the ISO Control register (0x01). By writing to this register, the user selects the protocol to be used. With each new write in this register, all related registers are preset to their defaults for the protocol, so no further adjustments in other registers are neededforproperoperation.Table6-6describesthebitfieldsoftheISOControlregister(0x01). NOTE If changes to other registers are needed to fine-tune the system, those changes must be madeaftersettingtheISOControlregister(0x01). 24 DetailedDescription Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 Table6-6.CodingoftheISOControlRegister BIT SIGNALNAME FUNCTION COMMENTS 1=NoRXCRC B7 rx_crc_n ReceivingwithoutCRC 0=RXCRC 0=Outputissubcarrierdata B6 dir_mode Directmodetype 1=OutputisbitstreamandclockfromdecoderselectedbyISObits 0=RFIDreadermode B5 rfid RFIDmode 1=NFCorcardemulatormode RFID:Modeselection NFC: B4 iso_4 RFIDprotocol,NFCtarget 0=NFCtarget 1=NFCinitiator RFID:Modeselection(seeTable6-7) NFC: B3 iso_3 RFIDprotocol,NFCmode 0=Passivemode 1=Activemode RFID:Modeselection NFC: B2 iso_2 RFIDprotocol,CardEmulation 0=NFCnormalmodes 1=Cardemulationmode RFID:Modeselection B1 iso_1 RFIDprotocol,NFCbitrate NFC:BitrateselectionorCardEmulationselection(seeTable6-8) RFID:Modeselection B0 iso_0 RFIDprotocol,NFCbitrate NFC:BitrateselectionorCardEmulationselection(seeTable6-8) Copyright©2011–2017,TexasInstrumentsIncorporated DetailedDescription 25 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com Table6-7.CodingoftheISOControlRegisterForRFIDMode(B5=0) Iso_4 Iso_3 Iso_2 Iso_1 Iso_0 PROTOCOL REMARKS 0 0 0 0 0 ISO/IEC15693lowbitrate,onesubcarrier,1outof4 0 0 0 0 1 ISO/IEC15693lowbitrate,onesubcarrier,1outof256 0 0 0 1 0 ISO/IEC15693highbitrate,onesubcarrier,1outof4 DefaultforRFIDIC 0 0 0 1 1 ISO/IEC15693highbitrate,onesubcarrier,1outof256 0 0 1 0 0 ISO/IEC15693lowbitrate,doublesubcarrier,1outof4 0 0 1 0 1 ISO/IEC15693lowbitrate,doublesubcarrier,1outof256 0 0 1 1 0 ISO/IEC15693highbitrate,doublesubcarrier,1outof4 0 0 1 1 1 ISO/IEC15693highbitrate,doublesubcarrier,1outof256 0 1 0 0 0 ISO/IEC14443A,bitrate106kbps RXbitratewhenTXrate 0 1 0 0 1 ISO/IEC14443Ahighbitrate212kbps differentfromRXrate(see register0x03) 0 1 0 1 0 ISO/IEC14443Ahighbitrate424kbps 0 1 0 1 1 ISO/IEC14443Ahighbitrate848kbps 0 1 1 0 0 ISO/IEC14443B,bitrate106kbps RXbitratewhenTXrate 0 1 1 0 1 ISO/IEC14443Bhighbitrate212kbps differentfromRXrate(see register0x03) 0 1 1 1 0 ISO/IEC14443Bhighbitrate424kbps 0 1 1 1 1 ISO/IEC14443Bhighbitrate848kbps 1 0 0 1 1 Reserved 1 0 1 0 0 Reserved 1 1 0 1 0 FeliCa212kbps 1 1 0 1 1 FeliCa424kbps Table6-8.CodingoftheISOControlRegisterForNFC Mode(B5=1,B2=0)orCardEmulation(B5=1, B2=1) CARDEMULATION Iso_1 Iso_0 NFC(B5=1,B2=0) (B5=1,B2=1) 0 0 N/A ISO/IEC14443A 0 1 106kbps ISO/IEC14443B 1 0 212kbps N/A 1 1 424kbps N/A 26 DetailedDescription Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A www.ti.com SLOS743L–AUGUST2011–REVISEDMARCH2017 6.5.1 Received Signal Strength Indicator (RSSI) The TRF7970A incorporates in total three independent RSSI building blocks: Internal Main RSSI, Internal Auxiliary RSSI, and External RSSI. The internal RSSI blocks measure the amplitude of the subcarrier signal,andtheexternalRSSIblockmeasurestheamplitudeoftheRFcarriersignalatthereceiverinput. 6.5.1.1 InternalRSSI– MainandAuxiliaryReceivers Each receiver path has its own RSSI block to measure the envelope of the demodulated RF signal (subcarrier). Internal Main RSSI and Internal Auxiliary RSSI are identical however connected to different RFinputpins.TheInternalRSSIisintendedfordiagnosticpurposestosetthecorrectRXpathconditions. The internal RSSI values can be used to adjust the RX gain settings or determine which RX path (main or auxiliary) provides the greater amplitude and, hence, to determine if the MUX may need to be reprogrammed to swap the RX input signal. The measuring system latches the peak value, so the RSSI level can be read after the end of each receive packet. The RSSI register values are reset with every transmission(TX)bythereader.ThisensuresanupdatedRSSImeasurementforeachnewtagresponse. The Internal RSSI has 7 steps (3 bit) with a typical increment of approximately 4 dB. The operating range is between 600 mV and 4.2 V with a typical step size of approximately 600 mV. Both Internal Main PP PP andInternalAuxiliaryRSSIvaluesarestoredintheRSSILevelsandOscillatorStatusregister(0x0F).The nominalrelationshipbetweentheinputRFpeaklevelandtheRSSIvalueisshowninFigure6-5. F) 7 0 x 0 e ( alu 6 V er st gi 5 e R s u at 4 St or at cill 3 s O d an 2 s el v e SI L 1 S R 0 0 0.25 0.5 0.75 1 1.25 1.5 1.75 2 2.25 2.5 2.75 3 3.25 3.5 3.75 4 4.25 Input RF Carrier Level (V ) PP Figure6-5.DigitalInternalRSSI(MainandAuxiliary)ValuevsRFInputLevelinV (V) PP This RSSI measurement is done during the communication to the Tag; this means the TX must be on. Bit 1 in the Chip Status Control register (0x00) defines if Internal RSSI or the External RSSI value is stored in the RSSI Levels and Oscillator Status register (0x0F). Direct command 0x18 is used to trigger an Internal RSSImeasurement. 6.5.1.2 ExternalRSSI The external RSSI is mainly used to check for any external 13.56-MHz signals at the receiver RX_IN1 input. The external RSSI measurement should be used before turning on the transmitter to prevent RF field collisions. This is especially important for active mode, when both devices emit their own RF field. The level of the RF signal received at the antenna is measured and stored in the RSSI Levels and Oscillator Status register (0x0F). Figure 6-6 shows the relationship between the voltage at the RX_IN1 inputandthe3-bitcode. Copyright©2011–2017,TexasInstrumentsIncorporated DetailedDescription 27 SubmitDocumentationFeedback ProductFolderLinks:TRF7970A

TRF7970A SLOS743L–AUGUST2011–REVISEDMARCH2017 www.ti.com 0F) 7 x 0 e ( u al 6 V er st gi 5 e R s u at 4 St or at cill 3 s O d an 2 s el v e L 1 SI S R 0 0 25 50 75 100 125 150 175 200 225 250 275 300 325 RF Input Voltage Level at RF_IN1 (mV ) PP Figure6-6.DigitalExternalRSSIValuevsRFInputLevelinV (mV) PP The relation between the 3-bit code and the external RF field strength (A/m) sensed by the antenna must be determined by calculation or by experiments for each antenna design. The antenna Q-factor and connection to the RF input influence the result. Direct command 0x19 is used to trigger an external RSSI measurement. Forclarity,tochecktheinternalorexternalRSSIvalueindependentofanyotheroperation,theusermust: 1. Settransmittertodesiredstate(onoroff)usingBit5ofChipStatusControlregister(0x00)andenable receiverusingBit1. 2. CheckinternalorexternalRSSIusingdirectcommands0x18or0x19,respectively.Thisactionplaces theRSSIvalueintheRSSIregister. 3. Delayatleast50µs. 4. ReadtheRSSIregisterusingdirectcommand0x0F;valuesrangefrom0x40to0x7F. 5. Repeatsteps1to4asneeded.Theregisterisresetwhenitisread. 6.6 Oscillator Section The 13.56-MHz or 27.12-MHz crystal (or oscillator) is controlled by the Chip Status Control register (0x00) and the EN and EN2 terminals. The oscillator generates the RF frequency for the RF output stage as well as the clock source for the digital section. The buffered clock signal is available at pin 27 (SYS_CLK) for any other external circuits. B4 and B5 inside the Modulation and SYS_CLK register (0x09) can be used to dividetheexternalSYS_CLKsignalatpin27by1,2,or4. Typicalstart-uptimefromcompletepowerdownisintherangeof3.5ms. DuringPowerDownMode2(EN=0,EN2=1)thefrequencyofSYS_CLKisswitchedto60kHz(typical). Thecrystalneedstobeconnectedbetweenpin30andpin31.TheexternalshuntcapacitorsvaluesforC 1 andC mustbecalculatedbasedonthespecifiedloadcapacitanceofthecrystalbeingused.Theexternal 2 shunt capacitors are calculated as two identical capacitors in series plus the stray capacitance of the TRF7970AandparasiticPCBcapacitanceinparalleltothecrystal. The parasitic capacitance (C , stray and parasitic PCB capacitance) can be estimated at 4 to 5 pF S (typical). As an example, using a crystal with a required load capacitance (C ) of 18 pF, the calculation is shown in L Equation1. 28 DetailedDescription Copyright©2011–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:TRF7970A