ICGOO在线商城 > ISL9305IRTAANLZ-T

- 型号: ISL9305IRTAANLZ-T

- 制造商: Intersil

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ISL9305IRTAANLZ-T产品简介:

ICGOO电子元器件商城为您提供ISL9305IRTAANLZ-T由Intersil设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 提供ISL9305IRTAANLZ-T价格参考以及IntersilISL9305IRTAANLZ-T封装/规格参数等产品信息。 你可以下载ISL9305IRTAANLZ-T参考资料、Datasheet数据手册功能说明书, 资料中有ISL9305IRTAANLZ-T详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

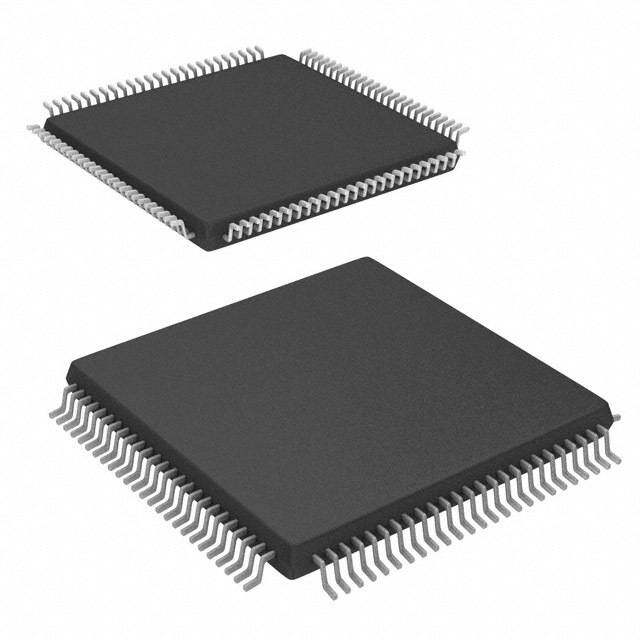

| 描述 | IC REG QD BUCK/LINEAR 16TQFN |

| 产品分类 | |

| 品牌 | Intersil |

| 数据手册 | |

| 产品图片 | |

| 产品型号 | ISL9305IRTAANLZ-T |

| PCN设计/规格 | |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | - |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=25476 |

| 供应商器件封装 | 16-TQFN-EP(4x4) |

| 其它名称 | ISL9305IRTAANLZ-TCT |

| 功能 | 任何功能 |

| 包装 | 剪切带 (CT) |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 16-WQFN 裸露焊盘 |

| 工作温度 | -40°C ~ 85°C |

| 带LED驱动器 | 无 |

| 带定序器 | 无 |

| 带监控器 | 无 |

| 拓扑 | 降压(降压)(2),线性(LDO)(2) |

| 标准包装 | 1 |

| 电压-电源 | 1.5 V ~ 5.5 V |

| 电压/电流-输出1 | 0.8 V ~ 5.5 V,800mA |

| 电压/电流-输出2 | 0.8 V ~ 5.5 V,800mA |

| 电压/电流-输出3 | 3.3V,350mA |

| 输出数 | 4 |

| 频率-开关 | 3MHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

DATASHEET ISL9305 FN7605 3MHz Dual Step-Down Converters and Dual Low-Input LDOs with I2C Compatible Rev 2.00 Interface February 9, 2015 The ISL9305 is an integrated mini Power Management IC Features (mini-PMIC) ideal for applications of powering low-voltage microprocessor or multiple voltage rails with battery as input • Dual 800mA, Synchronous Step-down Converters and Dual sources, such as a single Li-ion or Li-Polymer. ISL9305 300mA, General-purpose LDOs integrates two high-efficiency 3MHz synchronous step-down • Input Voltage Range converters (DCD1 and DCD2) and two low-input, low-dropout - DCD1/DCD2. . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.3V to 5.5V linear regulators (LDO1 and LDO2). - LDO1/LDO2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.5V to 5.5V The 3MHz PWM switching frequency allows the use of very small • 400kb/s I2C-bus Series Interface Transfers the Control Data external inductors and capacitors. Both step-down converters can Between the Host Controller and the ISL9305 enter skip mode under light load conditions to further improve the efficiency and maximize the battery life. For noise sensitive • Adjustable Output Voltage applications, they can also be programmed through I2C interface - VODCD1/VODCD2 . . . . . . . . . . . . . . . . . . . . . . . . 0.8V to VIN to operate in forced PWM mode regardless of the load current condition. The I2C interface supports on-the-fly slew rate control of • Fixed Output I2C Programmability the output voltage from 0.825V to 3.6V at 25mV/step size for - At 25mV/Step . . . . . . . . . . . . . . . . . . . . . . . .0.825V to 3.6V dynamic power saving. Each step-down converter can supply up to • LDO1/LDO2 Output Voltage I2C Programmability 800mA load current. The default output voltage can be set from - At 50mV/Step . . . . . . . . . . . . . . . . . . . . . . . . . . 0.9V to 3.6V 0.8V to VIN using external feedback resistors on the adjustable version, or the ISL9305 can be ordered in factory pre-set voltage • 50μA IQ (Typ) with DCD1/DCD2 in Skip Mode; 20μA IQ (Typ) options from 0.9V to 3.6V in 50mV step. for each Enabled LDO The ISL9305 also provides two 300mA low dropout (LDO) • On-the-fly I2C Programming of DC/DC and LDO Output regulators. The input voltage range is 1.5V to 5.5V allowing Voltages them to be powered from one of the on-chip step-down • DCD1/DCD2 I2C Programmable Skip Mode Under Light converters or directly from the battery. The default LDO Load or Forced Fixed Switching Frequency PWM Mode power-up output comes with factory pre-set fixed output • Small, Thin, 4mmx4mm TQFN Package voltage options between 0.9V to 3.3V. Applications The ISL9305 is available in a 4mmx4mm 16 Ld TQFN package. • Cellular Phones, Smart Phones Related Literature • PDAs, Portable Media Players, Portable Instruments •ISL9305H Data Sheet • Single Li-ion/Li-Polymer Battery-Powered Equipment •AN1564 “ISL9305 and ISL9305H Evaluation Boards” • DSP Core Power L1 = 1.5µH 800mA PG SW1 2.3V TO C5.150V VVIINNDDCCDD12 FB1 R1 R2* C4.47µF 10µF SDAT L2 = 1.5µH 800mA SW2 1.5V TO 5.5V C2 VSICNLLKDO1 ISL9305 FB2 R3 R4* C4.57µF 1µF 300mA 1.5V TO 5.5V VOLDO1 VINLDO2 300mA C3 VOLDO2 1µF GNDDCD1GNDDCD2GNDLDO C6 C7 1µF 1µF *Only for adjustable output version. For fixed output version, directly connect the FB pin to the output of the buck converter. FIGURE 1. TYPICAL APPLICATION DIAGRAM FN7605 Rev 2.00 Page 1 of 17 February 9, 2015

ISL9305 TABLE 1. TYPICAL APPLICATION PART LIST PARTS DESCRIPTION MANUFACTURER PART NUMBER SPECIFICATIONS SIZE L1, L2 Inductor Sumida CDRH2D14NP-1R5 1.5µH/1.80A/50mΩ 3.0mmx3.0mmx1.55mm C1 Input capacitor Murata GRM21BR60J106KE19L 10µF/6.3V 0805 C2, C3 Input capacitor Murata GRM185R60J105KE26D 1µF/6.3V 0603 C4, C5 Output capacitor Murata GRM219R60J475KE01D 4.7µF/6.3V 0805 C6, C7 Output capacitor Murata GRM185R60J105KE26D 1µF/6.3V 0603 R1, R2, Resistor Various 1%, SMD, 0.1Ω 0603 R3, R4 NOTE: 1. C4 and C5 are 10µF/6.3V for VODCD less than 1V. Block Diagram ANALOG/LOGIC SHORT CIRCUIT INPUT VINDCD1 DCDPG CIRCUIT PROTECTION 10µF 1.5µH SW1 DCD1 4.7µF FB1 BUCK CONVERTER PGOOD WITH GNDDCD1 1~200MS DELAY TIME OVERCURRENT VINDCD2 PROTECTION 10µF 1.5µH SW2 DCD2 4.7µF FB2 UVLO VREF BUCK CONVERTER GNDDCD2 OSC VINLDO1 THERMAL SHUTDOWN 1µF LDO1 VOLDO1 300mA 1µF SDAT I2C VINLDO2 INTERFACE SCLK 1µF LDO2 VOLDO2 300mA GNDLDO 1µF FN7605 Rev 2.00 Page 2 of 17 February 9, 2015

ISL9305 Pin Configuration ISL9305 (16 LD 4x4 TQFN) TOP VIEW 1 2 C D D C C D W1 ND ND W2 S G G S 16 15 14 13 VINDCD11 12VINDCD2 FB1 2 11FB2 E-PAD SCLK 3 10DCDPG SDAT 4 9GNDLDO 5 6 7 8 1 1 2 2 O O O O D D D D L L L L N O O N VI V V VI Pin Descriptions PIN NUMBER (TQFN) NAME DESCRIPTION 1 VINDCD1 Input voltage for buck converter DCD1 and it also serves as the power supply pin for the whole internal digital/ analog circuits. 2 FB1 Feedback pin for DCD1, connect external voltage divider resistors between DCDC1 output, this pin and ground. For fixed output versions, connect this pin directly to the DCD1 output. 3 SCLK I2C interface clock pin. 4 SDAT I2C interface data pin. 5 VINLDO1 Input voltage for LDO1. 6 VOLDO1 Output voltage of LDO1. 7 VOLDO2 Output voltage of LDO2. 8 VINLDO2 Input voltage for LDO2. 9 GNDLDO Power ground for LDO1 and LDO2. 10 DCDPG The DCDPG pin is an open-drain output to indicate the state of the DCD1/DCD2 output voltages. When both DCD1 and DCD2 are enabled, the output is released to be pulled high by an external pull-up resistor if both converter voltages are within the power-good range. The pin will be pulled low if either DCD is outside their range. When only one DCD is enabled, the state of the enabled DCD’s output will define the state of the DCDPG pin. The DCDPG state can be programmed for a delay of up to 200ms before being released to rise high. The programming range is 1ms~200ms through the I2C interface. 11 FB2 Feedback pin for DCD2, connect external voltage divider resistors between DCD2 output, this pin and ground. For fixed output versions, connect this pin directly to the DCD2 output. 12 VINDCD2 Input voltage for buck converter DCD2. 13 SW2 Switching node for DCD2, connect to one terminal of the inductor. 14 GNDDCD2 Power ground for DCD2. 15 GNDDCD1 Power ground for DCD1. 16 SW1 Switching node for DCD1, connect to one terminal of the inductor. E-pad E-pad Exposed Pad. Connect to system ground. FN7605 Rev 2.00 Page 3 of 17 February 9, 2015

ISL9305 Ordering Information FBSEL FBSEL SLV SLV PACKAGE PART NUMBER DCD1 DCD2 LDO1 LDO2 TEMP. RANGE Tape and Reel PKG. (Notes 1, 2, 3) PART MARKING (V) (V) (V) (V) (°C) (Pb-free) DWG. # ISL9305IRTAANLZ-T 9305I AANLZ Adj Adj 3.3 2.9 -40 to +85 16 Ld TQFN L16.4x4G ISL9305IRTBCNLZ-T 9305I BCNLZ 1.5 1.8 3.3 2.9 -40 to +85 16 Ld TQFN L16.4x4G ISL9305IRTBFNCZ-T 9305I BFNCZ 1.5 2.5 3.3 1.8 -40 to +85 16 Ld TQFN L16.4x4G ISL9305IRTWBNLZ-T 9305I WBNLZ 1.2 1.5 3.3 2.9 -40 to +85 16 Ld TQFN L16.4x4G ISL9305IRTWCLBZ-T 9305I WCLBZ 1.2 1.8 2.9 1.5 -40 to +85 16 Ld TQFN L16.4x4G ISL9305IRTWCNLZ-T 9305I WCNLZ 1.2 1.8 3.3 2.9 -40 to +85 16 Ld TQFN L16.4x4G ISL9305IRTWCNYZ-T 9305I WCNYZ 1.2 1.8 3.3 0.9 -40 to +85 16 Ld TQFN L16.4x4G ISL9305IRTWLNCZ-T 9305I WLNCZ 1.2 2.9 3.3 1.8 -40 to +85 16 Ld TQFN L16.4x4G ISL9305IRTAANLZEV1Z Evaluation Board ISL9305IRTBCNLZEV1Z Evaluation Board ISL9305IRTBFNCZEV1Z Evaluation Board ISL9305IRTWBNLZEV1Z Evaluation Board ISL9305IRTWCLBZEV1Z Evaluation Board ISL9305IRTWCNLZEV1Z Evaluation Board ISL9305IRTWCNYZEV1Z Evaluation Board ISL9305IRTWLNCZEV1Z Evaluation Board NOTES: 1. Please refer to TB347 for details on reel specifications. 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020. 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL9305. For more information on MSL please see techbrief TB363. FN7605 Rev 2.00 Page 4 of 17 February 9, 2015

ISL9305 Absolute Maximum Ratings Thermal Information (Refer to ground) SW1, SW2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -1.5V to 6.5V Thermal Resistance (Typical) JA (°C/W) JC (°C/W) FB1, FB2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to 3.6V 16 Ld TQFN Package (Notes 4, 5) . . . . . . . 40.2 5 GNDDCD1, GNDDCD2, GNDLDO. . . . . . . . . . . . . . . . . . . . . . . . -0.3V to 0.3V Maximum Junction Temperature Range. . . . . . . . . . . . . .-40°C to +150°C All other pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to 6.5V Recommended Junction Temperature Range . . . . . . . . .-40°C to +125°C ESD Ratings Storage Temperature Range. . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150°C Human Body Model (Tested per JESD22-A114F). . . . . . . . . . . . . . .3.5kV Pb-Free Reflow Profile . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . see TB493 Machine Model (Tested per JESD22-A115-A). . . . . . . . . . . . . . . . . 225V Charged Device Model (Tested per JESD22-C101D) . . . . . . . . . . . 2.2kV Recommended Operating Conditions Latch Up (Tested per JESD78B, Class II, Level A). . . . . . . . . . . . . . . 100mA VINDCD1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2.3V to 5.5V VINDCD2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2.3V to VINDCD1 VINLDO1 and VINLDO2 . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.5V to VINDCD1 DCD1 and DCD2 Output Current . . . . . . . . . . . . . . . . . . . . . 0mA to 800mA LDO1 and LDO2 Output Current. . . . . . . . . . . . . . . . . . . . . . 0mA to 300mA Operating Ambient Temperature . . . . . . . . . . . . . . . . . . . . .-40°C to +85°C CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty. NOTES: 4. JA is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See Tech Brief TB379. 5. JC, “case temperature” location is at the center of the exposed metal pad on the package underside. Electrical Specifications Unless otherwise noted, all parameter limits are guaranteed over the recommended operating conditions and the typical specifications are measured at the following conditions: TA = +25°C, VINDCD1 = 3.6V, VINDCD2 = 3.3V. For LDO1 and LDO2, VINLDOx=VOLDOx + 0.5V to 5.5V with VINLDOx always no higher than VINDCD1, L1=L2 = 1.5µH, C1 = 10µF, C4 = C5 = 4.7µF, C2=C3=C6=C7=1µF, IOUT=0A for DCD1, DCD2, LDO1 and LDO2 (seeFigure 1 on page1 for more details). Boldface limits apply over the operating temperature range, -40°C to +85°C. MIN MAX PARAMETER SYMBOL TEST CONDITIONS (Note 6) TYP (Note 6) UNIT VINDCD1, VINDCD2 Voltage Range 2.3 - 5.5 V VINDCD1, VINDCD2 Undervoltage VUVLO Rising - 2.2 2.3 V Lockout Threshold Falling 1.9 2.1 - V Quiescent Supply Current on VINDCD1 IVIN1 Only DCD1 enabled, no load and no switching - 40 60 µA on DCD1 IVIN2 Only DCD1 and LDO1 enabled, with no load and - 65 95 µA no switching on DCD1 IVIN3 Both DCD1 and DCD2 enabled, no load and no - 50 75 µA switching on both DCD1 and DCD2 IVIN4 Only LDO1 and LDO2 enabled - 75 100 µA IVIN5 DCD1, DCD2, LDO1 and LDO2 are enabled, - 100 130 µA with no load and no switching on both DCD1 and DCD2 IVIN6 Only one DCD in forced PWM mode, no load - 4 7.5 mA Shutdown Supply Current ISD VINDCD1 = 5.5V, DCD1, DCD2, LDO1 and LDO2 - 0.15 5 µA are disabled through I2C interface, VINDCD1=4.2V Thermal Shutdown - 155 - °C Thermal Shutdown Hysteresis - 30 - °C DCD1 AND DCD2 FB1, FB2 Regulation Voltage VFB 0.785 0.8 0.815 V FB1, FB2 Bias Current IFB FB = 0.75V - 0.001 - µA Output Voltage Accuracy VIN = VO + 0.5V to 5.5V (minimal 2.3V), -3 - +3 % 1mAload Line Regulation VIN = VO + 0.5V to 5.5V (minimal 2.3V) - 0.1 - %/V Maximum Output Current 800 - - mA FN7605 Rev 2.00 Page 5 of 17 February 9, 2015

ISL9305 Electrical Specifications Unless otherwise noted, all parameter limits are guaranteed over the recommended operating conditions and the typical specifications are measured at the following conditions: TA = +25°C, VINDCD1 = 3.6V, VINDCD2 = 3.3V. For LDO1 and LDO2, VINLDOx=VOLDOx + 0.5V to 5.5V with VINLDOx always no higher than VINDCD1, L1=L2 = 1.5µH, C1 = 10µF, C4 = C5 = 4.7µF, C2=C3=C6=C7=1µF, IOUT=0A for DCD1, DCD2, LDO1 and LDO2 (seeFigure 1 on page1 for more details). Boldface limits apply over the operating temperature range, -40°C to +85°C. (Continued) MIN MAX PARAMETER SYMBOL TEST CONDITIONS (Note 6) TYP (Note 6) UNIT P-Channel MOSFET ON-resistance VIN = 3.6V, IO = 200mA - 0.14 0.2 Ω VIN = 2.3V, IO = 200mA - 0.24 0.40 Ω N-Channel MOSFET ON-resistance VIN = 3.6V, IO = 200mA - 0.11 0.2 Ω VIN = 2.3V, IO = 200mA - 0.18 0.34 Ω P-Channel MOSFET Peak Current Limit IPK 1.075 1.3 1.6 A SW Maximum Duty Cycle - 100 - SW Leakage Current VIN = 5.5V - 0.005 1 µA PWM Switching Frequency fS 2.6 3.0 3.4 MHz SW Minimum ON-time VFB = 0.75V - 70 - ns Bleeding Resistor - 115 - Ω PG Output Low Voltage Sinking 1mA, FB1 = FB2 = 0.7V - - 0.25 V Rising Delay Time Based on 1ms programmed nominal delay 0.6 1.1 1.8 ms time Falling Delay Time Based on 1ms programmed nominal delay - 30 - µs time PG Pin Leakage Current PG = VINDCD1 = VINDCD2 = 3.6V - 0.005 0.1 µA PG Low Rising Threshold Percentage of nominal regulation voltage - 91 - % PG Low Falling Threshold Percentage of nominal regulation voltage - 87 - % PG High Rising Threshold Percentage of nominal regulation voltage - 112 - % PG High Falling Threshold Percentage of nominal regulation voltage - 109 - % LDO1 AND LDO2 VINLDO1, VINLDO2 Supply Voltage No higher than VINDCD1 1.5 - 5.5 V VINLDO1, VINLDO2 Undervoltage VUVLO VINDCD1 = 2.3V, Rising - 1.41 1.46 V Lock-out Threshold VINDCD1 = 2.3V, Falling 1.33 1.37 - V Internal Peak Current Limit 350 425 540 mA Dropout Voltage IO = 300mA, VO 2.1V - 125 250 mV IO = 300mA, 2.1V < VO 2.8V - 100 200 mV IO = 300mA, VO > 2.8V - 80 170 mV Power Supply Rejection Ratio IO= 300mA @ 1kHz, VIN = 3.6V, VO = 2.6V, - 55 - dB TA=+25°C Output Voltage Noise VIN = 4.2V, IO = 10mA, TA=+25°C, BW = 10Hz - 45 - µVRMS to 100kHz NOTE: 6. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. FN7605 Rev 2.00 Page 6 of 17 February 9, 2015

ISL9305 Theory of Operation crossing. When it is detected to cross zero for 16 consecutive cycles, the regulator enters the skip mode. During the 16 DCD1 and DCD2 Introduction consecutive cycles, the inductor current could be negative. The counter is reset to zero when the sensed current flowing through Both the DCD1 and DCD2 converters on ISL9305 use the the SW node does not cross zero during any cycle within the 16 peak-current-mode pulse-width modulation (PWM) control consecutive cycles. Once the converter enters the skip mode, the scheme for fast transient response and pulse-by-pulse current pulse modulation is controlled by an internal comparator while limiting. Both converters are able to supply up to 800mA load each pulse cycle remains synchronized to the PWM clock. The current. The default output voltage ranges from 0.8V to 3.6V P-Channel MOSFET is turned on at the rising edge of the clock depending on the factory pre-set configuration and can be and turned off when its current reaches ~20% of the peak programmed via the I2C interface in the range of 0.825V to 3.6V current limit. As the average inductor current in each cycle is at 25mV/step with a programmable slew rate. An open-drain higher than the average current of the load, the output voltage DCDPG (DCD Power-Good) signal is also provided to monitor the rises cycle-over-cycle. When the output voltage is sensed to reach DCD1 and DCD2 output voltages. Optionally, both DCD1 and 1.5% above its nominal voltage, the P-Channel MOSFET is turned DCD2 can be programmed to be actively discharged via an off immediately and the inductor current is fully discharged to on-chip bleeding resistor (typical 115Ω) when the converter is zero and stays at zero. The output voltage reduces gradually due disabled. to the load current discharging the output capacitor. When the output voltage drops to the nominal voltage, the P-Channel Skip Mode (PFM Mode) for DCD1/DCD2 MOSFET will be turned on again, repeating the previous Under light load condition, the DCD1 and DCD2 can be operations. programmed to automatically enter a pulse-skipping mode to The regulator resumes normal PWM mode operation when the minimize the switching loss by reducing the switching frequency. output voltage is sensed to drop below 1.5% of its nominal Figure 2 illustrates the skip mode operation. A zero-cross sensing voltage value as shown in Figure 3. circuit monitors the current flowing through the SW node for zero 16 CYCLES CLOCK 20% PEAK CURRENT LIMIT IL 0 1.015*VOUT_NOMINAL VOUT VOUT_NOMINAL FIGURE 2. SKIP MODE OPERATION WAVEFORMS v EAMP v CSA d i L v OUT FIGURE 3. PWM OPERATION WAVEFORMS FN7605 Rev 2.00 Page 7 of 17 February 9, 2015

ISL9305 Soft-Start switching regulation to maintain the output voltage, the P-Channel MOSFET is completely turned on (100% duty cycle). The soft-start reduces the in-rush current during the start-up stage. The dropout voltage under such a condition is the product of the The soft-start block limits the current rising speed so that the load current and the ON-resistance of the P-Channel MOSFET. output voltage rises in a controlled fashion. Minimum required input voltage VIN under such condition is the Overcurrent Protection sum of output voltage plus the voltage drop across the inductor and the P-Channel MOSFET switch. The overcurrent protection for DCD1 and DCD2 is provided on ISL9305 for when an overload condition occurs. When the Active Output Voltage Discharge For current at P-Channel MOSFET is sensed to reach the current limit, DCD1/DCD2 the internal protection circuit is triggered to turn off the P-Channel MOSFET immediately. The ISL9305 offers a feature to actively discharge the output voltage of DCD1 and DCD2 via an internal bleeding resistor (typical DCD Short-Circuit Protection 115Ω) when the channel is disabled. This feature is enabled by default, thus outputs can be disabled individually through The ISL9305 provides Short-Circuit Protection for both DCD1 and programming the control bit in DCD_PARAMETER register. DCD2. The feedback voltage is monitored for output short-circuit protection. When the output voltage is sensed to be lower than a Thermal Shutdown certain threshold, the internal circuit will change the PWM The ISL9305 provides built-in thermal protection function with oscillator frequency to a lower frequencies in order to protect the thermal shutdown threshold temperature set at +155°C with IC from damage. The P-Channel MOSFET peak current limit +25°C hysteresis (typical). When the die temperature is sensed remains active during this state. to reach +155°C, the regulator is completely shut down and as Undervoltage Lock-out (UVLO) the temperature is sensed to drop to +130°C (typical), the device resumes normal operation starting from the soft-start. An undervoltage lock-out (UVLO) circuit is provided on ISL9305. The UVLO circuit block can prevent abnormal operation in the Board Layout Recommendations event that the supply voltage is too low to guarantee proper operation. The UVLO on VINDCD1 is set for a typical 2.2V with The ISL9305 is a high frequency switching charger and hence the PCB layout is a very important design practice to ensure a 100mV hysteresis. VINLDO1 and VINLDO2 are set for a typical satisfactory performance. 1.4V with 50mV hysteresis. When the input voltage is sensed to be lower than the UVLO threshold, the related channel is disabled. The power loop is composed of the output inductor L, the output DCDPG (DCD Power-Good) capacitor COUT, the SW pin and the PGND pin. It is important to make the power loop as small as possible and the connecting ISL9305 offers an open-drain Power-Good signal with traces among them should be direct, short and wide; the same programmable delay time for monitoring the converters DCD1 practice should be applied to the connection of the VIN pin, the and DCD2 output voltages status. input capacitor CIN and PGND. When both DCD1 and DCD2 are enabled and their output voltages The switching node of the converter, the SW pin, and the traces are within the power-good window, an internal power-good signal connected to this node are very noisy, so keep the voltage is issued to turn off the open-drain MOSFET so the DCDPG pin feedback trace and other noise sensitive traces away from these voltage can be externally pulled high after a programmed delay noisy traces. time. If either DCD1 or DCD2 output voltages or both of them are The input capacitor should be placed as close as possible to the not within the power-good window, the DCDPG outputs an VIN pin. The ground of the input and output capacitors should be open-drain logic low signal after the programmed delay time. connected as close as possible as well. In addition, a solid ground When there is only one DCD converter (either DCD1 or DCD2) is plane is helpful for a good EMI performance. enabled, then the DCDPG only indicates the status of this active The ISL9305 employs a thermal enhanced TQFN package with DCD converter. For example, if only DCD1 converter is enabled an exposed pad. The exposed pad should be properly soldered on and DCD2 converter is disabled, when DCD1 output is within the thermal pad of the board in order to remove heat from the IC. The power-good window, internal power-good signal will be issued to thermal pad should be big enough for 9 vias as shown in turn off the open-drain MOSFET so the DCDPG pin voltage is Figure4. externally pulled high after the programmed delay time. If output voltage of DCD1 is outside the power-good window, the DCDPG outputs an open-drain logic low signal after the programmed delay time. It is similar when only DCD2 is enabled and DCD1 is disabled. When both converters are disabled, DCDPG always outputs the open-drain logic low signal. Low Dropout Operation Both DCD1 and DCD2 converters feature the low dropout operation to maximize the battery life. When the input voltage FIGURE 4. EXPOSED THERMAL PAD drops to a level that the converter can no longer operate under FN7605 Rev 2.00 Page 8 of 17 February 9, 2015

ISL9305 2 I C Compatible Interface specifications, here the value of Bit 0 determines the direction of the message (“0” means “write” and “1” means “read”). The ISL9305 offers an I2C compatible interface, using two pins: SCLK for the serial clock and SDAT for serial data respectively. MSB LSB According to the I2C specifications, a pull-up resistor is needed for the clock and data signals to connect to a positive supply. When 1 1 0 1 0 0 0 R/W the ISL9305 and the host use different supply voltages, the pull-up resistors should be connected to the higher voltage rail. BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 Signal timing specifications should satisfy the standard I2C bus specification. The maximum bit rate is 400kb/s and more details FIGURE 5. I2C SLAVE ADDRESS regarding the I2C specifications can be found from Philips. 2 2 I C Slave Address I C Protocol The ISL9305 serves as a slave device and the 7-bit default chip Figures 6, 7, and 8 show three typical I2C-bus transaction address is 1101000, as shown in Figure 5 According to the I2C protocols. S SLAVE ADDRESS 0 A REGISTER ADDRESS A DATA BYTE 1 A SYSTEM HOST R/W AUTO INCREMENT ISL9305 REGISTER ADDRESS OPTIONAL A – ACKNOWLEDGE N – NOT ACKNOWLEDGE S – START DATA BYTE 2 A DATA BYTE N A P P – STOP AUTO INCREMENT AUTO INCREMENT REGISTER ADDRESS REGISTER ADDRESS FIGURE 6. I2C WRITE S SLAVE ADDRESS 0 A REGISTER ADDRESS A S SLAVE ADDRESS 1 A SYSTEM HOST R/W R/W ISL9305 OPTIONAL A – ACKNOWLEDGE N – NOT ACKNOWLEDGE S – START DATA BYTE 1 A DATA BYTE 2 A DATA BYTE N N P P – STOP AUTO INCREMENT AUTO INCREMENT AUTO INCREMENT REGISTER ADDRESS REGISTER ADDRESS REGISTER ADDRESS FIGURE 7. I2C READ SPECIFYING REGISTER ADDRESS OPTIONAL S SLAVE ADDRESS 1 A DATA BYTE 1 A DATA BYTE 2 A DATA BYTE N N P R/W AUTO INCREMENT AUTO INCREMENT AUTO INCREMENT REGISTER ADDRESS REGISTER ADDRESS REGISTER ADDRESS SYSTEM HOST A – ACKNOWLEDGE N – NOT ACKNOWLEDGE ISL9305 S – START P – STOP FIGURE 8. I2C READ NOT SPECIFYING REGISTER ADDRESS FN7605 Rev 2.00 Page 9 of 17 February 9, 2015

ISL9305 2 I C Control Registers TABLE 2. BUCK CONVERTERS OUTPUT VOLTAGE CONTROL REGISTER All the registers are reset at initial start-up. BIT NAME ACCESS RESET DESCRIPTION B7 Reserve - 0 Refer to Table 3 DCD OUTPUT VOLTAGE CONTROL REGISTER B6 DCDxOUT-6 R/W 0 DCD1OUT, address 0x00h; DCD2OUT, address 0x01h B5 DCDxOUT-5 R/W 0 B4 DCDxOUT-4 R/W 1 B3 DCDxOUT-3 R/W 0 Refer to Table 3 B2 DCDxOUT-2 R/W 0 B1 DCDxOUT-1 R/W 0 B0 DCDxOUT-0 R/W 0 TABLE 3. DCD1 AND DCD2 OUTPUT VOLTAGE SETTING DCD OUTPUT DCD OUTPUT DCD OUTPUT DCD OUTPUT DCDOUT VOLTAGE DCDOUT VOLTAGE DCDOUT VOLTAGE DCDOUT VOLTAGE <7:0> (V) <7:0> (V) <7:0> (V) <7:0> (V) 00 0.825 20 1.625 40 2.425 60 3.225 01 0.850 21 1.650 41 2.450 61 3.250 02 0.875 22 1.675 42 2.475 62 3.275 03 0.900 23 1.700 43 2.500 63 3.300 04 0.925 24 1.725 44 2.525 64 3.325 05 0.950 25 1.750 45 2.550 65 3.350 06 0.975 26 1.775 46 2.575 66 3.375 07 1.000 27 1.800 47 2.600 67 3.400 08 1.025 28 1.825 48 2.625 68 3.425 09 1.050 29 1.850 49 2.650 69 3.450 0A 1.075 2A 1.875 4A 2.675 6A 3.475 0B 1.100 2B 1.900 4B 2.700 6B 3.500 0C 1.125 2C 1.925 4C 2.725 6C 3.525 0D 1.150 2D 1.950 4D 2.750 6D 3.550 0E 1.175 2E 1.975 4E 2.775 6E 3.575 0F 1.200 2F 2.000 4F 2.800 6F 3.600 10 1.225 30 2.025 50 2.825 11 1.250 31 2.050 51 2.850 12 1.275 32 2.075 52 2.875 13 1.300 33 2.100 53 2.900 14 1.325 34 2.125 54 2.925 15 1.350 35 2.150 55 2.950 16 1.375 36 2.175 56 2.975 17 1.400 37 2.200 57 3.000 18 1.425 38 2.225 58 3.025 19 1.450 39 2.250 59 3.050 1A 1.475 3A 2.275 5A 3.075 1B 1.500 3B 2.300 5B 3.100 1C 1.525 3C 2.325 5C 3.125 1D 1.550 3D 2.350 5D 3.150 1E 1.575 3E 2.375 5E 3.175 1F 1.600 3F 2.400 5F 3.200 FN7605 Rev 2.00 Page 10 of 17 February 9, 2015

ISL9305 LDO1 AND LDO2 OUTPUT VOLTAGE CONTROL TABLE 4. LDOX OUTPUT VOLTAGE CONTROL REGISTERS REGISTERS BIT NAME ACCESS RESET DESCRIPTION LDO1OUT, address 0x02h and LDO2OUT, address 0x03h. B7 Reserve - 0 Refer to Table 5 for output voltage B6 Reserve - 0 settings B5 LDOxOUT-5 R/W 0 B4 LDOxOUT-4 R/W 0 B3 LDOxOUT-3 R/W 1 B2 LDOxOUT-2 R/W 1 B1 LDOxOUT-1 R/W 0 B0 LDOxOUT-0 R/W 0 TABLE 5. LDOX OUTPUT VOLTAGE SETTINGS LDOOUT LDO OUTPUT LDOOUT LDO OUTPUT LDOOUT LDO OUTPUT LDOOUT LDO OUTPUT <7:0> VOLTAGE (V) <7:0> VOLTAGE (V) <7:0> VOLTAGE (V) <7:0> VOLTAGE (V) 00 0.90 10 1.70 20 2.50 30 3.30 01 0.95 11 1.75 21 2.55 31 3.35 02 1.00 12 1.80 22 2.60 32 3.40 03 1.05 13 1.85 23 2.65 33 3.45 04 1.10 14 1.90 24 2.70 34 3.50 05 1.15 15 1.95 25 2.75 35 3.55 06 1.20 16 2.00 26 2.80 36 3.60 07 1.25 17 2.05 27 2.85 08 1.30 18 2.10 28 2.90 09 1.35 19 2.15 29 2.95 0A 1.40 1A 2.20 2A 3.00 0B 1.45 1B 2.25 2B 3.05 0C 1.50 1C 2.30 2C 3.10 0D 1.55 1D 2.35 2D 3.15 0E 1.60 1E 2.40 2E 3.20 0F 1.65 1F 2.45 2F 3.25 DCD1 AND DCD2 CONTROL REGISTER DCD_PARAMETER, address 0x04h TABLE 6. DCD_PARAMETER REGISTER TABLE 6. DCD_PARAMETER REGISTER (Continued) BIT NAME ACCESS RESET DESCRIPTION BIT NAME ACCESS RESET DESCRIPTION B7 - - 0 Reserved B2 DCD1_BLD R/W 1 Selection of DCD1 for active output voltage discharge when disabled. B6 DCD_PHASE R/W 0 DCD1 and DCD2 PWM switch 0-disabled; 1-enabled. selection. 0-in phase; 1 to 180° out-of-phase. B1 DCD2_MODE R/W 1 Selection on DCD2 of auto PFM/PWM mode (=1) or forced B5 DCD2_ULTRA R/W 0 Ultrasonic feature under PFM mode PWM mode (=0). for DCD2. 0-disabled; 1-enabled. B0 DCD1_MODE R/W 1 Selection on DCD1 of auto B4 DCD1_ULTRA R/W 0 Ultrasonic feature under PFM mode PFM/PWM mode (=1) or forced for DCD1. 0-disabled; 1-enabled. PWM mode (=0). B3 DCD2_BLD R/W 1 Selection of DCD2 for active output voltage discharge when disabled. 0-disabled; 1-enabled. FN7605 Rev 2.00 Page 11 of 17 February 9, 2015

ISL9305 SYSTEM CONTROL REGISTER DCD OUTPUT VOLTAGE SLEW RATE CONTROL REGISTER SYS_PARAMETER, address 0x05h DCD_SRCTL, address 0x06h TABLE 7. SYS_PARAMETER REGISTER TABLE 8. BIT NAME ACCESS RESET DESCRIPTION BIT NAME ACCESS RESET DESCRIPTION B7 - - 0 Reserved B6 I2C_EN R/W 0 I2C function enable. B7 DCD2SR_2 R/W 0 DCD2 Slew Rate Setting, 0-disabled; 1-enabled DCD2SR[2:0]: B6 DCD2SR_1 R/W 0 000 to 0.225mV/µs B5 DCDPOR_1 R/W 1 DCDPOR Delay Time Setting, B5 DCD2SR_0 R/W 1 001 to 0.45mV/µs DCDPOR[1:0]: 010 to 0.90mV/µs B4 DCDPOR_0 R/W 0 00 to 1ms 011 to 1.8mV/µs 01 to 50ms 100 to 3.6mV/µs 10 to 150ms 101 to 7.2mV/µs 11 to 200m 110 to 14.4mV/µs 111 to 28.8mV/µs B3 LDO2_EN R/W 1 LDO2 enable selection. 0-disable, 1-enable. B4 Reserve - 0 Reserved B2 LDO1_EN R/W 1 LDO1 enable selection. B3 DCD1SR_2 R/W 0 DCD1 Slew Rate Setting, 0-disable, 1-enable DCD1SR[2:0]: B2 DCD1SR_1 R/W 0 B1 DCD2_EN R/W 1 DCD2 enable selection. 000 to 0.225mV/µs 0-disable, 1-enable. B1 DCD1SR_0 R/W 1 001 to 0.45mV/µs 010 to 0.90mV/µs B0 DCD1_EN R/W 1 DCD1 enable selection. 011 to 1.8mV/µs 0-disable, 1-enable 100 to 3.6mV/µs 101 to 7.2mV/µs 110 to 14.4mV/µs 111 to 28.8mV/µs B0 Reserve - 0 Reserved FN7605 Rev 2.00 Page 12 of 17 February 9, 2015

ISL9305 Typical Operating Conditions VODCD1(20mV/DIV, AC-COUPLING) VODCD1(20mV/DIV, AC-COUPLING) IL1 (500mA/DIV) SW2(5V/DIV) VODCD2(20mV/DIV, AC-COUPLING) VODCD2(20mV/DIV, AC-COUPLING) SW1(5V/DIV) IL2 (500mA/DIV) FIGURE 9. DCD OUTPUT VOLTAGE RIPPLE (VIN = 4.2V, FULL LOAD AT FIGURE 10. DCD OUTPUT VOLTAGE RIPPLE (VIN = 4.2V, PFM MODE) DCD1 AND DCD2) VODCD1 (100mV/DIV VOLDO1 (100mV/DIV VODCD2 (10mV/DIV) VOLDO2 (10mV/DIV) IOUT_LDO1 (200mA/DIV IOUT_VODCD1 (500mA/DIV FIGURE 11. DCD OUTPUT TRANSIENT RESPONSE (VIN=4.2V, LOAD FIGURE 12. LDO OUTPUT TRANSIENT RESPONSE (VIN=4.2V, STEP STEP: 80mA TO 800mA) LOAD: 30mA TO 300mA) IL2 (200mA/DIV) VODCD1 (2V/DIV) VODCD2 (1V/DIV) IL1 (200mA/DIV) SW1 (5V/DIV) VOLDO1 (1V/DIV) VOLDO2 (2V/DIV) SW2 (5V/DIV) FIGURE 13. START-UP SEQUENCE (VIN = 4.2V, NO LOAD) FIGURE 14. DCD1 AND DCD2 SWITCHING WAVEFORM (VIN = 5V, FULL LOAD ON TWO CHANNELS) FN7605 Rev 2.00 Page 13 of 17 February 9, 2015

ISL9305 Typical Operating Conditions (Continued) 1.83 1.23 1.82 1.22 E (V) 1.81 E (V) 1.21 G G TA 1.80 TA L L O O 1.20 T V 1.79 VIN = 5.5V T V VIN = 5.5V VIN = 3.6V UTPU 1.78 VIN = 3.6V VIN = 2.8V UTPU 1.19 VIN = 2.8V O O 1.18 1.77 1.76 1.17 1 10 100 1000 10000 1 10 100 1000 10000 OUTPUT CURRENT (mA) OUTPUT CURRENT (mA) FIGURE 15. DCD OUTPUT VOLTAGE vs LOAD (VOUT = 1.8V, FIGURE 16. DCD OUTPUT VOLTAGE vs LOAD (VOUT = 1.2V, PFM/PWM) PFM/PWM) 100 100 90 90 VIN = 2.8V 80 VIN = 2.8V 80 70 70 CY (%) 60 VIN = 3.6V VIN = 5.5V CY (%) 60 VIN = 3.6V VIN = 5.5V N 50 N 50 EFFICIE 3400 EFFICIE 3400 20 20 10 10 0 0 0.1 1 10 100 1k 0.1 1 10 100 1k OUTPUT CURRENT (mA) OUTPUT CURRENT (mA) FIGURE 17. EFFICIENCY vs OUTPUT CURRENT (VOUT=1.8V, FORCED FIGURE 18. EFFICIENCY vs OUTPUT CURRENT (VOUT=1.8V, PFM PWM MODE) TOPWM) 70 58 56 B) 60 +85°C ATIO (d 50 NT (µA) 5524 R E N 40 RR 50 O U ECTI 30 PSRR NT C 48 +25°C E REJ 20 ESCE 46 -40°C RIPPL 10 VVIONU =T 3=. 62V.6V QUI 4424 VDOC D=1 1 =.2 DVCD2 = NO SWITCHING, NO LOAD LOAD = 300mA LDO1 = LDO2 = DISABLED 0 40 0.1 1 10 100 1000 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 FREQUENCY (kHz) INPUT VOLTAGE (V) FIGURE 19. RIPPLE REJECTION RATIO vs FREQUENCY FIGURE 20. QUIESCENT CURRENT vs INPUT VOLTAGE FN7605 Rev 2.00 Page 14 of 17 February 9, 2015

ISL9305 Revision History The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev. DATE REVISION CHANGE February 9, 2015 FN7605.2 page5, Abs Max Rating, ESD Ratings, change from: Machine Model (Tested per JESD22-A115-A) . . . . . . . . . . 2.2kV Charged Device Model (Tested per JESD22-C101D) . . . . 225V to: Machine Model (Tested per JESD22-A115-A) . . . . . . . . . . 225V Charged Device Model (Tested per JESD22-C101D) . . . . 2.2kV page1 - Changed Related Literature AN1564 title from “ISL9305IRTZEVAL1Z and ISL9305HIRTZEVAL1Z Evaluation Boards” to “ISL9305 and ISL9305H Evaluation Boards” page1 - Changed “the ISL9305 can be ordered in factory pre-set power-up default voltages in increments of 100mV from 0.9V to 3.6V.” to “the ISL9305 can be ordered in factory pre-set output voltage options from 0.9V to 3.6V in 50mV step.” page1 Features - Changed “at 50mV/Step.....0.9V to 3.3V” to “50mV/Step.......0.9V to 3.6V” under LDO1/LDO2 output voltage I2C programmability. page2 - Change the output capacitor value at VOLDO1 and VOLDO2 from "10µF" to "1µF" in the block diagram. page4 - Changed Eval Board part numbers in Ordering Information table from “ISL9305IRTBCNLZEV1Z, ISL9305IRTBFNCZEV1Z, ISL9305IRTAANLZEV1Z” to “ISL9305IRTAANLZEV1Z, ISL9305IRTBCNLZEV1Z, ISL9305IRTBFNCZEV1Z, ISL9305IRTWBNLZEV1Z, ISL9305IRTWCLBZEV1Z, ISL9305IRTWCNLZEV1Z, ISL9305IRTWCNYZEV1Z, ISL9305IRTWLNCZEV1Z” page12 - Removed PCN “Note 7” under Table 8. Changed “111 to reserve for system use” to “111 to 28.8mV/µs. Changed “DCD2” to “DCD1” in line B0 of Table 7. May 25, 2011 FN7605.1 - Table 8 on page12 changed 111 description from “to immediate” to “reserved for system use (Note 7).” Added Note to Table 8, which reads "The IC can be damaged when output is programmed from high to low and the slew rate register is set to 111." - Changed ordering information EVAL Board name from ISL9305IRTZEVAL1Z to three separate ones ISL9305IRTBCNLZEV1Z ISL9305IRTBFNCZEV1Z ISL9305IRTAANLZEV1Z - Corrected Theta JA Thermal Information on page5 for TQFN from 42 to 40.2 - “Electrical Specifications” on page5: Added "Boldface limits apply over the operating temperature range, -40°C to +85°C." to common conditions. Bolded applicable specs. - Changed “Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.” note in Electrical Spec Table on page6 to “Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.” per Product Line decision. - Changed text under Figure 15, from "VOUT = 1.2V" to "VOUT = 1.8V." November 8, 2010 FN7605.0 Initial Release FN7605 Rev 2.00 Page 15 of 17 February 9, 2015

ISL9305 About Intersil Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets. For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at www.intersil.com. You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask. Reliability reports are also available from our website at www.intersil.com/support © Copyright Intersil Americas LLC 2010-2015. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners. For additional products, see www.intersil.com/en/products.html Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at www.intersil.com/en/support/qualandreliability.html Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries. For information regarding Intersil Corporation and its products, see www.intersil.com FN7605 Rev 2.00 Page 16 of 17 February 9, 2015

ISL9305 Package Outline Drawing L16.4x4G 16 LEAD THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 0, 4/10 4X 1.95 4.00 A 12X 0.65 6 B 13 16 PIN #1 INDEX AREA 6 PIN 1 INDEX AREA 12 1 00 2 . 10 ± 0 . 10 4. 9 4 (4X) 0.15 8 5 0.10M C AB TOP VIEW 16X 0 . 50 ± 0 . 1 4 0.30 ± 0.05 BOTTOM VIEW SEE DETAIL "X" 0.10C C 0.75 BASE PLANE SEATING PLANE 0.08C SIDE VIEW ( 3 . 6 TYP ) ( 2 . 10 ) ( 12X 0 . 65 ) C 0 . 2 REF 5 ( 16X 0 . 30 ) ( 16 X 0 . 70 ) 0 . 00 MIN. 0 . 05 MAX. TYPICAL RECOMMENDED LAND PATTERN DETAIL "X" NOTES: 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only. 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994. 3. Unless otherwise specified, tolerance : Decimal ± 0.05 4. Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip. 5. Tiebar shown (if present) is a non-functional feature. 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature. 7. JEDEC reference drawing: MO220K. FN7605 Rev 2.00 Page 17 of 17 February 9, 2015

Mouser Electronics Authorized Distributor Click to View Pricing, Inventory, Delivery & Lifecycle Information: R enesas Electronics: ISL9305IRTAANLZ-T ISL9305IRTBCNLZ-T ISL9305IRTBFNCZ-T ISL9305IRTWBNLZ-T ISL9305IRTWCLBZ-T ISL9305IRTWCNLZ-T ISL9305IRTWCNYZ-T ISL9305IRTWLNCZ-T ISL9305IRTHWCNYZ-T7A

Datasheet下载

Datasheet下载