ICGOO在线商城 > 集成电路(IC) > 时钟/计时 - 实时时钟 > DS1338U-33+T&R

- 型号: DS1338U-33+T&R

- 制造商: Maxim

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

DS1338U-33+T&R产品简介:

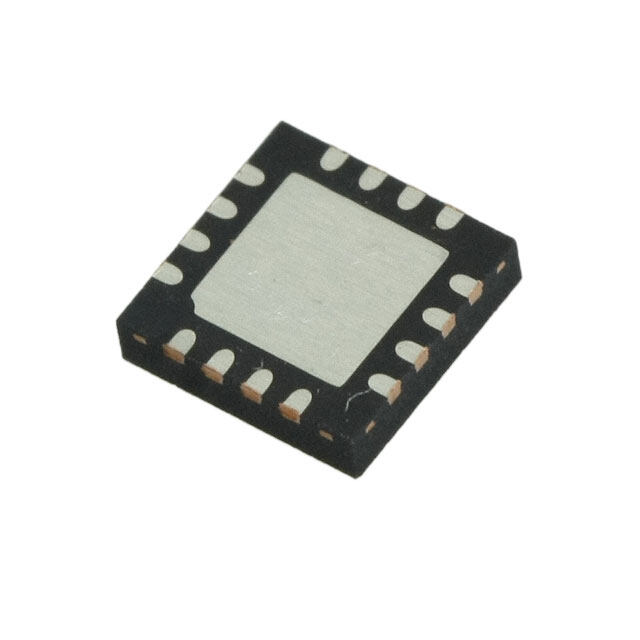

ICGOO电子元器件商城为您提供DS1338U-33+T&R由Maxim设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 DS1338U-33+T&R价格参考。MaximDS1338U-33+T&R封装/规格:时钟/计时 - 实时时钟, Real Time Clock (RTC) IC Clock/Calendar 56B I²C, 2-Wire Serial 8-TSSOP, 8-MSOP (0.118", 3.00mm Width)。您可以下载DS1338U-33+T&R参考资料、Datasheet数据手册功能说明书,资料中有DS1338U-33+T&R 详细功能的应用电路图电压和使用方法及教程。

Maxim Integrated的DS1338U-33+T&R是一款I²C接口的实时时钟(RTC)芯片,采用微型8引脚µSOP封装,适用于对空间和功耗敏感的应用场景。该器件内置晶振、电池备份输入端口及时间/日期功能模块,可在主电源断电时由备用电池维持时钟持续运行。 典型应用场景包括便携式设备(如智能手表、手持终端)、消费类电子产品(如机顶盒、家用电器)、工业控制系统、医疗仪器以及通信设备等需要精确时间记录和低功耗运行的系统。其工作电压为2.7V至3.7V,适合3.3V供电环境,集成度高,外围电路简单,有助于减少PCB面积并提升系统可靠性。 此外,DS1338U-33+T&R支持I²C总线通信,便于与微控制器连接,广泛用于需长时间稳定计时且要求小型化设计的嵌入式系统中。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC RTC CLK/CALENDAR I2C 8-USOP实时时钟 I2C Serial RTC w/56 Byte NV RAM |

| 产品分类 | |

| 品牌 | Maxim Integrated |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 时钟和计时器IC,实时时钟,Maxim Integrated DS1338U-33+T&R- |

| 数据手册 | |

| 产品型号 | DS1338U-33+T&R |

| RTC存储容量 | 56 B |

| RTC总线接口 | Serial |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=25703http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=25705 |

| 产品种类 | |

| 供应商器件封装 | 8-uMAX |

| 其它名称 | DS1338U-33+T&RDKR |

| 功能 | Clock, Calendar |

| 包装 | Digi-Reel® |

| 商标 | Maxim Integrated |

| 存储容量 | 56B |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | 8-TSSOP,8-MSOP(0.118",3.00mm 宽) |

| 封装/箱体 | uSOP |

| 工作温度 | -40°C ~ 85°C |

| 工厂包装数量 | 3000 |

| 应用说明 | 点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet点击此处下载产品Datasheet |

| 接口 | I²C,2 线串口 |

| 日期格式 | YY-MM-DD-dd |

| 时间格式 | HH:MM:SS |

| 最大工作温度 | + 85 C |

| 最小工作温度 | - 40 C |

| 标准包装 | 1 |

| 特性 | 闰年,NVSRAM,方波输出 |

| 电压-电源 | 3 V ~ 5.5 V |

| 电压-电源,电池 | 1.3 V ~ 3.7 V |

| 电流-计时(最大) | 125µA ~ 200µA @ 3.63V ~ 5.5V |

| 电源电压-最大 | 5.5 V |

| 电源电压-最小 | 3 V |

| 类型 | 时钟/日历 |

| 系列 | DS1338U |

| 零件号别名 | 90-1338U+33T DS1338U |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

DS1338 I2C RTC with 56-Byte NV RAM GENERAL DESCRIPTION BENEFITS AND FEATURES The DS1338 serial real-time clock (RTC) is a low- • Completely Manages All Timekeeping power, full binary-coded decimal (BCD) Functions clock/calendar plus 56 bytes of NV SRAM. Address RTC Counts Seconds, Minutes, Hours, o and data are transferred serially through an I2C Date of the Month, Month, Day of the interface. The clock/calendar provides seconds, Week, and Year with Leap-Year minutes, hours, day, date, month, and year Compensation Valid Up to 2100 information. The end of the month date is 56-Byte, Battery-Backed, General- o automatically adjusted for months with fewer than 31 Purpose RAM with Unlimited Writes days, including corrections for leap year. The clock Programmable Square-Wave Output o operates in either the 24-hour or 12-hour format with Signal AM/PM indicator. The DS1338 has a built-in power- • Surface-Mount Package with an Integrated sense circuit that detects power failures and Crystal (DS1338C) Saves Additional Space automatically switches to the backup supply, and Simplifies Design maintaining time and date operation • Interfaces with Most Microcontrollers APPLICATIONS I2C Serial Interface o Handhelds (GPS, POS Terminal) • Low-Power Operation Extends Battery Consumer Electronics (Set-Top Box, Digital Backup Run Time Recording, Network Appliance) Automatic Power-Fail Detect and Switch o Office Equipment (Fax/Printer, Copier) Circuitry Medical (Glucometer, Medicine Dispenser) Telecommunications (Router, Switcher, Server) • -40°C to +85°C Industrial Temperature Range Other (Utility Meter, Vending Machine, Thermostat, Supports Operation in a Wide Range of Modem) Applications • Underwriters Laboratories (UL®) Recognized UL is a registered trademark of Underwriters Laboratories Inc. ORDERING INFORMATION PART TEMP RANGE PIN-PACKAGE TOP MARK† DS1338Z-18+ -40°C to +85°C 8 SO (0.150″) DS1338-18 DS1338Z-3+ -40°C to +85°C 8 SO (0.150″) DS1338-3 TYPICAL OPERATING CIRCUIT DS1338Z-33+ -40°C to +85°C 8 SO (0.150″) DS133833 1338 R PU = tr / Cb VC C CRYSTAL V CC DDSS11333388UU--138++ --4400°°CC ttoo ++8855°°CC 88 µµSSOOPP r1rrr3--1338 8 VC C RP U RP U DS1338U-33+ -40°C to +85°C 8 µSOP 1338 rr-33 DS1338C-18# -40°C to +85°C 16 SO (0.300″) DS1338C-18 X1 X2 V CC DS1338C-3# -40°C to +85°C 16 SO (0.300″) DS1338C-3 SCL SQW/OUT i DS1338C-33# -40°C to +85°C 16 SO (0.300″) DS1338C-33 CPU DS1338 rr = second line, revision level + Denotes a lead(Pb)-free/RoHS-compliant device. SDA VB AT # Denotes a RoHS-compliant device that may include lead that is GND exempt under the RoHS requirements. The lead finish is JESD97 category e3, and is compatible with both lead-based and lead-free soldering processes. † A “+” anywhere on the top mark denotes a lead-free device. A “#” Pin Configurations appear at end of data sheet. denotes a RoHS-compliant device. 19-6019; Rev 4/15 1 of 16

ABSOLUTE MAXIMUM RATINGS Voltage Range on Any Pin Relative to Ground………………………………………………………..……..-0.3V to +6.0V Operating Temperature Range…………………………………………………………………………..……-40°C to +85°C Storage Temperature Range………………………………………………………………………………...-55°C to +125°C Lead Temperature (soldering, 10s) ……….………………………………………………………………………. +260°C Soldering Temperature (reflow) ……………………………………………………………………………………. +260°C Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability. RECOMMENDED DC OPERATING CONDITIONS (VCC = VCC(MIN) to VCC(MAX), TA = -40°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C, unless otherwise noted.) (Note 1) PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS DS1338-18 1.71 1.8 5.5 Supply Voltage VCC DS1338-3 2.7 3.0 5.5 V DS1338-33 3.0 3.3 5.5 Logic 1 VIH (Note 2) 0V.7C Cx V0C.C3 + V +0.3 x Logic 0 VIL (Note 2) -0.3 VCC V DS1338-18 1.51 1.62 1.71 Power-Fail Voltage VPF DS1338-3 2.45 2.59 2.70 V DS1338-33 2.70 2.82 2.97 VBAT Input Voltage VBAT (Note 2) 1.3 3.0 3.7 V DC ELECTRICAL CHARACTERISTICS (VCC = VCC(MIN) to VCC(MAX), TA = -40°C to +85°C, unless otherwise noted. Typical values are at VCC = TYP, TA = +25°C, unless otherwise noted.) (Note 1) PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS Input Leakage ILI (Note 3) 1 µA I/O Leakage ILO (Note 4) 1 µA VCC > 2V; VOL = 0.4V 3.0 SDA Logic 0 Output IOLSDA mA VCC < 2V; VOL = 0.2 x VCC 3.0 VCC > 2V; VOL = 0.4V 3.0 1.71V < VCC < 2V; 3.0 mA SQW/OUT Logic 0 Output IOLSQW VOL = 0.2 x VCC 1.3V < VCC < 1.71V; 250 µA VOL = 0.2 x VCC DS1338-18: VCC = 1.89V 75 150 A(Ncotitvee 5 S) upply Current ICCA DS1338-3: VVCCCC == 33..3603VV 111200 220000 µA DS1338-33 VCC = 5.5V 325 DS1338-18: VCC = 1.89V 60 100 Standby Current (Note 6) ICCS DS1338-3: VCC = 3.30V 80 125 µA VCC = 3.63V 85 125 DS1338-33 VCC = 5.5V 200 (VVBCACT LAecatikvaeg) e Current IBATLKG 25 100 nA 2 of 16

DS1338 DC ELECTRICAL CHARACTERISTICS (VCC = 0V, TA = -40°C to +85°C, unless otherwise noted. Typical values are at VBAT = 3.0V, TA = +25°C, unless otherwise noted.) (Note 1) PARAMETER SYMBOL MIN TYP MAX UNITS VBAT Current (OSC ON); VBAT = 3.7V, SQW/OUT OFF (Note 7) IBATOSC1 800 1200 nA (VNBoATte C 7u)r rent (OSC ON); VBAT = 3.7V, SQW/OUT ON (32kHz) IBATOSC2 1025 1400 nA VBAT Data-Retention Current (Osc Off); VBAT = 3.7V (Note 7) IBATDAT 10 100 nA AC ELECTRICAL CHARACTERISTICS (VCC = VCC(MIN) to VCC(MAX), TA = -40°C to +85°C) (Note 1) PARAMETER SYMBOL CONDITION MIN TYP MAX UNITS Fast mode 100 400 SCL Clock Frequency fSCL kHz Standard mode 0 100 Bus Free Time Between STOP Fast mode 1.3 and START Condition tBUF Standard mode 4.7 µs Fast mode 0.6 Hold Time (Repeated) START Condition (Note 8) tHD:STA Standard mode 4.0 µs Fast mode 1.3 LOW Period of SCL Clock tLOW µs Standard mode 4.7 Fast mode 0.6 HIGH Period of SCL Clock tHIGH µs Standard mode 4.0 Fast mode 0.6 Setup Time for Repeated START Condition tSU:STA Standard mode 4.7 µs Fast mode 0 0.9 Data Hold Time (Notes 9, 10) tHD:DAT µs Standard mode 0 Fast mode 100 Data Setup Time (Note 11) tSU:DAT ns Standard mode 250 Rise Time of Both SDA and Fast mode 20 + 0.1CB 300 SCL Signals (Note 12) tR ns Standard mode 20 + 0.1CB 1000 Fall Time of Both SDA and Fast mode 20 + 0.1CB 300 SCL Signals (Note 12) tF Standard mode 20 + 0.1CB 300 ns Setup Time for STOP Fast mode 0.6 Condition tSU:STO Standard mode 4.0 µs Capacitive Load for Each Bus Line CB (Note 12) 400 pF I/O Capacitance (SDA, SCL) CI/O (Note 13) 10 pF Oscillator Stop Flag (OSF) tOSF (Note 14) 100 ms Delay 3 of 16

DS1338 POWER-UP/POWER-DOWN CHARACTERISTICS (TA = -40°C to +85°C) (Note 1, Figure 1) PARAMETER SYMBOL MIN TYP MAX UNITS Recovery at Power-Up (Note 15) tREC 2 ms VCC Fall Time; VPF(MAX) to VPF(MIN) tVCCF 300 µs VCC Rise Time; VPF(MIN) to VPF(MAX) tVCCR 0 µs Warning: Negative undershoots below -0.3V while the part is in battery-backed mode may cause loss of data. Note 1: Limits at -40°C are guaranteed by design and not production tested. Note 2: All voltages are referenced to ground. Note 3: SCL only. Note 4: SDA and SQW/OUT. Note 5: ICCA—SCL clocking at max frequency = 400kHz. Note 6: Specified with the I2C bus inactive. Note 7: Measured with a 32.768kHz crystal attached to X1 and X2. Note 8: After this period, the first clock pulse is generated. Note 9: A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the VIH(MIN) of the SCL signal) to bridge the undefined region of the falling edge of SCL. Note 10: The maximum tHD:DAT need only be met if the device does not stretch the LOW period (tLOW) of the SCL signal. Note 11: A fast-mode device can be used in a standard-mode system, but the requirement tSU:DAT ≥ to 250ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line tR(MAX) + tSU:DAT = 1000 + 250 = 1250ns before the SCL line is released. Note 12: CB—total capacitance of one bus line in pF. Note 13: Guaranteed by design. Not production tested. Note 14: The parameter tOSF is the time period the oscillator must be stopped for the OSF flag to be set over the voltage range of 0.0V ≤ VCC ≤ VCC(MAX) and 1.3V ≤ VBAT ≤ 3.7V. Note 15: This delay applies only if the oscillator is enabled and running. If the oscillator is disabled or stopped, no power-up delay occurs. Figure 1. Power-Up/Power-Down Timing V PF(MVACXC ) VP F(MIN) t VCCF t VCCR t REC INPUTS RECOGNIZED DON'T CARE RECOGNIZED HIGH-Z OUTPUTS VALID VALID 4 of 16

DS1338 Figure 2. Timing Diagram Figure 3. Block Diagram SQW/OUT X1 1Hz/4.096kHz/8.192kHz/32.768kHz MUX/ CL BUFFER N 1Hz X2 C L Oscillator "C" VERSION ONLY and divider RAM (56 X 8) CONTROL V CC LOGIC POWER GND CONTROL CLOCK, CALENDAR, V BAT AND CONTROL DS1338 REGISTERS SCL SERIAL BUS INTERFACE AND ADDRESS USER BUFFER SDA REGISTER (7 BYTES) 5 of 16

DS1338 TYPICAL OPERATING CHARACTERISTICS IBAT vs. VBAT VCC=0V ICC vs. VCC RS1=RS0=1 250 1250 SCL=400kHz 1200 225 1150 1100 IBATOSC2 200 SUPPLY CURRENT (nA11007889905505050000000 (SQWE = 1) (SIQBAWTOES C=1 0) SUPPLY CURRENT (uA111257505 SCL=SDA=0Hz 100 700 650 75 600 550 50 1.3 1.8 2.3 2.8 3.3 3.8 4.3 4.8 5.3 1.8 2.3 2.8 3.3 3.8 4.3 4.8 5.3 VBAT (V) VCC (V) IBAT vs. Temperature VCC=0V Oscillator Frequency vs. Supply Voltage VBAT = 3.0V 1000 32768.5 950 SQWE=1 32768.4 900 NT (nA 850 Y (Hz)32768.3 E C URR 800 SQWE=0 UEN C Q PPLY 750 FRE32768.2 U S 700 32768.1 650 32768.0 600 1.3 1.8 2.3 2.8 3.3 3.8 4.3 4.8 -40 -20 0 20 40 60 80 Oscillator Supply Voltage (V) TEMPERATURE (°C) 6 of 16

DS1338 PIN DESCRIPTION PIN NAME FUNCTION 8 16 32.768kHz Crystal Connections. The internal oscillator circuitry is designed for 1 — X1 operation with a crystal having a specified load capacitance (CL) of 12.5pF. An external 32.768kHz oscillator can also drive the DS1338. In this configuration, the X1 pin is connected to the external oscillator signal and the X2 pin is left unconnected. 2 — X2 Note: For more information about crystal selection and crystal layout considerations, refer to Application Note 58: Crystal Considerations with Dallas Real-Time Clocks. Backup Supply Input for Lithium Cell or Other Energy Source. Battery voltage must be held between the minimum and maximum limits for proper operation. 3 14 VBAT Dprieovdeenst pplraocpeedr ionp seerraietios nb.e Itfw ae beanc tkhuep b saucpkpulpy isso nuorct ere aqnudir ethde, VVBBAATT mpinu smt baey grounded. UL recognized to ensure against reverse charging when used with a lithium cell. For more information, visit www.maxim-ic.com/qa/info/ul. Ground. DC power is provided to the device on these pins. VCC is the primary power input. When voltage is applied within normal limits, the device is fully accessible and data can be written and read. When a backup supply is 4 15 GND connected to the device and VCC is below VPF, reads and writes are inhibited. However, the timekeeping function continues unaffected by the lower input voltage. Serial Data. Input/output pin for the I2C serial interface. It is an open drain 5 16 SDA output and requires an external pullup resistor. The pull up voltage may be up to 5.5V regardless of the voltage on VCC. Serial Clock. Input pin for the I2C serial interface. Used to synchronize data 6 1 SCL movement on the serial interface. The pull up voltage may be up to 5.5V regardless of the voltage on VCC. Square-Wave/Output Driver. When enabled and the SQWE bit set to 1, the SQW/OUT pin outputs one of four square-wave frequencies (1Hz, 4kHz, 8kHz, 32kHz). It is an open drain output and requires an external pullup resistor. 7 2 SQW/OUT Operates with either VCC or VBAT applied. The pull up voltage may be up to 5.5V regardless of the voltage on VCC. If not used, this pin may be left unconnected. Primary Power Supply. When voltage is applied within normal limits, the device is fully accessible and data can be written and read. When a backup supply is 8 3 VCC connected to the device and VCC is below VPF, reads and writes are inhibited. The backup supply maintains the timekeeping function while VCC is absent. No Connection. These pins are not connected internally, but must be grounded — 4–13 N.C. for proper operation. DETAILED DESCRIPTION The DS1338 serial RTC is a low-power, full BCD clock/calendar plus 56 bytes of NV SRAM. Address and data are transferred serially through an I2C interface. The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The end of the month date is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with AM/PM indicator. The DS1338 has a built-in power-sense circuit that detects power failures and automatically switches to the VBAT supply. 7 of 16

DS1338 OPERATION The DS1338 operates as a slave device on the serial bus. Access is obtained by implementing a START condition and providing a device identification code, followed by data. Subsequent registers can be accessed sequentially until a STOP condition is executed. The device is fully accessible and data can be written and read when VCC is greater than VPF. However, when VCC falls below VPF, the internal clock registers are blocked from any access. If VPF is less than VBAT, the device power is switched from VCC to VBAT when VCC drops below VPF. If VPF is greater than VBAT, the device power is switched from VCC to VBAT when VCC drops below VBAT. The oscillator and timekeeping functions are maintained from the VBAT source until VCC is returned to nominal levels. The block diagram (Figure 3) shows the main elements of the DS1338. An enable bit in the seconds register controls the oscillator. Oscillator startup times are highly dependent upon crystal characteristics, PC board leakage, and layout. High ESR and excessive capacitive loads are the major contributors to long start-up times. A circuit using a crystal with the recommended characteristics and proper layout usually starts within 1 second. POWER CONTROL The power-control function is provided by a precise, temperature-compensated voltage reference and a comparator circuit that monitors the VCC level. The device is fully accessible and data can be written and read when VCC is greater than VPF. However, when VCC falls below VPF, the internal clock registers are blocked from any access. If VPF is less than VBAT, the device power is switched from VCC to VBAT when VCC drops below VPF. If VPF is greater than VBAT, the device power is switched from VCC to VBAT when VCC drops below VBAT. The registers are maintained from the VBAT source until VCC is returned to nominal levels (Table 1). After VCC returns above VPF, read and write access is allowed after tREC (Figure 1). On the first application of power to the device the time and date registers are reset to 01/01/00 01 00:00:00 (DD/MM/YY DOW HH:MM:SS). The CH bit in the seconds register will be set to a 0. Table 1. Power Control SUPPLY READ/WRITE POWERED CONDITION ACCESS BY VCC < VPF, VCC < VBAT No VBAT VCC < VPF, VCC > VBAT No VCC VCC > VPF, VCC < VBAT Yes VCC VCC > VPF, VCC > VBAT Yes VCC OSCILLATOR CIRCUIT The DS1338 uses an external 32.768kHz crystal. The oscillator circuit does not require any external resistors or capacitors to operate. Table 2 specifies several crystal parameters for the external crystal. Figure 3 shows a functional schematic of the oscillator circuit. The startup time is usually less than 1 second when using a crystal with the specified characteristics. Table 2. Crystal Specifications* PARAMETER SYMBOL MIN TYP MAX UNITS Nominal Frequency fO 32.768 kHz Series Resistance ESR 50 kΩ Load Capacitance CL 12.5 pF *The crystal, traces, and crystal input pins should be isolated from RF generating signals. Refer to Application Note 58: Crystal Considerations for Dallas Real-Time Clocks for additional specifications. 8 of 16

DS1338 CLOCK ACCURACY The accuracy of the clock is dependent upon the accuracy of the crystal and the accuracy of the match between the capacitive load of the oscillator circuit and the capacitive load for which the crystal was trimmed. Crystal frequency drift caused by temperature shifts creates additional error. External circuit noise coupled into the oscillator circuit can result in the clock running fast. Figure 4 shows a typical PC board layout for isolating the crystal and oscillator from noise. Refer to Application Note 58: Crystal Considerations with Dallas Real-Time Clocks for detailed information. DS1338C ONLY The DS1338C integrates a standard 32,768Hz crystal in the package. Typical accuracy at nominal VCC and +25°C is approximately 10ppm. Refer to Application Note 58 for information about crystal accuracy vs. temperature. Figure 4. Typical PC Board Layout for Crystal LOCAL GROUND PLANE (LAYER 2) X1 CRYSTAL X2 GND NOTE: AVOID ROUTING SIGNALS IN THE CROSSHATCHED AREA (UPPER LEFT-HAND QUADRANT) OF THE PACKAGE UNLESS THERE IS A GROUND PLANE BETWEEN THE SIGNAL LINE AND THE PACKAGE. RTC AND RAM ADDRESS MAP Table 3 shows the address map for the RTC and RAM registers. The RTC registers and control register are located in address locations 00h to 07h. The RAM registers are located in address locations 08h to 3Fh. During a multibyte access, when the register pointer reaches 3Fh (the end of RAM space) it wraps around to location 00h (the beginning of the clock space). On an I2C START, STOP, or register pointer incrementing to location 00h, the current time and date is transferred to a second set of registers. The time and date in the secondary registers are read in a multibyte data transfer, while the clock continues to run. This eliminates the need to re-read the registers in case of an update of the main registers during a read. CLOCK AND CALENDAR The time and calendar information is obtained by reading the appropriate register bytes. See Figure 6 for the RTC registers. The time and calendar are set or initialized by writing the appropriate register bytes. The contents of the time and calendar registers are in the BCD format. Bit 7 of Register 0 is the clock halt (CH) bit. When this bit is set to 1, the oscillator is disabled. When cleared to 0, the oscillator is enabled. The clock can be halted whenever the timekeeping functions are not required, which minimizes VBAT current (IBATDAT) when VCC is not applied. The day-of-week register increments at midnight. Values that correspond to the day of week are user-defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on). Illogical time and date entries result in undefined operation. When reading or writing the time and date registers, secondary (user) buffers are used to prevent errors when the internal registers update. When reading the time and date registers, the user buffers are synchronized to the internal registers on any start or stop and when the register pointer rolls over to zero. The countdown chain is reset whenever the seconds register is written. Write transfers occur on the acknowledge from the DS1338. Once the 9 of 16

DS1338 countdown chain is reset, to avoid rollover issues the remaining time and date registers must be written within 1 second. The 1Hz square-wave output, if enabled, transitions high 500ms after the seconds data transfer, provided the oscillator is already running. The DS1338 runs in either 12-hour or 24-hour mode. Bit 6 of the hours register is defined as the 12-hour or 24-hour mode-select bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the AM/PM bit, with logic high being PM. In the 24-hour mode, bit 5 is the 20-hour bit (20–23 hours). If the 12/24-hour mode select is changed, the hours register must be re-initialized to the new format. On an I2C START, the current time is transferred to a second set of registers. The time information is read from these secondary registers, while the clock continues to run. This eliminates the need to re-read the registers in case of an update of the main registers during a read. Table 3. RTC and RAM Address Map ADDRESS BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 FUNCTION RANGE 00H CH 10 Seconds Seconds Seconds 00–59 01H 0 10 Minutes Minutes Minutes 00–59 AM/PM 1–12 10 02H 0 12/24 Hour Hours +AM/PM 20 Hour Hour 00–23 03H 0 0 0 0 0 Day Day 1–7 04H 0 0 10 Date Date Date 01–31 10 05H 0 0 0 Month Month 01–12 Month 06H 10 Year Year Year 00–99 07H OUT 0 OSF SQWE 0 0 RS1 RS0 Control 08H–3FH RAM 56 x 8 00H–FFH Note: Bits listed as “0” always read as a 0. 10 of 16

DS1338 CONTROL REGISTER (07H) The control register controls the operation of the SQW/OUT pin and provides oscillator status. Bit # BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 Name OUT 0 OSF SQWE 0 0 RS1 RS0 POR 1 0 1 1 0 0 1 1 Bit 7: Output Control (OUT). Controls the output level of the SQW/OUT pin when the square-wave output is disabled. If SQWE = 0, the logic level on the SQW/OUT pin is 1 if OUT = 1; it is 0 if OUT = 0. Bit 5: Oscillator Stop Flag (OSF). A logic 1 in this bit indicates that the oscillator has stopped or was stopped for some time period and can be used to judge the validity of the clock and calendar data. This bit is edge triggered, and is set to logic 1 when the internal circuitry senses the oscillator has transitioned from a normal run state to a STOP condition. The following are examples of conditions that may cause the OSF bit to be set: 1) The first time power is applied. 2) The voltage present on VCC and VBAT are insufficient to support oscillation. 3) The CH bit is set to 1, disabling the oscillator. 4) External influences on the crystal (i.e., noise, leakage, etc.). This bit remains at logic 1 until written to logic 0. This bit can only be written to logic 0. Attempting to write OSF to logic 1 leaves the value unchanged. Bit 4: Square-Wave Enable (SQWE). When set to logic 1, this bit enables the oscillator output to operate with either VCC or VBAT applied. The frequency of the square-wave output depends upon the value of the RS0 and RS1 bits. Bits 1 and 0: Rate Select (RS1 and RS0). These bits control the frequency of the square-wave output when the square-wave output has been enabled. The table below lists the square-wave frequencies that can be selected with the RS bits. Square-Wave Output OUT RS1 RS0 SQW OUTPUT SQWE X 0 0 1Hz 1 X 0 1 4.096kHz 1 X 1 0 8.192kHz 1 X 1 1 32.768kHz 1 0 X X 0 0 1 X X 1 0 11 of 16

DS1338 I2C SERIAL DATA BUS The DS1338 supports the I2C protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data is a receiver. The device that controls the message is called a master. The devices that are controlled by the master are referred to as slaves. The bus must be controlled by a master device, which generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. The DS1338 operates as a slave on the I2C bus. Within the bus specifications, a standard mode (100kHz maximum clock rate) and a fast mode (400kHz maximum clock rate) are defined. The DS1338 works in both modes. Connections to the bus are made through the open-drain I/O lines SDA and SCL. The following bus protocol has been defined (Figure 5). Data transfer can be initiated only when the bus is not busy. During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH are interpreted as control signals. Accordingly, the following bus conditions have been defined: Bus not busy: Both data and clock lines remain HIGH. Start data transfer: A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition. Stop data transfer: A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition. Data valid: The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data. Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions is not limited and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit. Acknowledge: Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit. A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition. Figure 5. Data Transfer on I2C Serial Bus 12 of 16

DS1338 Depending upon the state of the R/W bit, two types of data transfer are possible: 1) Data transfer from a master transmitter to a slave receiver. The master transmits the first byte (the slave address). Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most significant bit (MSB) first. 2) Data transfer from a slave transmitter to a master receiver. The master transmits the first byte (the slave address). The slave then returns an acknowledge bit, which is followed by the slave transmitting a number of data bytes. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a “not acknowledge” is returned. The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus is not released. Data is transferred with the most significant bit (MSB) first. The DS1338 can operate in the following two modes: 1) Slave receiver mode (write mode): Serial data and clock are received through SDA and SCL. An acknowledge bit is transmitted after each byte is received. START and STOP conditions are recognized as the beginning and end of a serial transfer. Hardware performs address recognition after reception of the slave address and direction bit (Figure 6). The slave address byte is the first byte received after the master generates the START condition. The slave address byte contains the 7-bit DS1338 address—1101000— followed by the direction bit (R/W), which, for a write, is 0. After receiving and decoding the slave address byte, the slave outputs an acknowledge on the SDA line. After the DS1338 acknowledges the slave address and write bit, the master transmits a register address to the DS1338. This sets the register pointer on the DS1338, with DS1338 acknowledging the transfer. The master may then transmit zero or more bytes of data, with the DS1338 acknowledging each byte received. The register pointer increments after each data byte is transferred. The master generates a STOP condition to terminate the data write. 2) Slave transmitter mode (read mode): The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit indicates that the transfer direction is reversed. The DS1338 transmits serial data on SDA while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer (Figure 7). The slave address byte is the first byte received after the master generates the START condition. The slave address byte contains the 7-bit DS1338 address— 1101000—followed by the direction bit (R/W), which, for a read, is 1. After receiving and decoding the slave address byte, the slave outputs an acknowledge on the SDA line. The DS1338 then starts transmitting data using the register address pointed to by the register pointer. If the register pointer is not set before the initiation of a read mode, the first address that is read is the last one stored in the register pointer. The register pointer is incremented after each byte is transferred. The DS1338 must receive a “not acknowledge” to end a read. 13 of 16

DS1338 Figure 6. Data Write—Slave Receiver Mode > W <Slave Address> <R/ <Word Address (n)> <Data (n)> <Data (n+1)> <Data (n+X)> S 1101000 0 A XXXXXXXX A XXXXXXXX A XXXXXXXX A ... XXXXXXXX A P S - START MASTER TO SLAVE A - ACKNOWLEDGE (ACK) DATA TRANSFERRED P - STOP SLAVE TO MASTER (X+1 BYTES + ACKNOWLEDGE) Figure 7. Data Read (From Current Pointer Location)—Slave Transmitter Mode > W <Slave Address> <R/ <Data (n)> <Data (n+1)> <Data (n+2)> <Data (n+X)> S 1101000 1 A XXXXXXXX A XXXXXXXX A XXXXXXXX A ... XXXXXXXX A P S - START A - ACKNOWLEDGE (ACK) MASTER TO SLAVE DATA TRANSFERRED P - STOP (X+1 BYTES + ACKNOWLEDGE) A - NOT ACKNOWLEDGE (NACK) SLAVE TO MASTER NOTE: LAST DATA BYTE IS FOLLOWED BY A NACK Figure 8. Data Read (Write Pointer, Then Read—Slave Receive and Transmit > > W W R/ <Word Address (n)> <Slave Address> R/ < < S 1101000 0 A XXXXXXXX A Sr 1101000 1 A <Data (n)> <Data (n+1)> <Data (n+2)> <Data (n+X)> XXXXXXXX A XXXXXXXX A XXXXXXXX A ... XXXXXXXX A P S - START SR - REPEATED START A - ACKNOWLEDGE (ACK) MASTER TO SLAVE DATA TRANSFERRED P - STOP SLAVE TO MASTER (X+1 BYTES + ACKNOWLEDGE) A - NOT ACKNOWLEDGE (NACK) NOTE: LAST DATA BYTE IS FOLLOWED BY A NACK 14 of 16

DS1338 HANDLING, PCB LAYOUT, AND ASSEMBLY The DS1338C package contains a quartz tuning-fork crystal. Pick-and-place equipment may be used, but precautions should be taken to ensure that excessive shocks are avoided. Ultrasonic cleaning should be avoided to prevent damage to the crystal. Exposure to reflow is limited to 2 times maximum. Avoid running signal traces under the package, unless a ground plane is placed between the package and the signal line. All N.C. (no connect) pins must be connected to ground. The RoHS and lead-free/RoHS packages may be reflowed using a reflow profile that complies with JEDEC J-STD- 020. Moisture-sensitive packages are shipped from the factory dry-packed. Handling instructions listed on the package label must be followed to prevent damage during reflow. Refer to the IPC/JEDEC J-STD-020 standard for moisture- sensitive device (MSD) classifications. PIN CONFIGURATIONS TOP VIEW TOP VIEW SCL SDA X1 VCC SQW/OUT DS1338C GND 1 8 Vcc VBAT X2 SQW/OUT 2 38 7 N.C. N.C. VBAT 3 S13 6 SCL N.C. N.C. D GND 4 5 SDA N.C. N.C. N.C. N.C. SO, μSOP N.C. N.C. SO (300 mils) CHIP INFORMATION TRANSISTOR COUNT: 12,231 PROCESS: CMOS THERMAL INFORMATION THETA-J THETA-J PART A C (°C/W) (°C/W) 8 SO 132 38 8 μSOP 206.3 42 16 SO 73 23 PACKAGE INFORMATION For the latest package outline information and land patterns (footprints), go to www.maxim-ic.com/packages. Note that a “+”, “#”, or “-“ in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status. PACKAGE TYPE PACKAGE CODE OUTLINE NO. LAND PATTERN NO. 8 SO S8+4 21-0041 90-0096 8 µMAX U8+1 21-0036 90-0092 16 SO W16#H2 21-0042 90-0107 15 of 16

REVISION HISTORY REVISION PAGES DESCRIPTION DATE CHANGED Modified the Features bullet to indicate that battery-backed RAM has unlimited 1 writes. Removed leaded part numbers from the Ordering Information table. 1 Removed the pullup resistor voltage spec from the Recommended DC 2, 7 Operating Conditions table and added it to the pin descriptions. 100108 Updated the block diagram (Figure 3) to show that SQW is open drain. 5 Added the initial POR state for time and date registers in the Power Control 8 section. Added text to explain the use of the oscillator bit to control battery current in the 9 Clock and Calendar section. Updated the Absolute Maximum Ratings, Recommended DC Operating Conditions, DC Electrical Characteristics, Power Control, Oscillator Circuit, 9/11 2, 8, 10, 15 Table 3, Handling, PBB Layout, and Assembly, Thermal Information, and Package Information. 3/12 Corrected the CH bit POR condition from 1 to 0 in the Power Control section 8 4/15 Revised Benefits and Features section 1 16 of 16 Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. Maxim Integrated Products, 160 Rio Robles, San Jose, CA 95134 408-601-1000 © 2015 Maxim Integrated Products Maxim is a registered trademark of Maxim Integrated Products, Inc.

Mouser Electronics Authorized Distributor Click to View Pricing, Inventory, Delivery & Lifecycle Information: M axim Integrated: DS1338C-18# DS1338C-3# DS1338C-33# DS1338C-33#T&R DS1338U-18+ DS1338U-3+ DS1338U-3+T&R DS1338Z-18+ DS1338Z-3+T&R DS1338Z-33+T&R DS1338Z-18+T&R DS1338U-33+ DS1338U-33+T&R DS1338Z- 3+ DS1338Z-33+

Datasheet下载

Datasheet下载