ICGOO在线商城 > 集成电路(IC) > 数据采集 - 模拟前端(AFE) > ADS131E04IPAGR

- 型号: ADS131E04IPAGR

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ADS131E04IPAGR产品简介:

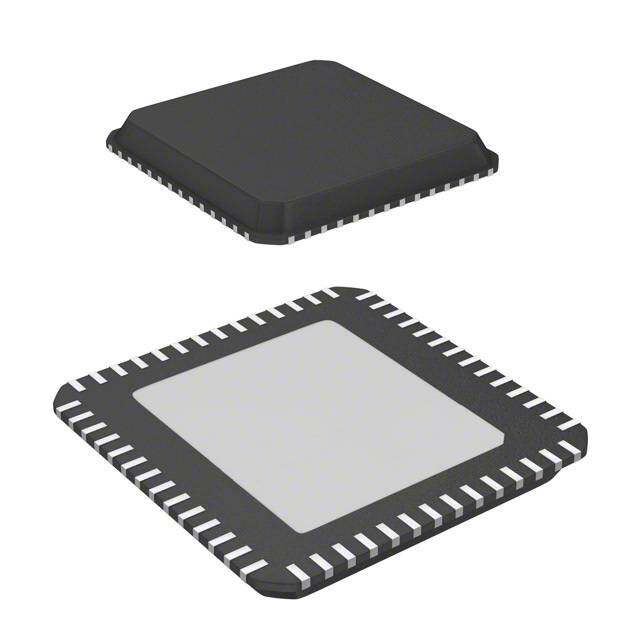

ICGOO电子元器件商城为您提供ADS131E04IPAGR由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 ADS131E04IPAGR价格参考。Texas InstrumentsADS131E04IPAGR封装/规格:数据采集 - 模拟前端(AFE), 4 Channel AFE 16, 24 Bit 10.2mW 64-TQFP (10x10)。您可以下载ADS131E04IPAGR参考资料、Datasheet数据手册功能说明书,资料中有ADS131E04IPAGR 详细功能的应用电路图电压和使用方法及教程。

Texas Instruments(德州仪器)的ADS131E04IPAGR是一款高性能、低功耗的24位模数转换器(ADC),属于数据采集系统中的模拟前端(AFE)产品。其应用场景主要包括以下几个方面: 1. 医疗设备 - 心电图(ECG/EKG)监测:ADS131E04IPAGR具有高分辨率和低噪声特性,非常适合用于心电图设备中,能够精确采集心脏电信号。 - 生物电势测量:可用于脑电图(EEG)、肌电图(EMG)等生物信号采集,支持多通道同步采样,满足高精度需求。 2. 工业自动化 - 传感器信号调理:适用于压力、温度、振动等传感器信号的高精度采集,广泛用于工业控制和监测系统。 - 过程控制:在工厂自动化中,该器件可用于实时监测和控制关键参数,确保系统的稳定性和可靠性。 3. 能源管理 - 智能电网监控:用于电力线路电流和电压信号的高精度采集,支持电网状态的实时分析。 - 电池管理系统(BMS):能够精确测量电池组的电压、电流和温度,提升电池的安全性和寿命。 4. 环境监测 - 气象站:用于采集风速、湿度、气压等环境参数,提供高精度的数据支持。 - 水质检测:对水体中的电导率、pH值等参数进行精确测量。 5. 科研与测试设备 - 实验室仪器:如示波器、信号分析仪等,需要高精度数据采集的场景。 - 振动与噪声分析:用于机械设备的故障诊断和性能优化。 核心优势 - 24位分辨率:提供极高的测量精度。 - 低功耗设计:适合便携式和电池供电设备。 - 多通道同步采样:支持复杂系统的多点数据采集。 - 内置PGA(可编程增益放大器):简化信号调理电路设计。 综上,ADS131E04IPAGR凭借其高精度、低功耗和灵活性,广泛应用于医疗、工业、能源、环境监测及科研等领域,是高性能数据采集系统的核心组件之一。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC AFE 16/24BIT 64KSPS 64TQFP |

| 产品分类 | 数据采集 - 模拟前端 (AFE) |

| 品牌 | Texas Instruments |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | ADS131E04IPAGR |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | - |

| 位数 | 16,24 |

| 供应商器件封装 | 64-TQFP(10x10) |

| 其它名称 | ADS131E04IPAGR-ND |

| 功率(W) | 10.2mW |

| 包装 | 带卷 (TR) |

| 封装/外壳 | 64-TQFP |

| 标准包装 | 1,500 |

| 电压-电源,数字 | 1.8 V ~ 3.6 V |

| 电压-电源,模拟 | 2.7 V ~ 5.25 V |

| 通道数 | 4 |

PDF Datasheet 数据手册内容提取

Product Order Technical Tools & Support & Folder Now Documents Software Community ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 ADS131E0x 4-, 6-, and 8-Channel, 24-Bit, Simultaneously-Sampling, Delta-Sigma ADC 1 Features The ADS131E0x have a flexible input multiplexer per channel that can be independently connected to the • EightDifferentialADCInputs 1 internally-generated signals for test, temperature, and • OutstandingPerformance: fault detection. Fault detection can be implemented – DynamicRange:118dBat1kSPS internal to the device, using the integrated comparators with digital-to-analog converter (DAC)- – Crosstalk: –110dB controlledtriggerlevels.TheADS131E0xcanoperate – THD:–90dBat50Hzand60Hz atdataratesashighas64kSPS. • AnalogSupplyRangeOptions: These complete analog front-end (AFE) solutions are – 3Vto5V(Unipolar) packaged in a TQFP-64 package and are specified – ±2.5V(Bipolar,AllowsDC-Coupling) over the industrial temperature range of –40°C to +105°C. • Digital:1.8Vto3.6V • LowPower:2mWperChannel DeviceInformation(1) • DataRates:1,2,4,8,16,32,and64kSPS PARTNUMBER PACKAGE BODYSIZE(NOM) • ProgrammableGains:1,2,4,8,and12 ADS131E0x TQFP(64) 10.00mm×10.00mm • FaultDetectionandDeviceTestingCapability (1) For all available packages, see the orderable addendum at • SPI™DataInterfaceandFourGPIOs theendofthedatasheet. • Package:TQFP-64(PAG) ADS131E08SimplifiedSchematic • OperatingTemperatureRange: –40°Cto+105°C Current Line A Sensing Channel 1 PGA AßD(cid:8)C Device 2 Applications SVeonltsaigneg Channel 2 PGA AßD(cid:8)C Voltage • PowerProtection:CircuitBreakers,andRelay Reference Protection SCeunrrseinngt Channel 3 PGA AßD(cid:8)C Oscillator • EnergyMetering:SinglePhase,Polyphase,and Line B PowerQuality SVeonltsaigneg EMI Channel 4 PGA AßD(cid:8)C Filters Control • BatteryTestSystems and and Input SPI Interface • TestandMeasurement SCeunrrseinngt MUX Channel 5 PGA AßD(cid:8)C Line C • SimultaneousSamplingDataAcquisitionSystems SVeonltsaigneg Channel 6 PGA AßD(cid:8)C DeFteacutliton 3 Description Current Channel 7 PGA AßD(cid:8)C Test The ADS131E0x are a family of multichannel, Sensing Line N simultaneous sampling, 24-bit, delta-sigma (ΔΣ), Voltage Channel 8 PGA AßD(cid:8)C AOmpp analog-to-digital converters (ADCs) with a built-in Sensing programmable gain amplifier (PGA), internal reference, and an onboard oscillator. The ADC wide dynamic range, scalable data rates, and internal fault detect monitors make the ADS131E0x attractive in industrial power monitoring and protection as well as test and measurement applications. True high- impedance inputs enable the ADS131E0x to directly interface with a resistor-divider network or a voltage transformer to measure line voltage, or a current transformer or Rogowski coil to measure line current. With high integration levels and exceptional performance, the ADS131E0x family enables the creation of scalable industrial power systems at significantly reduced size, power, and low overall cost. 1 An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectualpropertymattersandotherimportantdisclaimers.PRODUCTIONDATA.

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com Table of Contents 1 Features.................................................................. 1 9.5 Programming...........................................................33 2 Applications........................................................... 1 9.6 RegisterMap...........................................................39 3 Description............................................................. 1 10 ApplicationandImplementation........................ 49 4 RevisionHistory..................................................... 2 10.1 ApplicationInformation..........................................49 10.2 TypicalApplication................................................58 5 DeviceComparison............................................... 4 11 PowerSupplyRecommendations..................... 61 6 PinConfigurationandFunctions......................... 4 11.1 Power-UpTiming..................................................61 7 Specifications......................................................... 7 11.2 RecommendedExternalCapacitorValues...........62 7.1 AbsoluteMaximumRatings......................................7 11.3 DeviceConnectionsforUnipolarPowerSupplies 62 7.2 ESDRatings..............................................................7 11.4 DeviceConnectionsforBipolarPowerSupplies..63 7.3 RecommendedOperatingConditions.......................7 12 Layout................................................................... 64 7.4 ThermalInformation..................................................8 12.1 LayoutGuidelines.................................................64 7.5 ElectricalCharacteristics...........................................9 12.2 LayoutExample....................................................64 7.6 TimingRequirements..............................................12 13 DeviceandDocumentationSupport................. 66 7.7 SwitchingCharacteristics........................................12 7.8 TypicalCharacteristics............................................13 13.1 DeviceSupport......................................................66 13.2 RelatedLinks........................................................66 8 ParameterMeasurementInformation................16 13.3 ReceivingNotificationofDocumentationUpdates66 8.1 NoiseMeasurements..............................................16 13.4 CommunityResource............................................66 9 DetailedDescription............................................ 17 13.5 Trademarks...........................................................66 9.1 Overview.................................................................17 13.6 ElectrostaticDischargeCaution............................66 9.2 FunctionalBlockDiagram.......................................18 13.7 Glossary................................................................66 9.3 FeatureDescription................................................19 14 Mechanical,Packaging,andOrderable 9.4 DeviceFunctionalModes........................................28 Information........................................................... 67 4 Revision History NOTE:Pagenumbersforpreviousrevisionsmaydifferfrompagenumbersinthecurrentversion. ChangesfromRevisionB(December2013)toRevisionC Page • AddedESDRatingstable,FeatureDescriptionsection,DeviceFunctionalModes,ApplicationandImplementation section,PowerSupplyRecommendationssection,Layoutsection,DeviceandDocumentationSupportsection,and Mechanical,Packaging,andOrderableInformationsection ................................................................................................. 1 • ChangedformattingofThermalInformationtablenote ......................................................................................................... 8 ChangesfromRevisionA(April2013)toRevisionB Page • Deleteddevicegraphic........................................................................................................................................................... 1 • ChangedADS131E0xfamilydescriptionto24-bitsonlythroughoutdocument..................................................................... 1 • AddedAVSStoDGNDrowtoAbsoluteMaximumRatingstable.......................................................................................... 7 • ChangedminimumspecificationtoExternalReference,VREFPparameterinElectricalCharacteristicstable....................7 • ChangedconditionsinFigure10.......................................................................................................................................... 13 • ChangedconditionsinFigure11.......................................................................................................................................... 13 • ChangedSTARTOpcodetoSTARTinFigure39................................................................................................................ 28 • ChangedReset(RESET)sectionforclarity......................................................................................................................... 29 • ChangedPower-UpSequencingsection.............................................................................................................................. 61 ChangesfromOriginal(June2012)toRevisionA Page • DeletedAGNDtoDGNDrowfromAbsoluteMaximumRatingstable................................................................................... 7 • ChangedvalueofDigitalinputtoDVDDrowinAbsoluteMaximumRatingstable................................................................ 7 • AddedminimumandmaximumspecificationstoExternalReference,ReferenceinputvoltageparameterinElectrical 2 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 Characteristicstable............................................................................................................................................................... 7 • AddedminimumandmaximumspecificationstoExternalReference,VREFPparameterinElectricalCharacteristics table........................................................................................................................................................................................ 7 • ChangedChannelPerformance(ACPerformance),AccuracyparameterinElectricalCharacteristicstable.......................9 • ChangedInternalReference,V parameterinElectricalCharacteristicstable..................................................................... 9 O • ChangedInternalReference,TemperaturedriftparameterinElectricalCharacteristicstable.............................................. 9 • AddedFigure15 .................................................................................................................................................................. 14 Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com 5 Device Comparison PRODUCT NO.OFINPUTS REFERENCEOPTIONS RESOLUTION(Bits) POWER-UPTIME(ms) ADS130E08 8 Internal,external 16 128 ADS131E04 4 Internal,external 24 128 ADS131E06 6 Internal,external 24 128 ADS131E08 8 Internal,external 24 128 ADS131E08S 8 Internalonly 24 3 6 Pin Configuration and Functions PAGPackage 64-PinTQFP TopView T U AMPO AMPN AMPP DD SS SS DD AP3 DD1 SS1 KSEL ND DD ND C P C P P V V V V C V V L G V G N O N O O A A A A V A A C D D D 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 9 6 6 6 6 6 5 5 5 5 5 5 5 5 5 5 4 IN8N 1 48 DVDD IN8P 2 47 DRDY IN7N 3 46 GPIO4 IN7P 4 45 GPIO3 IN6N 5 44 GPIO2 IN6P 6 43 DOUT IN5N 7 42 GPIO1 IN5P 8 41 DAISY_IN IN4N 9 40 SCLK IN4P 10 39 CS IN3N 11 38 START IN3P 12 37 CLK IN2N 13 36 RESET IN2P 14 35 PWDN IN1N 15 34 DIN IN1P 16 33 DGND 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 1 1 1 2 2 2 2 2 2 2 2 2 2 3 3 3 P N D S D D S P N 4 C 1 C 2 1 S Not to scale T T D S D D S F F P N P N P V S S S V V V V V E E A A A S V E E A A A A A R R C C C E A T T V V V V V R 4 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 PinFunctions PIN I/O DESCRIPTION NAME NO. Analogsupply.Connecta1-µF(orlarger)capacitortoAVSSforeach AVDD 19,21,22,56,59 Supply AVDDpin. Chargepumpanalogsupply.Connecta1-µF(orlarger)capacitorto AVDD1 54 Supply AVSS1. AVSS 20,23,32,57,58 Supply Analogground AVSS1 53 Supply Chargepumpanalogground CS 39 Digitalinput Chipselect;activelow CLK 37 Digitalinput Masterclockinput.ConnecttoDGNDifunused. CLKSEL 52 Digitalinput Masterclockselect DAISY_IN 41 Digitalinput Daisy-chaininput.ConnecttoDGNDifunused. DGND 33,49,51 Supply Digitalground DIN 34 Digitalinput Serialdatainput DOUT 43 Digitaloutput Serialdataoutput Dataready;activelow.ConnecttoDGNDwitha10-kΩresistorif DRDY 47 Digitaloutput unused. Digitalcorepowersupply.Connecta1-µF(orlarger)capacitorto DVDD 48,50 Supply DGNDforeachDVDDpin. General-purposeinput/outputpin1.ConnecttoDGNDwitha10-kΩ GPIO1 42 Digitalinput/output resistorifunused. General-purposeinput/outputpin2.ConnecttoDGNDwitha10-kΩ GPIO2 44 Digitalinput/output resistorifunused. General-purposeinput/outputpin3.ConnecttoDGNDwitha10-kΩ GPIO3 45 Digitalinput/output resistorifunused. General-purposeinput/outputpin4.ConnecttoDGNDwitha10-kΩ GPIO4 46 Digitalinput/output resistorifunused. IN1N(1) 15 Analoginput Negativeanaloginput1 IN1P(1) 16 Analoginput Positiveanaloginput1 IN2N(1) 13 Analoginput Negativeanaloginput2 IN2P(1) 14 Analoginput Positiveanaloginput2 IN3N(1) 11 Analoginput Negativeanaloginput3 IN3P(1) 12 Analoginput Positiveanaloginput3 IN4N(1) 9 Analoginput Negativeanaloginput4 IN4P(1) 10 Analoginput Positiveanaloginput4 IN5N(1) 7 Analoginput Negativeanaloginput5(ADS131E06andADS131E08only) IN5P(1) 8 Analoginput Positiveanaloginput5(ADS131E06andADS131E08only) IN6N(1) 5 Analoginput Negativeanaloginput6(ADS131E06andADS131E08only) IN6P(1) 6 Analoginput Positiveanaloginput6(ADS131E06andADS131E08only) IN7N(1) 3 Analoginput Negativeanaloginput7(ADS131E08only) IN7P(1) 4 Analoginput Positiveanaloginput7(ADS131E08only) IN8N(1) 1 Analoginput Negativeanaloginput8(ADS131E08only) IN8P(1) 2 Analoginput Positiveanaloginput8(ADS131E08only) Noconnection,leavefloating.CanbeconnectedtoAVDDorAVSS NC 27,29,62,64 — witha10-kΩorhigherresistor. Opampinvertinginput;leavefloatingifunusedandpower-downthe OPAMPN 61 Analoginput opamp. Opampnoninvertinginput;leavefloatingifunusedandpower-down OPAMPP 60 Analoginput theopamp. OPAMPOUT 63 Analogoutput Opampoutput;leavefloatingifunusedandpower-downtheopamp. PWDN 35 Digitalinput Power-down;activelow (1) Connectanyunusedorpowered-downanaloginputpinstoAVDD. Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com PinFunctions(continued) PIN I/O DESCRIPTION NAME NO. RESET 36 Digitalinput Systemreset;activelow RESV1 31 Digitalinput Reservedforfutureuse.ConnectdirectlytoDGND. SCLK 40 Digitalinput Serialclockinput START 38 Digitalinput Startconversion Testsignal,negativepin.SeetheUnusedInputsandOutputssection TESTN 18 Analoginput/output forunusedpins. Testsignal,positivepin.SeetheUnusedInputsandOutputssection TESTP 17 Analoginput/output forunusedpins. VCAP1 28 Analogoutput Analogbypasscapacitor.Connecta22-µFcapacitortoAVSS. VCAP2 30 Analogoutput Analogbypasscapacitor.Connecta1-µFcapacitortoAVSS. Analogbypasscapacitor.Connectaparallelcombinationof1-µFand VCAP3 55 Analogoutput 0.1-µFcapacitorstoAVSS. VCAP4 26 Analogoutput Analogbypasscapacitor.Connecta1-µFcapacitortoAVSS. VREFN 25 Analoginput Negativereferencevoltage.ConnecttoAVSS Positivereferencevoltage.Connectaminimum10-µFcapacitorto VREFP 24 Analoginput/output VREFN. 6 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 7 Specifications 7.1 Absolute Maximum Ratings overoperatingfree-airtemperaturerange(unlessotherwisenoted)(1) MIN MAX UNIT AVDDtoAVSS –0.3 5.5 Power-supplyvoltage AVSStoDGND –3 0.2 V DVDDtoDGND –0.3 3.9 Analoginputvoltage AnaloginputtoAVSS AVSS–0.3 AVDD+0.3 V Digitalinputvoltage DigitalinputtoDVDD DGND–0.3 DVDD+0.3 V Momentary –100 100 Inputcurrent mA Continuous,allotherpinsexceptpower-supplypins –10 10 Junction,T 150 J Temperature °C Storage,T –60 150 stg (1) StressesbeyondthoselistedunderAbsoluteMaximumRatingsmaycausepermanentdamagetothedevice.Thesearestressratings only,whichdonotimplyfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderRecommended OperatingConditions.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability. 7.2 ESD Ratings VALUE UNIT Human-bodymodel(HBM),perANSI/ESDA/JEDECJS-001(1) ±1000 V(ESD) Electrostaticdischarge Charged-devicemodel(CDM),perJEDECspecificationJESD22- V C101(2) ±500 (1) JEDECdocumentJEP155statesthat500-VHBMallowssafemanufacturingwithastandardESDcontrolprocess. (2) JEDECdocumentJEP157statesthat250-VCDMallowssafemanufacturingwithastandardESDcontrolprocess. 7.3 Recommended Operating Conditions overoperatingfree-airtemperaturerange(unlessotherwisenoted) MIN NOM MAX UNIT POWERSUPPLY AVDD Analogpowersupply AVDDtoAVSS 2.7 5.0 5.25 V DVDD Digitalpowersupply DVDDtoDGND 1.7 1.8 3.6 V Analogtodigitalsupply AVDDtoDVDD –2.1 3.6 V ANALOGINPUTS VIN Differentialinputvoltage VIN=V(INxP)–V(INxN) –VREF/Gain VREF/Gain V VCM Common-modeinputvoltage VCM=(V(INxP)–V(INxN))/2 SeetheInputCommon-ModeRangesection V VOLTAGEREFERENCEINPUTS AVDD=3V,VREF=(VVREFP– 2 2.5 AVDD V VVREFN) VREF Referenceinputvoltage AVDD=5V,VREF=(VVREFP– 2 4 AVDD V VVREFN) VREFN Negativereferenceinput AVSS V VREFP Positiveinput AVDD–3 AVSS+2.5 AVDD V EXTERNALCLOCKSOURCE CLKSELpin=0, 1.7 2.048 2.25 (AVDD–AVSS)=3V fCLK Masterclockrate MHz CLKSELpin=0, 1.0 2.048 2.25 (AVDD–AVSS)=5V DIGITALINPUTS Inputvoltage DGND–0.1 DVDD+0.1 V TEMPERATURERANGE TA Operatingambienttemperature –40 105 °C Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com 7.4 Thermal Information ADS131E0x THERMALMETRIC(1) PAG(TQFP) UNIT 64PINS R Junction-to-ambientthermalresistance 35 °C/W θJA R Junction-to-case(top)thermalresistance 31 °C/W θJC(top) R Junction-to-boardthermalresistance 26 °C/W θJB ψ Junction-to-topcharacterizationparameter 0.1 °C/W JT ψ Junction-to-boardcharacterizationparameter NA °C/W JB R Junction-to-case(bottom)thermalresistance NA °C/W θJC(bot) (1) Formoreinformationabouttraditionalandnewthermalmetrics,seetheSemiconductorandICPackageThermalMetricsapplication report. 8 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 7.5 Electrical Characteristics Minimumandmaximumspecificationsapplyfrom–40°Cto+105°C.Typicalspecificationsareat25°C.Allspecificationsare atDVDD=1.8V,AVDD=3V,AVSS=0V,V =2.4V,externalf =2.048MHz,datarate=8kSPS,andgain=1, REF CLK unlessotherwisenoted. PARAMETER TESTCONDITIONS MIN TYP MAX UNIT ANALOGINPUTS Ci Inputcapacitance 20 pF IIB Inputbiascurrent PGAoutputinnormalrange 5 nA DCinputimpedance 200 MΩ PGAPERFORMANCE Gainsettings 1,2,4,8,12 BW Bandwidth SeeTable3 ADCPERFORMANCE DR Datarate fCLK=2.048MHz 1 64 kSPS DR=1kSPS,2kSPS,4kSPS,8kSPS,and16kSPS 24 Bits Resolution DR=32kSPSand64kSPS 16 Bits CHANNELPERFORMANCE(DCPERFORMANCE) INL Integralnonlinearity Full-scale,bestfit 10 ppm G=1 105 dB Dynamicrange SeetheNoiseMeasurements Gainsettingsotherthan1 section EO Offseterror 350 μV Offseterrordrift 0.65 μV/°C EG Gainerror Excludingvoltagereferenceerror 0.1% Gaindrift Excludingvoltagereferencedrift 3 ppm/°C Gainmatchbetweenchannels 0.2 %ofFS CHANNELPERFORMANCE(ACPERFORMANCE) CMRR Common-moderejectionratio fCM=50Hzand60Hz(1) –110 dB PSRR Power-supplyrejectionratio fPS=50Hzand60Hz –80 dB Crosstalk fIN=50Hzand60Hz –110 dB 3000:1dynamicrangewitha1- AVDD=3V,VREF=2.4V 0.04% Accuracy secondmeasurement (VRMS/IRMS) AVDD=5V,VREF=4V 0.025% SNR Signal-to-noiseratio fIN=50Hzand60Hz,gain=1 107 dB THD Totalharmonicdistortion 10Hz,–0.5dBFs –93 dB INTERNALREFERENCE TA=25°C,VREF=2.4V 2.394 2.4 2.406 V VREF Outputvoltage TA=25°C,VREF=4V 4 V VREFaccuracy ±0.2% Temperaturedrift TA=–40°Cto+105°C 20 ppm/°C Start-uptime Settledto0.2% 150 ms EXTERNALREFERENCE Inputimpedance 6 kΩ INTERNALOSCILLATOR ±2% Accuracy TA=25°C ±0.5% TA=–40°Cto105°C 2.5% Internaloscillatorclockfrequency Nominalfrequency 2.048 MHz Internaloscillatorstart-uptime 20 μs Internaloscillatorpower 120 μW consumption FAULTDETECTANDALARM Comparatorthresholdaccuracy ±30 mV (1) CMRRismeasuredwithacommon-modesignalof(AVSS+0.3V)to(AVDD–0.3V).Thevaluesindicatedaretheminimumofthe eightchannels. Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com Electrical Characteristics (continued) Minimumandmaximumspecificationsapplyfrom–40°Cto+105°C.Typicalspecificationsareat25°C.Allspecificationsare atDVDD=1.8V,AVDD=3V,AVSS=0V,V =2.4V,externalf =2.048MHz,datarate=8kSPS,andgain=1, REF CLK unlessotherwisenoted. PARAMETER TESTCONDITIONS MIN TYP MAX UNIT OPERATIONALAMPLIFIER Integratednoise 0.1Hzto250Hz 9 µVRMS Noisedensity 2kHz 120 nV/√Hz GBP Gainbandwidthproduct 50kΩ||10-pFload 100 kHz SR Slewrate 50kΩ||10-pFload 0.25 V/µs Loadcurrent 50 µA THD Totalharmonicdistortion fIN=100Hz 70 dB AVSS+ AVDD– Common-modeinputrange V 0.7 0.3 Quiescentpowerconsumption 20 µA SYSTEMMONITORS Supplyreading Analog 2% error Digital 2% Frompower-uptoDRDYlow 150 ms Devicewakeup STANDBYmode 31.25 µs Temperature Voltage TA=25°C 145 mV sensorreading Coefficient 490 μV/°C SELF-TESTSIGNAL fCLK/221 Signalfrequency SeetheRegisterMapsectionforsettings Hz fCLK/220 ±1 Signalvoltage SeetheRegisterMapsectionforsettings mV ±2 DIGITALINPUTANDOUTPUT(DVDD=1.8Vto3.6V) VIH Logiclevel, High 0.8DVDD DVDD+0.1 V VIL inputvoltage Low –0.1 0.2DVDD V VOH Logiclevel, High IOH=–500µA 0.9DVDD V VOL outputvoltage Low IOL=+500µA 0.1DVDD V IIN Inputcurrent 0V<VDigitalInput<DVDD –10 10 μA 10 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 Electrical Characteristics (continued) Minimumandmaximumspecificationsapplyfrom–40°Cto+105°C.Typicalspecificationsareat25°C.Allspecificationsare atDVDD=1.8V,AVDD=3V,AVSS=0V,V =2.4V,externalf =2.048MHz,datarate=8kSPS,andgain=1, REF CLK unlessotherwisenoted. PARAMETER TESTCONDITIONS MIN TYP MAX UNIT SUPPLYCURRENT(OPERATIONALAMPLIFIERTURNEDOFF) AVDD–AVSS=3V 5.1 mA IAVDD AVDD–AVSS=5V 5.8 mA Normalmode DVDD=3.3V 1 mA IDVDD DVDD=1.8V 0.4 mA POWERDISSIPATION(ANALOGSUPPLY=3V) Normalmode 9.3 10.2 mW ADS131E04 Power-downmode 10 µW Standbymode 2 mW Normalmode 12.7 13.5 mW Quiescentpower ADS131E06 Power-downmode 10 µW dissipation Standbymode 2 mW Normalmode 16 17.6 mW ADS131E08 Power-downmode 10 µW Standbymode 2 mW POWERDISSIPATION(ANALOGSUPPLY=5V) Normalmode 18 mW ADS131E04 Power-downmode 20 µW Standbymode 4.2 mW Normalmode 24.3 mW Quiescentpower ADS131E06 Power-downmode 20 µW dissipation Standbymode 4.2 mW Normalmode 29.7 mW ADS131E08 Power-downmode 20 µW Standbymode 4.2 mW Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 11 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com 7.6 Timing Requirements overoperatingambienttemperaturerangeandDVDD=1.7Vto3.6V(unlessotherwisenoted) 2.7V≤DVDD≤3.6V 1.7V≤DVDD≤2.0V UNIT MIN MAX MIN MAX t Masterclockperiod 444 588 444 588 ns CLK t Delaytime,firstSCLKrisingedgeafterCSfallingedge 6 17 ns CSSC t SCLKperiod 50 66.6 ns SCLK t Pulseduration,SCLKhighorlow 15 25 ns SPWH,L t Setuptime,DINvalidbeforeSCLKfallingedge 10 10 ns DIST t Holdtime,DINvalidafterSCLKfallingedge 10 11 ns DIHD t Pulseduration,CShigh 2 2 t CSH CLK t Delaytime,CSrisingedgeafterfinalSCLKfallingedge 4 4 t SCCS CLK t Commanddecodetime 4 4 t SDECODE CLK t Setuptime,DAISY_INvalidbeforeSCLKfallingedge 10 10 ns DISCK2ST t Holdtime,DAISY_INvalidafterSCLKfallingedge 10 10 ns DISCK2HT 7.7 Switching Characteristics overoperatingambienttemperaturerange,DVDD=1.7Vto3.6V,andloadonDOUT=20pF||100kΩ(unlessotherwise noted) 2.7V≤DVDD≤3.6V 1.7V≤DVDD≤2.0V PARAMETER UNIT MIN MAX MIN MAX t Propagationdelaytime,CSfallingedgetoDOUTdriven 10 20 ns CSDOD t Propagationdelaytime,SCLKrisingedgetovalidnewDOUT 17 32 ns DOST t Holdtime,SCLKfallingedgetoinvalidDOUT 10 10 ns DOHD Propagationdelaytime,CSrisingedgetoDOUThigh t 10 20 ns CSDOZ impedance (cid:15) (cid:2)(cid:4)(cid:5) (cid:2)(cid:4)(cid:5) (cid:2)(cid:3) (cid:15)(cid:2)(cid:3)(cid:3)(cid:2) (cid:15)(cid:3)(cid:6)(cid:19)(cid:2)(cid:9)(cid:6)(cid:19) (cid:15)(cid:2)(cid:3)(cid:16) (cid:15)(cid:3)(cid:2)(cid:4)(cid:5) (cid:15)(cid:3)(cid:17)(cid:18)(cid:16) (cid:15)(cid:3)(cid:17)(cid:18)(cid:4) (cid:15)(cid:3)(cid:2)(cid:2)(cid:3) (cid:3)(cid:2)(cid:4)(cid:5) (cid:1) (cid:12) (cid:13) (cid:14) (cid:1) (cid:12) (cid:13) (cid:14) (cid:15) (cid:15) (cid:15) (cid:6)(cid:7)(cid:16)(cid:6) (cid:6)(cid:9)(cid:16)(cid:6) (cid:6)(cid:7)(cid:3)(cid:11) (cid:15) (cid:6)(cid:7)(cid:8) (cid:6)(cid:9)(cid:3)(cid:11) (cid:15)(cid:2)(cid:3)(cid:6)(cid:9)(cid:6) (cid:15)(cid:2)(cid:3)(cid:6)(cid:9)(cid:22) (cid:6)(cid:9)(cid:10)(cid:11) (cid:16)(cid:20)(cid:21)(cid:22) (cid:16)(cid:20)(cid:21)(cid:22) NOTE: SPIsettingsareCPOL=0andCPHA=1. Figure1. SerialInterfaceTiming (cid:16) (cid:1)(cid:3)(cid:4)(cid:11)(cid:13)(cid:17)(cid:4)(cid:10) (cid:16) (cid:1)(cid:3)(cid:4)(cid:11)(cid:13)(cid:17)(cid:22)(cid:10) (cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:3)(cid:7) (cid:14)(cid:4)(cid:15) (cid:12)(cid:4)(cid:15) (cid:4)(cid:11)(cid:12)(cid:13) (cid:18) (cid:17) (cid:19) (cid:20) (cid:20)(cid:21)(cid:18) (cid:20)(cid:21)(cid:17) (cid:20)(cid:21)(cid:19) (cid:16) (cid:1)(cid:8)(cid:4)(cid:10) (cid:1)(cid:8)(cid:9)(cid:10) (cid:14)(cid:4)(cid:15) (cid:12)(cid:4)(cid:15) (cid:23) (cid:14)(cid:4)(cid:15) (1) n=Numberofchannels×resolution+24bits.Numberofchannelsis8;resolutionis24-bit. Figure2. Daisy-ChainInterfaceTiming 12 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 7.8 Typical Characteristics allplotsareatT =25°C,AVDD=3V,AVSS=0V,DVDD=1.8V,internalVREFP=2.4V,VREFN=AVSS,externalclock A =2.048MHz,datarate=8kSPS,andgain=1,unlessotherwisenoted. 10 2200 8 Data Rate = 1 kSPS 2000 Data Rate = 1 kSPS Gain = 1 Gain = 1 V) 6 1800 e (µ 4 1600 Referred Nois −202 Occurences 111802400000000 − −4 ut 600 p In −6 400 −8 200 −10 0 0 1 2 3 4 5 6 7 8 9 10 99887766554433221100112233445566778899 Time (s) −−−−−−−−−−−−−−−−−− G003 Input−Referred Noise (µV) G004 Figure3.Input-ReferredNoise Figure4.NoiseHistogram −90 −75 Gain = 1 Gain = 1 −95 Gain = 2 B) Gain = 2 Gain = 4 d Gain = 4 −100 Gain = 8 n ( −80 Gain = 8 o MRR (dB)−−111005 Gain = 12 onic Distorti −85 Gain = 12 C−115 m ar H −120 al −90 ot −125 Data Rate = 4 kSPS T AIN = AVDD − 0.3 V to AVSS + 0.3 V −130 −95 10 100 1000 10 100 1000 Frequency (Hz) Frequency (Hz) G005 G006 Figure5.CMRRvsFrequency Figure6.THDvsFrequency 110 14 B) G = 1 G = 4 G = 12 12 Gain = 1 Ratio (d 105 G = 2 G = 8 ppm) 1680 GGGaaaiiinnn === 248 n 100 y ( 4 Gain = 12 Supply Rejectio 9905 gral Nonlinearit −−−64202 wer− 85 Inte −−108 o P −12 80 −14 10 100 1000 −1 −0.8 −0.6 −0.4 −0.2 0 0.2 0.4 0.6 0.8 1 Frequency (Hz) Input (Normalized to Full−Scale) G007 G008 Figure7.PSRRvsFrequency Figure8.INLvsPGAGain Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 13 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com Typical Characteristics (continued) allplotsareatT =25°C,AVDD=3V,AVSS=0V,DVDD=1.8V,internalVREFP=2.4V,VREFN=AVSS,externalclock A =2.048MHz,datarate=8kSPS,andgain=1,unlessotherwisenoted. 24 0 −40°C PGA Gain = 1 +105°C −20 THD = −97 dB m) 16 +25°C −40 SNR = 117 dB y (pp 8 FS) −60 D16a3ta8 4R Patoei n=ts 1 kSPS nearit 0 e (dB −80 nli ud−100 No plit gral −8 Am−120 Inte −16 −140 −160 −24 −180 −1 −0.8 −0.6 −0.4 −0.2 0 0.2 0.4 0.6 0.8 1 0 100 200 300 400 500 Input (Normalized to Full−Scale) Frequency (Hz) G009 G010 Figure9.INLvsTemperature Figure10.THDFFTPlot 0 600 PGA Gain = 1 AVDD = 3 V −20 THD = −96 dB AVDD = 5 V 500 −40 SNR = 74 dB Data Rate = 64 kSPS S) −60 16384 Points 400 F de (dB −80 et (µV) 300 u−100 s plit Off m−120 200 A −140 100 −160 −180 0 0 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 1 2 3 4 5 6 7 8 9 10 11 12 Frequency (kHz) PGA Gain G011 G012 Figure11.FFTPlot Figure12.OffsetvsPGAGain(AbsoluteValue) 900 32 AVDD = 3 V AVDD = 3 V 800 AVDD = 5 V 28 AVDD = 5 V 700 24 V/°C) 600 W) 20 Drift (n 450000 wer (m 16 Offset 300 Po 12 8 200 100 4 0 0 1 2 3 4 5 6 7 8 9 10 11 12 0 1 2 3 4 5 6 7 8 PGA Gain Number of Channels Disabled G013 G014 Figure13.OffsetDriftvsPGAGain Figure14.ADS131E08ChannelPower 14 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 Typical Characteristics (continued) allplotsareatT =25°C,AVDD=3V,AVSS=0V,DVDD=1.8V,internalVREFP=2.4V,VREFN=AVSS,externalclock A =2.048MHz,datarate=8kSPS,andgain=1,unlessotherwisenoted. 2.406 2.404 2.402 V) 2.400 V(ref 2.398 2.396 2.394 2.392 –40 –15 10 35 60 85 110 Temperature ((cid:131)C) C001 Figure15.InternalV vsTemperature REF Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 15 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com 8 Parameter Measurement Information 8.1 Noise Measurements Adjust the data rate and PGA gain to optimize the ADS131E0x noise performance. When averaging is increased by reducing the data rate, noise drops correspondingly. Increasing the PGA gain reduces the input-referred noise, which is particularly useful when measuring low-level signals. Table 1 summarizes the ADS131E0x noise performancewitha3-Vanalogpowersupply.Table2summarizestheADS131E0xnoiseperformancewitha5-V analog power supply. Data are representative of typical noise performance at T = 25°C. Data shown are the A result of averaging the readings from multiple devices and are measured with the inputs shorted together. A minimum of 1000 consecutive readings are used to calculate the RMS noise for each reading. For the two highest data rates, noise is limited by the ADC quantization noise and does not have a Gaussian distribution. Table 1 and Table 2 show measurements taken with an internal reference. Data are representative of the ADS131E0x noise performance shown in both effective number of bits (ENOB) and dynamic range when using a low-noise external reference (such as the REF5025). ENOB data in Table 1 and Table 2 are calculated using Equation1anddynamicrangedatainTable1 andTable2arecalculatedusingEquation2. VREF ENOB log 2 2uV uGain RMS_Noise (1) VREF Dynamic Range 20ulog 10 2uV uGain RMS_Noise (2) Table1.Input-ReferredNoise,3-VAnalogSupply,and2.4-VReference PGAGAIN OUTPUT x1 x2 x4 x8 x12 DRBITS DATA –3-dB (CONFIG1 RATE BANDWIDTH DYNAMIC DYNAMIC DYNAMIC DYNAMIC DYNAMIC Register) (kSPS) (Hz) RANGE(dB) ENOB RANGE(dB) ENOB RANGE(dB) ENOB RANGE(dB) ENOB RANGE(dB) ENOB 000 64 16768 74.1 12.31 74.1 12.30 74.0 12.29 74.0 12.29 73.9 12.27 001 32 8384 89.6 14.89 89.6 14.88 89.4 14.85 88.6 14.71 87.6 14.55 010 16 4192 102.8 17.07 102.3 16.99 100.6 16.72 97.1 16.12 94.2 15.65 011 8 2096 108.2 18.0 107.4 17.9 105.2 17.5 101.6 16.9 98.9 16.5 100 4 1048 111.4 18.6 109.4 18.4 107.4 18.1 103.5 17.4 100.5 17.0 101 2 524 114.6 19.1 113.7 19.0 111.4 18.6 107.7 18.0 104.9 17.5 110 1 262 117.7 19.6 116.8 19.5 114.5 19.1 110.7 18.5 108.0 18.0 Table2.Input-ReferredNoise,5-VAnalogSupply,And4-VReference PGAGAIN OUTPUT DRBITS –3-dB DATA x1 x2 x4 x8 x12 (CONFIG1 BANDWIDTH RATE Register) (kSPS) (Hz) DYNAMIC ENOB DYNAMIC ENOB DYNAMIC ENOB DYNAMIC ENOB DYNAMIC ENOB RANGE(dB) RANGE(dB) RANGE(dB) RANGE(dB) RANGE(dB) 000 64 16768 74.7 12.41 74.7 12.41 74.7 12.41 74.7 12.41 74.6 12.39 001 32 8384 90.3 15.01 90.3 15.00 90.2 14.99 89.9 14.93 89.4 14.85 010 16 4192 104.3 17.33 104 17.28 103.1 17.12 100.5 16.70 98.1 16.3 011 8 2096 112.3 18.7 111.6 18.6 109.7 18.3 106.3 17.7 103.8 17.3 100 4 1048 116 19.3 115.2 19.2 113.1 18.8 109.5 18.3 106.9 17.8 101 2 524 119.1 19.8 118.2 19.7 116.2 19.4 112.6 18.8 109.9 18.3 110 1 262 122.1 20.4 121.3 20.2 119.1 19.9 115.6 19.3 112.9 18.8 16 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 9 Detailed Description 9.1 Overview The ADS131E0x series are low-power, multichannel, simultaneously-sampling, 24-bit, delta-sigma (ΔΣ), analog- to-digitalconverter(ADC)withanintegratedprogrammablegainamplifier(PGA).Theanalogdeviceperformance across a scalable data rate makes the device well-suited for smart-grid and other industrial power monitor, control,andprotectionapplications. The ADS131E0x devices have a programmable multiplexer that allows for various internal monitoring signal measurements including temperature, supply, and input-short for device noise testing. The PGA gain can be chosen from one of five settings: 1, 2, 4, 8, or 12. The ADCs in the device offer data rates of 1 kSPS, 2 kSPS, 4 kSPS, 8 kSPS, 16 kSPS, 32 kSPS, and 64 kSPS. The devices communicate using a serial peripheral interface (SPI)-compatible interface. The devices provide four general-purpose I/O (GPIO) pins for general use. Use multipledevicestoeasilyaddchannelstothesystemandsynchronizethemwiththeSTARTpins. Program the internal reference to either 2.4 V or 4 V. The internal oscillator generates a 2.048-MHz clock. Use the integrated comparators, with programmable trigger-points, for input overrange or underrange detection. A detaileddiagramoftheADS131E0xisprovidedin. Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 17 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com 9.2 Functional Block Diagram (cid:10)(cid:25)(cid:1)(cid:1) (cid:10)(cid:25)(cid:1)(cid:1) (cid:25)(cid:2)(cid:8)(cid:28)(cid:23) (cid:25)(cid:2)(cid:8)(cid:28)(cid:27) (cid:1)(cid:25)(cid:1)(cid:1) (cid:9)(cid:31)(cid:15)(cid:20)(cid:30)(cid:7)(cid:17)-)(cid:19)(cid:18) (cid:9)(cid:31)*((cid:31)(cid:22)(cid:19)(cid:20)(cid:29)(cid:22)(cid:31) (cid:2)(cid:31)+(cid:31)(cid:22)(cid:31))(cid:16)(cid:31) (cid:28)(cid:19)(cid:29)(cid:18)(cid:20)(cid:30)(cid:1)(cid:31)(cid:20)(cid:31)(cid:16)(cid:20) (cid:7)(cid:29)(((cid:18).(cid:30)(cid:4)/(cid:31)(cid:16)0 (cid:24)(cid:27) (cid:23) (cid:1)(cid:2)(cid:1)(cid:3) (cid:8)(cid:11)(cid:24) (cid:1)Σ (cid:28)(cid:17)(cid:18)(cid:20)(cid:31)(cid:22) (cid:23)(cid:26)(cid:10) ADC1 (cid:24)(cid:27) (cid:27) (cid:4)(cid:7) (cid:7)(cid:4)(cid:5)(cid:6) (cid:7)(cid:23)(cid:24) (cid:1)(cid:24)(cid:27) (cid:24)(cid:27)’(cid:23) (cid:1)(cid:14)(cid:12)(cid:9) (cid:8)(cid:11)(cid:24) (cid:1)Σ (cid:28)(cid:17)(cid:18)(cid:20)(cid:31)(cid:22) (cid:23)(cid:26)(cid:10)’ ADC2 (cid:24)(cid:27)’(cid:27) (cid:24)(cid:27)&(cid:23) (cid:8)(cid:11)(cid:24) (cid:1)Σ (cid:28)(cid:17)(cid:18)(cid:20)(cid:31)(cid:22) (cid:23)(cid:26)(cid:10)& ADC3 (cid:24)(cid:27)&(cid:27) (cid:4)(cid:5)(cid:6)(cid:7)(cid:8)(cid:5) (cid:24)(cid:27)%(cid:23) (cid:28)(cid:8)(cid:17)(cid:18)(cid:11)(cid:20)(cid:31)(cid:24)(cid:22) (cid:23)(cid:26)(cid:10)% AD(cid:1)ΣC4 (cid:4)(cid:21))(cid:20)(cid:22)(cid:21)(cid:18) (cid:14)(cid:15)(cid:16)(cid:17)(cid:18)(cid:18)(cid:19)(cid:20)(cid:21)(cid:22) (cid:4)(cid:5)(cid:6) (cid:24)(cid:27)%(cid:27) (cid:11)(cid:12)(cid:13) (cid:24)(cid:27)$(cid:23) (cid:26)(cid:23)(cid:24)(cid:14) (cid:8)(cid:11)(cid:24) (cid:1)Σ (cid:26)(cid:23)(cid:24)(cid:14)’ (cid:28)(cid:17)(cid:18)(cid:20)(cid:31)(cid:22) (cid:23)(cid:26)(cid:10)$ ADC5 (cid:26)(cid:23)(cid:24)(cid:14)& (cid:6)(cid:7)(cid:9)(cid:10)(cid:8) (cid:24)(cid:27)$(cid:27) (cid:26)(cid:23)(cid:24)(cid:14)% (cid:3)(cid:4)(cid:5)(cid:4) (cid:24)(cid:27)#(cid:23) (cid:2) (cid:1) (cid:8)(cid:11)(cid:24) (cid:1)Σ (cid:28)(cid:17)(cid:18)(cid:20)(cid:31)(cid:22) (cid:23)(cid:26)(cid:10)# ADC6 (cid:24)(cid:27)#(cid:27) (cid:23),(cid:1)(cid:27) (cid:24)(cid:27)"(cid:23) (cid:8)(cid:11)(cid:24) (cid:1)Σ (cid:28)(cid:17)(cid:18)(cid:20)(cid:31)(cid:22) (cid:23)(cid:26)(cid:10)" ADC7 (cid:2)(cid:8)(cid:7)(cid:8)(cid:9) (cid:6)(cid:7)(cid:8) (cid:24)(cid:27)"(cid:27) (cid:2)(cid:3)(cid:4)(cid:5)(cid:4) (cid:24)(cid:27)!(cid:23) (cid:7)(cid:9)(cid:10)(cid:2)(cid:9) (cid:1) (cid:8)(cid:11)(cid:24) (cid:1)Σ (cid:28)(cid:17)(cid:18)(cid:20)(cid:31)(cid:22) (cid:23)(cid:26)(cid:10)! ADC8 (cid:24)(cid:27)!(cid:27) (cid:14)((cid:31)(cid:22)(cid:19)(cid:20)(cid:17)(cid:21))(cid:19)(cid:18) (cid:10)*((cid:18)(cid:17)+(cid:17)(cid:31)(cid:22) (cid:10)(cid:25)(cid:7)(cid:7) (cid:10)(cid:25)(cid:7)(cid:7) (cid:14)(cid:23)(cid:10)(cid:11)(cid:23)(cid:14)(cid:12)(cid:9) (cid:14)(cid:23)(cid:10)(cid:11)(cid:23)(cid:27) (cid:14)(cid:23)(cid:10)(cid:11)(cid:23)(cid:23) (cid:1)(cid:26)(cid:27)(cid:1) 18 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 9.3 Feature Description 9.3.1 ElectromagneticInterference(EMI)Filter An RC filter at the input functions as an EMI filter on all channels. The –3-dB filter bandwidth is approximately 3MHz. 9.3.2 InputMultiplexer The ADS131E0x input multiplexers are very flexible and provide many configurable signal-switching options. Figure 16 shows a diagram of the multiplexer on a single channel of the device. INxP and INxN are separate for each of the four, six or eight blocks (depending on device). This flexibility allows for significant device and sub- system diagnostics, calibration, and configuration. Switch settings for each channel are selected by writing the appropriate values to the CHnSET registers (see the CHnSET registers in the Register Map section for details). TheoutputofeachmultiplexerisconnectedtotheindividualchannelPGA. Device INT_TEST MUX TESTP INT_TEST MUX[2:0] = 101 TestP MUX[2:0] = 100 TempP MUX[2:0] = 011 MvddP(1) MUX[2:0] = 000 INxP To PGA EMI MUX[2:0] = 001(VREFP + VREFN) Filter 2 MUX[2:0] = 000 MUX[2:0] = 001 INxN To PGA MUX[2:0] = 011 MvddN(1) MUX[2:0] = 100 TempN MUX[2:0] = 101 TestN INT_TEST TESTN INT_TEST (1) MVDDmonitorvoltagesupplydependsonchannelnumber;seethePower-SupplyMeasurements(MVDDP,MVDDN) section. Figure16. InputMultiplexerBlockforOneChannel Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 19 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com Feature Description (continued) 9.3.2.1 DeviceNoiseMeasurements SettingCHnSET[2:0]=001setsthecommon-modevoltageof[(V +V )/2]tobothchannelinputs.Use VREFP VREFN thissettingtotestinherentdevicenoiseintheusersystem. 9.3.2.2 TestSignals(TestPandTestN) Setting CHnSET[2:0] = 101 provides internally-generated test signals for use in sub-system verification at power- up. The test signals are controlled through register settings (see the CONFIG2: Configuration Register 2 section for details). TEST_AMP controls the signal amplitude and TEST_FREQ controls the switching frequency of the test signal. The test signals are multiplexed and transmitted out of the device at the TESTP and TESTN pins. The INT_TEST register bit (in the CONFIG2: Configuration Register 2 section) deactivates the internal test signals so that the test signal can be driven externally. This feature allows the test or calibration of multiple deviceswiththesamesignal. 9.3.2.3 TemperatureSensor(TempP,TempN) Setting CHnSET[2:0] = 100 sets the channel input to the temperature sensor. This sensor uses two internal diodes with one diode having a current density 16 times that of the other, as shown in Figure 17. The difference indiodecurrentdensitiesyieldsadifferenceinvoltagethatisproportionaltoabsolutetemperature. (cid:9)(cid:10)(cid:11)(cid:12)(cid:10)(cid:13)(cid:14)(cid:15)(cid:16)(cid:13)(cid:10)(cid:17)(cid:8)(cid:10)(cid:18)(cid:19)(cid:20)(cid:13)(cid:17)(cid:21)(cid:20)(cid:18)(cid:22)(cid:15)(cid:20)(cid:13) (cid:5)(cid:6)(cid:7)(cid:7) (cid:3)(cid:2) (cid:1)(cid:2) (cid:9)(cid:20)(cid:17)(cid:21)(cid:23)(cid:24)(cid:17)(cid:9)(cid:10)(cid:11)(cid:12)(cid:25) (cid:9)(cid:20)(cid:17)(cid:21)(cid:23)(cid:24)(cid:17)(cid:9)(cid:10)(cid:11)(cid:12)(cid:26) (cid:4)(cid:2) (cid:3)(cid:2) (cid:5)(cid:6)(cid:8)(cid:8) Figure17. TemperatureSensorImplementation TheinternaldevicetemperaturetracksthePCBtemperaturecloselybecauseofthelowthermalresistanceofthe package to the PCB. Self-heating of the ADS131E0x causes a higher reading than the temperature of the surroundingPCB.Settingthechannelgainto1isrecommendedwhenthetemperaturemeasurementistaken. The scale factor of Equation 3 converts the temperature reading to °C. Before using this equation, the temperaturereadingcodemustfirstbescaledtoμV. Temperature Reading (mV)-145,300mV Temperature (°C) = + 25°C 490mV/°C (3) 9.3.2.4 Power-SupplyMeasurements(MVDDP,MVDDN) SettingCHnSET[2:0]=011setsthechannelinputstodifferentdevicesupplyvoltages.Forchannels1,2,5,6,7, and 8 (MVDDP – MVDDN) is [0.5 × (AVDD – AVSS)]; for channels 3 and 4 (MVDDP – MVDDN) is DVDD/4.Setthegainto1toavoidsaturatingthePGAwhenmeasuringpowersupplies. 20 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 Feature Description (continued) 9.3.3 AnalogInput The analog inputs to the device connect directly to an integrated low-noise, low-drift, high input impedance, programmablegainamplifier.Theamplifierislocatedfollowingtheindividualchannelmultiplexer. The ADS131E0x analog inputs are fully differential. The differential input voltage (V – V ) can span from INxP INxN –V /gaintoV /gain.SeetheDataFormat sectionforanexplanationofthecorrelationbetweentheanalog REF REF input and digital codes. There are two general methods of driving the ADS131E0x analog inputs: pseudo- differentialorfully-differential,asshowninFigure18,Figure19,andFigure20. (cid:16)VREF / Gain VREF / Gain to Device Peak-to-Peak V / Gain REF Device Common Common VREF / Gain Voltage Voltage Peak-to-Peak a) Psuedo-Differential Input b) Differential Input Figure18. MethodsofDrivingtheADS131E0x:Pseudo-DifferentialorFullyDifferential INxP INxP INxN VCM VCM INxN Figure19.Pseudo-DifferentialInputMode Figure20.Fully-DifferentialInputMode Hold the INxN pin at a common voltage, preferably at mid supply, to configure the fully differential input for a pseudo-differentialsignal.SwingtheINxPpinaroundthecommonvoltage –V /gaintoV /gainandremain REF REF within the absolute maximum specifications. Verify that the differential signal at the minimum and maximum pointsmeetsthecommon-modeinputspecificationdiscussedintheInputCommon-ModeRange section. Configure the signals at INxP and INxN to be 180° out-of-phase centered around a common-mode voltage, V , CM to use a fully-differential input method. Both the INxP and INxN inputs swing from the V + ½ V / gain to the CM REF V – ½ V / gain. The differential voltage at the maximum and minimum points is equal to –V / gain to CM REF REF V / gain. Use the ADS131E0x in a differential configuration to maximize the dynamic range of the data REF converter. For optimal performance, the common-mode voltage is recommended to be set at the midpoint of the analogsupplies[(AVDD+AVSS)/2]. If any of the analog input channels are not used, then power-down these pins using register bits to conserve power. See the SPI Command Definitions section for more information on how to power-down individual channels.TieanyunusedorpowereddownanaloginputpinsdirectlytoAVDD. Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 21 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com 9.3.4 PGASettingsandInputRange Each channel has its own configurable programmable gain amplifier (PGA) following its multiplexer. The PGA is designed using two operational amplifiers in a differential configuration, as shown in Figure 21. Set the gain to one of five settings (1, 2, 4, 8, and 12) using the CHnSET registers for each individual channel (see the CHnSET registersintheRegisterMapsectionfordetails).TheADS131E0xhasCMOSinputsandthereforehasnegligible currentnoise.Table3showsthetypicalsmall-signalbandwidthvaluesforvariousgainsettings. From Mux Amp R2 30 k(cid:13) R1 60 k(cid:13) To ADC (for Gain = 2) R2 30 k(cid:13) Amp From Mux Figure21. PGAImplementation Table3.PGAGainversusBandwidth GAIN NOMINALBANDWIDTHATT =25°C(kHz) A 1 237 2 146 4 96 8 48 12 32 The PGA resistor string that implements the gain has 120 kΩ of resistance for a gain of 2. This resistance provides a current path across the PGA outputs in the presence of a differential input signal. This current is in additiontothequiescentcurrentspecifiedforthedeviceinthepresenceofadifferentialsignalattheinput. 22 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 9.3.4.1 InputCommon-ModeRange The usable input common-mode range of the analog front-end depends on various parameters, including the maximum differential input signal, supply voltage, and PGA gain. The common-mode range, V , is defined in CM Equation4: Gain´V Gain´V AVDD-0.3 V- MAX_DIFF > V >AVSS + 0.3 V + MAX_DIFF 2 CM 2 where: • V =maximumdifferentialsignalatthePGAinputand MAX_DIFF • V =common-modevoltage (4) CM Forexample: IfAVDD– AVSS=3.3V,gain=2,andV =1000mV, MAX_DIFF Then1.3V< V <2.0V CM 9.3.5 ΔΣ Modulator Each ADS131E0x channel has its own delta-sigma (ΔΣ) ADC. The ΔΣ converters use second-order modulators optimized for low-power applications. The modulator samples the input signal at the modulator rate of (f = MOD f /2).Aswithany ΔΣmodulator,theADS131E0xnoiseisshapeduntilf /2,asshowninFigure22. CLK MOD 0 −10 −20 B) −30 sity (d −−5400 n −60 e D −70 al −80 ctr −90 pe−100 S wer −−112100 Po−130 −140 −150 −160 0.001 0.01 0.1 1 Normalized Frequency (fIN/fMOD) G001 Figure22. ModulatorNoiseSpectrumUpto0.5 ×f MOD 9.3.6 Clock The ADS131E0x provides two different device clocking methods: internal and external. Internal clocking using the internal oscillator is ideally-suited for non-synchronized, low-power systems. The internal oscillator is trimmed for accuracy at room temperature. The accuracy of the internal oscillator varies over the specified temperature range; see the Electrical Characteristics table for details. External clocking is recommended when synchronizing multiple ADS131E0x devices or when synchronizing to an external event because the internal oscillator clock performance can vary over temperature. Clock selection is controlled by the CLKSEL pin and the CLK_EN registerbit.Providetheexternalclockanytimeaftertheanaloganddigitalsuppliesarepresent. Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 23 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com The CLKSEL pin selects either the internal oscillator or external clock. The CLK_EN bit in the CONFIG1 register enables and disables the oscillator clock to be output on the CLK pin. A truth table for the CLKSEL pin and the CLK_EN bit is shown in Table 4. The CLK_EN bit is useful when multiple devices are used in a daisy-chain configuration.Duringpower-down,theexternalclockisrecommendedtobeshutdowntosavepower. Table4.CLKSELPinandCLK_ENBit CLKSELPIN CLK_ENBIT CLOCKSOURCE CLKPINSTATUS 0 X Externalclock Input:externalclock 1 0 Internaloscillator 3-state 1 1 Internaloscillator Output:internaloscillator 9.3.7 DigitalDecimationFilter The digital filter receives the modulator output bit stream and decimates the data stream. The decimation ratio determines the number of samples taken to create the output data word, and is set by the modulator rate divided by the data rate (f / f ). By adjusting the decimation ratio, a tradeoff can be made between resolution and MOD DR data rate: higher decimation allows for higher resolution (thus creating lower data rates) and lower decimation decreases resolution but enables wider bandwidths with higher data rates. Higher data rates are typically used in power applications that implement software re-sampling techniques to help with channel-to-channel phase adjustmentforvoltageandcurrent. The digital filter on each channel consists of a third-order sinc filter. An input step change takes three conversion cycles for the filter to settle. Adjust the decimation ratio of the sinc3 filters using the DR[2:0] bits in the CONFIG1 register (see the Register Map section for details). The data rate setting is a global setting that sets all channels tothesamedatarate. The sinc filter is a variable decimation rate, third-order, low-pass filter. Data are supplied to this section of the filter from the modulator at the rate of f . The sinc3 filter attenuates the high-frequency modulator noise, then MOD decimatesthedatastreamintoparalleldata.Thedecimationrateaffectstheoverallconverterdatarate. Equation5showsthescaledsinc3filterZ-domaintransferfunction. 1-Z-N 3 ½H(z)½= 1-Z-1 (5) Thesinc3filterfrequencydomaintransferfunctionisshowninEquation6. 3 Npf sin f MOD H(f) = pf N´sin f MOD where: • N=decimationratio (6) The sinc3 filter has notches (or zeroes) that occur at the output data rate and multiples thereof. At these frequencies, the filter has infinite attenuation. Figure 23 illustrates the sinc filter frequency response and Figure24illustratesthesincfilterroll-off.Figure25 andFigure26illustratethefiltertransferfunctionuntilf /2 MOD andf /16,respectively,atdifferentdatarates.Figure27illustratesthetransferfunctionextendeduntil4f . MOD MOD Figure 27 illustrates that the ADS131E0x passband repeats itself at every f . Note that the digital filter MOD responseandfilternotchesareproportionaltothemasterclockfrequency. 24 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 0 0 -20 -0.5 -40 -1 B) -60 B) d d n ( n ( -1.5 Gai -80 Gai -2 -100 -120 -2.5 -140 -3 0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 Normalized Frequency (f /f ) Normalized Frequency (f /f ) IN DR IN DR Figure23.SincFilterFrequencyResponse Figure24. SincFilterRoll-Off 0 0 DR[2:0] = 110 DR[2:0] = 110 -20 -20 DR[2:0] = 000 DR[2:0] = 000 -40 -40 dB) -60 dB) -60 n ( n ( Gai -80 Gai -80 -100 -100 -120 -120 -140 -140 0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5 0 0.01 0.02 0.03 0.04 0.05 0.06 0.07 Normalized Frequency (f /f ) Normalized Frequency (f /f ) IN MOD IN MOD Figure25.TransferFunctionofDecimationFiltersUntil Figure26.TransferFunctionofDecimationFiltersUntil fMOD/2 fMOD/16 10 DR[2:0] = 000 DR[2:0] = 110 -10 -30 B) -50 d n ( Gai -70 -90 -110 -130 0 0.5 1 1.5 2 2.5 3 3.5 4 Normalized Frequency (f /f ) IN MOD Figure27. TransferFunctionofDecimationFilters Until4f forDR[2:0]=000andDR[2:0]=110 MOD Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 25 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com 9.3.8 VoltageReference Figure 28 shows a simplified block diagram of the internal ADS131E0x reference. The reference voltage is generatedwithrespecttoAVSS.Whenusingtheinternalvoltagereference,connectVREFNtoAVSS. 22 (cid:29)F VCAP1 (1) R1 Bandgap 2.4 V or 4 V VREFP (1) R3 10 (cid:29)F R2(1) VREFN AVSS To ADC Reference Inputs ForV =2.4V:R1=12.5kΩ,R2=25kΩ,andR3=25kΩ. REF ForV =4V:R1=10.5kΩ,R2=15kΩ,andR3=35kΩ. REF Figure28. InternalReference The external band-limiting capacitors determine the amount of reference noise contribution. For high-end systems, the capacitor values should be chosen such that the bandwidth is limited to less than 10 Hz, so that the reference noise does not dominate the system noise. When using a 3-V analog supply, the internal reference must be set to 2.4 V. In case of a 5-V analog supply, the internal reference can be set to 4 V by setting the VREF_4VbitintheCONFIG2register. Alternatively, the internal reference buffer can be powered down and VREFP can be driven externally. Figure 29 shows a typical external reference drive circuit. Power-down is controlled by the PD_REFBUF bit in the CONFIG3 register. This power-down is also used to share internal references when two devices are cascaded. Bydefault,thedevicewakesupinexternalreferencemode. 100 k(cid:13) 22 nF +5 V 0.1 (cid:29)F 10 (cid:13) 100 (cid:13) OPA350 To VREFP Pin +5 V VIN OUT 10 (cid:29)F 0.1 (cid:29)F REF5025 10 (cid:29)F 100 (cid:29)F 1 (cid:29)F TRIM Figure29. ExternalReferenceDriver 26 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 9.3.9 InputOut-of-RangeDetection The ADS131E0x has integrated comparators to detect out-of-range conditions on the input signals. The basic principle is to compare the input voltage against a threshold voltage set by a 3-bit digital-to-analog converter (DAC) based off the analog power supply. The comparator trigger threshold level is set by the COMP_TH[2:0] bitsintheFAULTregister. If the ADS131E0x is powered from a ±2.5-V supply and COMP_TH[2:0] = 000 (95% and 5%), the high-side trigger threshold is set at 2.25 V [equal to AVSS + (AVDD – AVSS) × 95%] and the low-side threshold is set at –2.25 V [equal to AVSS + (AVDD – AVSS) × 5%]. The threshold calculation formula applies to unipolar as well astobipolarsupplies. A fault condition can be detected by setting the appropriate threshold level using the COMP_TH[2:0] bits. To determine which of the inputs is out of range, read the FAULT_STATP and FAULT_STATN registers individually orreadtheFAULT_STATxbitsaspartoftheoutputdatastream;seetheDataOutput(DOUT) section. 9.3.10 General-PurposeDigitalI/O(GPIO) The ADS131E0x has a total of four general-purpose digital I/O (GPIO) pins available. Configure the digital I/O pinsaseitherinputsoroutputsthroughtheGPIOCbits.TheGPIODbitsintheGPIOregisterindicatethelevelof the pins. The GPIO logic high voltage level is set by the voltage level of DVDD. When reading the GPIOD bits, the data returned are the logic level of the pins, whether they are programmed as inputs or outputs. When the GPIOpinisconfiguredasaninput,awritetothecorrespondingGPIODbithasnoeffect.Whenconfiguredasan output,awritetotheGPIODbitsetstheoutputlevel. If configured as inputs, the GPIO pins must be driven to a defined state. The GPIO pins are set as inputs after power up or after a reset. Figure 30 shows the GPIO pin structure. Connect unused GPIO pins directly to DGND through10-kΩresistors. (cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:8)(cid:9)(cid:10)(cid:9)(cid:5)(cid:11)(cid:12)(cid:13)(cid:9)(cid:14)(cid:15) (cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:2)(cid:6)(cid:7) (cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:8)(cid:9)(cid:10)(cid:9)(cid:5)(cid:11)(cid:16)(cid:17)(cid:6)(cid:10)(cid:13)(cid:15) (cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:18)(cid:19)(cid:7)(cid:10)(cid:17)(cid:19)(cid:20) Figure30. GPIOPinImplementation Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 27 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com 9.4 Device Functional Modes 9.4.1 Start Pull the START pin high for at least 2 t periods, or send the START command to begin conversions. When CLK START is low and the START command has not been sent, the device does not issue a DRDY signal (conversionsarehalted). When using the START command to control conversions, hold the START pin low. In multiple device configurations, the START pin is used to synchronize devices (see the Multiple Device Configuration subsection formoredetails). 9.4.1.1 SettlingTime The settling time (t ) is the time required for the converter to output fully-settled data when the START SETTLE signal is pulled high. When START is pulled high, DRDY is also pulled high. The next DRDY falling edge indicates that data are ready. Figure 31 shows the timing diagram and Table 5 shows the settling time for differentdataratesasafunctionoft .Thesettlingtimedependsonf andthedecimationratio(controlledby CLK CLK the DR[2:0] bits in the CONFIG1 register). When the initial settling time has passed, the DRDY falling edge occurs at the set data rate, t . If data is not read back on DOUT and the output shift register needs to update, DR DRDYgoeshighfor4t beforereturningbacklowindicatingnewdataisready.NotethatwhenSTARTisheld CLK high and there is a step change in the input signal, 3 × t is required for the filter to settle to the new value. DR SettleddataareavailableonthefourthDRDYpulse. STARTPin t SETTLE or DIN START t DR 4 / f CLK DRDY Figure31. SettlingTime Table5.SettlingTimeforDifferentDataRates DR[2:0] NORMALMODE UNIT 000 152 t CLK 001 296 t CLK 010 584 t CLK 011 1160 t CLK 100 2312 t CLK 101 4616 t CLK 110 9224 t CLK 9.4.1.2 InputSignalStep When the device is converting and there is a step change on the input signal, a delay of 3 t is required for the DR output data to settle. Settled data are available on the fourth DRDY pulse. Data are available to read at each DRDY low transition prior to the 4th DRDY pulse, but are recommended to be ignored. Figure 32 shows the requiredwaittimeforcompletesettlingforaninputsteporinputtransienteventontheanaloginput. 28 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 Device Functional Modes (continued) START Analog Input Transient Input DRDY 4 x tDR Figure32. SettlingTimefortheInputTransient 9.4.2 Reset(RESET) There are two methods to reset the ADS131E0x: pull the RESET pin low, or send the RESET command. When using the RESET pin, make sure to follow the minimum pulse duration timing specifications before taking the pin back high. The RESET command takes effect on the eighth SCLK falling edge of the command. After a reset, 18 t cycles are required to complete initialization of the configuration registers to default states and start the CLK conversion cycle. Note that an internal reset is automatically issued to the digital filter whenever the CONFIG1 registerissettoanewvaluewithaWREGcommand. 9.4.3 Power-Down(PWDN) When PWDN is pulled low, all on-chip circuitry is powered down. To exit power-down mode, take the PWDN pin high. Upon exiting from power-down mode, the internal oscillator and the reference require time to wake up. Duringpower-down,theexternalclockisrecommendedtobeshutdowntosavepower. 9.4.4 ContinuousConversionMode Conversions begin when the START pin is taken high or when the START command is sent. As shown in Figure 33, the DRDY output goes high when conversions are started and goes low when data are ready. Conversions continue indefinitely until the START pin is taken low or the STOP command is transmitted. When the START pin is pulled low or the STOP command is issued, the conversion in progress is allowed to complete. Figure 34 and Table 6 show the required DRDY timing to the START pin or the START and STOP commands whencontrollingconversionsinthismode.Thet timingindicateswhentotaketheSTARTpinloworwhento SDSU send the STOP command before the DRDY falling edge to halt further conversions. The t timing indicates DSHD when to take the START pin low or send the STOP command after a DRDY falling edge to complete the current conversion and halt further conversions. To keep the converter running continuously, the START pin can be permanentlytiedhigh. START Pin or or START(1) STOP(1) DIN Command Command tDR DRDY tSETTLE (1) STARTandSTOPcommandstakeeffectontheseventhSCLKfallingedge. Figure33. ContinuousConversionMode Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 29 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com Device Functional Modes (continued) (cid:1) (cid:11)(cid:12)(cid:11)(cid:13) (cid:14)(cid:15)(cid:9)(cid:5)(cid:11)(cid:3)(cid:16)(cid:2) (cid:2)(cid:3)(cid:2)(cid:4) (cid:1) (cid:3)(cid:2)(cid:5)(cid:3) (cid:1)(cid:2)(cid:17)(cid:12)(cid:2)(cid:5)(cid:4)(cid:18)(cid:15) (cid:8)(cid:19) (cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:3)(cid:6)(cid:7)(cid:8)(cid:9)(cid:10) (cid:1)(cid:2)(cid:3)(cid:4)(cid:20)(cid:21)(cid:22) (cid:1)(cid:2)(cid:3)(cid:4)(cid:20)(cid:21)(cid:22) (1) STARTandSTOPcommandstakeeffectontheseventhSCLKfallingedgeattheendofthetransmission. Figure34. STARTtoDRDYTiming Table6.TimingCharacteristicsforFigure34(1) MIN UNIT Setuptime:STARTpinloworSTOPcommandbeforetheDRDYfallingedgeto t 16 t SDSU haltfurtherconversions CLK Delaytime:STARTpinloworSTOPcommandtocompletethecurrent t 16 t DSHD conversionandhaltfurtherconversions CLK (1) STARTandSTOPcommandstakeeffectontheseventhSCLKfallingedgeattheendofthetransmission. 9.4.5 DataRetrieval 9.4.5.1 DataReady(DRDY) DRDY is an output signal which transitions from high to low indicating new conversion data are ready. The CS signalhasnoeffectonthedatareadysignal. DRDYbehaviorisdeterminedbywhetherthedeviceisinRDATAC mode or the RDATA command is used to read data on demand. (See the RDATAC: Start Read Data Continuous ModeandRDATA:ReadDatasubsectionsoftheSPICommandDefinitions sectionforfurtherdetails). When reading data with the RDATA command, the read operation can overlap the next DRDY occurrence withoutdatacorruption. The START pin or the START command places the device either in normal data capture mode or pulse data capturemode. Figure 35 shows the relationship between CS, DRDY, DOUT, and SCLK during data retrieval (in case of an ADS131E0x). DOUT is latched out at the SCLK rising edge. DRDY is pulled high at the SCLK falling edge. Note that DRDY goes high on the first SCLK falling edge, regardless of whether data are being retrieved from the deviceoracommandisbeingsentthroughtheDINpin. CS DRDY SCLK DOUT MSB MSB-1 MSB-2 Figure35. DRDYBehaviorwithDataRetrieval 30 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 The DRDY signal is cleared on the first SCLK falling edge regardless of the state of CS. This condition must be taken into consideration if the SPI bus is used to communicate with other devices on the same bus. Figure 36 shows a behavior diagram for DRDY when SCLKs are sent with CS high. Figure 36 shows that no data are clockedout,buttheDRDYsignaliscleared. CS DRDY SCLK Figure36. DRDYandSCLKBehaviorwhen CSisHigh 9.4.5.2 ReadingBackData Dataretrievalcanbeaccomplishedinoneoftwomethods: 1. RDATAC:thereaddatacontinuouscommandsetsthedeviceinamodethatreadsdatacontinuouslywithout sendingcommands.SeetheRDATAC:StartReadDataContinuousMode sectionformoredetails. 2. RDATA: the read data command requires that a command is sent to the device to load the output shift registerwiththelatestdata.SeetheRDATA:ReadDatasectionformoredetails. Conversion data are read by shifting data out on DOUT. The MSB of the data on DOUT is clocked out on the first SCLK rising edge. DRDY returns high on the first SCLK falling edge. DIN should remain low for the entire readoperation. 9.4.5.3 StatusWord AstatuswordprecedesdatareadbackandprovidesinformationonthestateoftheADS131E0x.Thestatusword is 24 bits long and contains the values for FAULT_STATP, FAULT_STATN, and the GPIO data bits. The content alignmentisshowninFigure37. SCLK § § § (cid:3) (cid:3) (cid:3) § § § DOUT 1 1 0 0 FAULT_STA(cid:3)TP[7:0] FAULT_STAT(cid:3)N[7:0] GPIO(cid:3)[7:4] § § § (cid:3) (cid:3) (cid:3) Figure37. StatusWordContent NOTE The status word length is always 24 bits. The length does not change for 32-kSPS and 64-kSPSdatarates. Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 31 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com 9.4.5.4 ReadbackLength The number of bits in the data output depends on the number of channels and the number of bits per channel. ThedataformatforeachchanneldataaretwoscomplementandMSBfirst. For the ADS131E0x with 32-kSPS and 64-kSPS data rates, the number of data bits is: 24 status bits + 16 bits perchannel× 8channels=152bits. Forallotherdatarates,thenumberofdatabitsis:24statusbits+24bitsperchannel × 8channels=216bits. When channels are powered down using the user register setting, the corresponding channel output is set to 0. However,thesequenceofchanneloutputsremainsthesame. The ADS131E0x also provides a multiple data readback feature. Data can be read out multiple times by simply providing more SCLKs, in which case the MSB data byte repeats after reading the last byte. The DAISY_IN bit in theCONFIG1registermustbesetto1formultiplereadbacks. 32 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 9.5 Programming 9.5.1 DataFormat The DR[2:0] bits in the CONFIG1 register sets the output resolution for the ADS131E0x. When DR[2:0] = 000 or 001, the 16 bits of data per channel are sent in binary twos complement format, MSB first. The size of one code (LSB)iscalculatedusingEquation7. 1LSB=(2×V /Gain)/216=FS/215 (7) REF A positive full-scale input [V ≥ (FS – 1 LSB) = (V / Gain – 1 LSB)] produces an output code of 7FFFh and a IN REF negative full-scale input (V ≤ –FS = –V / Gain) produces an output code of 8000h. The output clips at these IN REF codesforsignalsthatexceedfull-scale. Table7summarizestheidealoutputcodesfordifferentinputsignals. Table7.16-BitIdealOutputCodeversusInputSignal INPUTSIGNAL,VIN IDEALOUTPUTCODE(1) V -V (IN×P) (IN×N) ≥FS(215–1)/215 7FFFh FS/215 0001h 0 0000h –FS/215 FFFFh ≤–FS 8000h (1) Excludestheeffectsofnoise,INL,offset,andgainerrors. When DR[2:0] = 010, 011, 100, 101, or 110, the ADS131E0x outputs 24 bits of data per channel in binary twos complementformat,MSBfirst.Thesizeofonecode(LSB)iscalculatedusingEquation8. 1LSB=(2×V /Gain)/224=FS/223 (8) REF A positive full-scale input [V ≥ (FS – 1 LSB) = (V / Gain – 1 LSB)] produces an output code of 7FFFFFh and IN REF a negative full-scale input (V ≤ –FS = –V / Gain) produces an output code of 800000h. The output clips at IN REF thesecodesforsignalsthatexceedfull-scale. Table8summarizestheidealoutputcodesfordifferentinputsignals. Table8.24-BitIdealOutputCodeversusInputSignal INPUTSIGNAL,V IN V -V IDEALOUTPUTCODE(1) (INxP) (INxN) ≥FS(223–1)/223 7FFFFFh FS/223 000001h 0 000000h –FS/223 FFFFFFh ≤–FS 800000h (1) Excludestheeffectsofnoise,INL,offset,andgainerrors. 9.5.2 SPIInterface The SPI-compatible serial interface consists of four signals: CS, SCLK, DIN, and DOUT. The interface is used to read conversion data, read and write registers, and control the ADS131E0x operation. The DRDY output is used as a status signal to indicate when ADC data are ready for readback. DRDY goes low when new data are available. 9.5.2.1 ChipSelect(CS) The CS pin activates SPI communication. CS must be low before data transactions and must stay low for the entire SPI communication period. When CS is high, the DOUT pin enters a high-impedance state. Therefore, reading and writing to the serial interface are ignored and the serial interface is reset. DRDY pin operation is independent of CS. DRDY still indicates that a new conversion has completed and is forced high as a response toSCLK,evenif CSishigh. Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 33 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 SBAS561C–JUNE2012–REVISEDJANUARY2017 www.ti.com Taking CS high deactivates only the SPI communication with the device and the serial interface is reset. Data conversion continues and the DRDY signal can be monitored to check if a new conversion result is ready. A master device monitoring the DRDY signal can select the appropriate slave device by pulling the CS pin low. Aftertheserialcommunicationisfinished,alwayswaitfourormoret cyclesbeforetaking CShigh. CLK 9.5.2.2 SerialClock(SCLK) SCLK provides the clock for serial communication. SCLK is a Schmitt-trigger input, but TI recommends keeping SCLK as free from noise as possible to prevent glitches from inadvertently shifting the data. Data are shifted into DINonthefallingedgeofSCLKandshiftedoutofDOUTontherisingedgeofSCLK. The absolute maximum SCLK limit is specified in Figure 1. When shifting in commands with SCLK, make sure thattheentiresetofSCLKsisissuedtothedevice.Failuretodosocanresultinthedeviceserialinterfacebeing placedintoanunknownstaterequiring CStobetakenhightorecover. For a single device, the minimum speed required for SCLK depends on the number of channels, number of bits ofresolution,andoutputdatarate.(Formultipledevices,seetheMultipleDeviceConfiguration section.) For example, if the ADS131E0x is used with an 8-kSPS mode (24-bit resolution), the minimum SCLK speed is 1.755MHztoshiftoutallthedata. Data retrieval can be accomplished either by placing the device in RDATAC mode or by issuing an RDATA command for data on demand. The SCLK rate limitation in Equation 9 applies to RDATAC. For the RDATA command, the limitation applies if data must be read in between two consecutive DRDY signals. Equation 9 assumesthattherearenoothercommandsissuedinbetweendatacaptures. t <(t –4t )/(N ×8+24) SCLK DR CLK BITS where • N =resolutionofdataforthecurrentdatarate;16or24 (9) BITS 9.5.2.3 DataInput(DIN) DIN is used along with SCLK to send data to the device. Data on DIN are shifted into the device on the falling edgeofSCLK. The communication of this device is full-duplex in nature. The device monitors commands shifted in even when data are being shifted out. Data that are present in the output shift register are shifted out when sending in a command.Therefore,makesurethatwhateverisbeingsentontheDINpinisvalidwhenshiftingoutdata.When no command is to be sent to the device when reading out data, send the NOP command on DIN. Make sure that thet timingismetintheSendingMultibyteCommandssectionwhensendingmultiplebytecommandson SDECODE DIN. 9.5.2.4 DataOutput(DOUT) DOUT is used with SCLK to read conversion and register data from the device. Data are clocked out on the rising edge of SCLK, MSB first. DOUT goes to a high-impedance state when CS is high. In read data continuous mode (see the SPI Command Definitions section for more details), the DOUT output line can also be used to indicate when new data are available. If CS is low when new data are ready, a high-to-low transition on the DOUT line occurs synchronously with a high-to-low transition on DRDY, as shown in Figure 38. This feature can beusedtominimizethenumberofconnectionsbetweenthedeviceandsystemcontroller. CS DOUT Data DRDY Figure38. UsingDOUTas DRDY 34 SubmitDocumentationFeedback Copyright©2012–2017,TexasInstrumentsIncorporated ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08

ADS131E04,ADS131E06,ADS131E08 www.ti.com SBAS561C–JUNE2012–REVISEDJANUARY2017 9.5.3 SPICommandDefinitions The ADS131E0x provides flexible configuration control. The commands, summarized in Table 9, control and configure device operation. The commands are stand-alone, except for the register read and register write operations that require a second command byte to include additional data. CS can be taken high or held low between commands but must stay low for the entire command operation (including multibyte commands). System commands and the RDATA command are decoded by the ADS131E0x on the seventh SCLK falling edge. The register read and write commands are decoded on the eighth SCLK falling edge. Be sure to follow the SPItimingrequirementswhenpulling CShighafterissuingacommand. Table9.CommandDefinitions COMMAND DESCRIPTION FIRSTBYTE SECONDBYTE SYSTEMCOMMANDS WAKEUP Wake-upfromstandbymode 00000010(02h) STANDBY Enterstandbymode 00000100(04h) RESET Resetthedevice 00000110(06h) START Startorrestart(synchronize)conversions 00001000(08h) STOP Stopconversions 00001010(0Ah) OFFSETCAL Channeloffsetcalibration 00011010(1Ah) DATAREADCOMMANDS Enablereaddatacontinuousmode. RDATAC Thismodeisthedefaultmodeatpower-up.(1) 00010000(10h) SDATAC Stopreaddatacontinuousmode 00010001(11h) RDATA Readdatabycommand 00010010(12h) REGISTERREADCOMMANDS RREG Readnnnnnregistersstartingataddressrrrrr 001rrrrr(2xh)(2) 000nnnnn(2) WREG Writennnnnregistersstartingataddressrrrrr 010rrrrr(4xh)(2) 000nnnnn(2) (1) WheninRDATACmode,theRREGcommandisignored. (2) nnnnn=numberofregisterstobereadorwritten–1.Forexample,toreadorwritethreeregisters,setnnnnn=0(0010).rrrrr=the startingregisteraddressforreadandwritecommands. 9.5.3.1 SendingMultibyteCommands The ADS131E0x serial interface decodes commands in bytes and requires 4 t cycles to decode and execute CLK each command. Therefore, when sending multi-byte commands (such as RREG or WREG), a 4 t period must CLK separatetheendofonebyte(orcommand)andthenext. Assuming CLK is 2.048 MHz, then t (4 t ) is 1.96 µs. When SCLK is 16 MHz, one byte can be SDECODE CLK transferred in 0.5 µs. This byte transfer time does not meet the t specification; therefore, a delay of 1.46 SDECODE µs(1.96 µs–0.5 µs)mustbeinsertedafterthefirstbyteandbeforethesecondbyte.IfSCLKis4MHz,onebyte is transferred in 2 µs. Because this transfer time exceeds the t specification (2 µs > 1.96 µs), the SDECODE processorcansendsubsequentbyteswithoutdelay. 9.5.3.2 WAKEUP:ExitSTANDBYMode The WAKEUP command exits the low-power standby mode; see the STANDBY: Enter STANDBY Mode section. Be sure to allow enough time for all circuits in standby mode to power-up (see the Electrical Characteristics table for details). There are no SCLK rate restrictions for this command and it can be issued at any time. There are no SCLK rate restrictions for this command and can be issued at any time. Any following commands must be sent afteradelayof4t cycles. CLK 9.5.3.3 STANDBY:EnterSTANDBYMode TheSTANDBYcommandenterslow-powerstandbymode.Allcircuitsinthedevicearepowereddownexceptfor the reference section. The standby mode power consumption is specified in the Electrical Characteristics table. There are no SCLK rate restrictions for this command and can be issued at any time. Do not send any other commandsotherthantheWAKEUPcommandafterthedeviceentersstandbymode. Copyright©2012–2017,TexasInstrumentsIncorporated SubmitDocumentationFeedback 35 ProductFolderLinks:ADS131E04 ADS131E06 ADS131E08