ICGOO在线商城 > TPS54980PWP

- 型号: TPS54980PWP

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

TPS54980PWP产品简介:

ICGOO电子元器件商城为您提供TPS54980PWP由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 提供TPS54980PWP价格参考¥21.81-¥36.57以及Texas InstrumentsTPS54980PWP封装/规格参数等产品信息。 你可以下载TPS54980PWP参考资料、Datasheet数据手册功能说明书, 资料中有TPS54980PWP详细功能的应用电路图电压和使用方法及教程。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

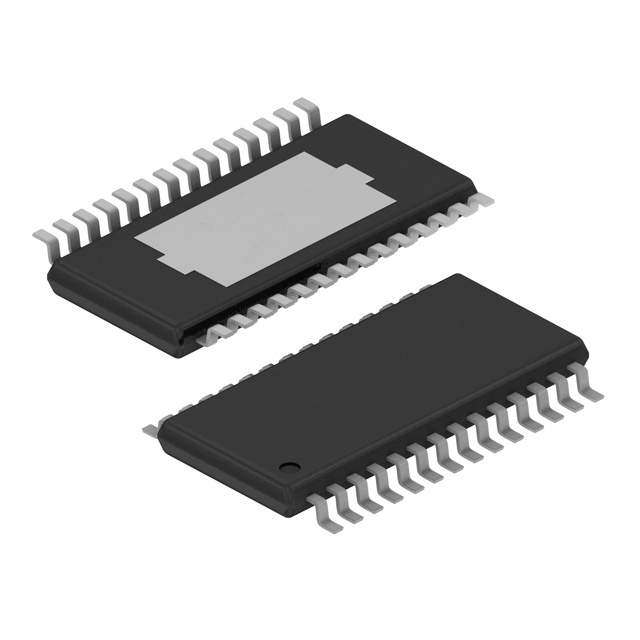

| 描述 | IC REG BUCK SYNC ADJ 9A 28HTSSOP稳压器—开关式稳压器 3.3V Inp Sync Buck Converter |

| DevelopmentKit | TPS54980EVM-022 |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 产品手册 | http://www.ti.com/litv/slvs452a |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 电源管理 IC,稳压器—开关式稳压器,Texas Instruments TPS54980PWPSWIFT™ |

| 数据手册 | |

| 产品型号 | TPS54980PWP |

| PWM类型 | - |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=16804 |

| 产品目录页面 | |

| 产品种类 | 稳压器—开关式稳压器 |

| 供应商器件封装 | 28-HTSSOP |

| 其它名称 | 296-14415-5 |

| 制造商产品页 | http://www.ti.com/general/docs/suppproductinfo.tsp?distId=10&orderablePartNumber=TPS54980PWP |

| 包装 | 管件 |

| 单位重量 | 118.500 mg |

| 同步整流器 | 是 |

| 商标 | Texas Instruments |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Tube |

| 封装/外壳 | 28-SOIC(0.173",4.40mm 宽)裸露焊盘 |

| 封装/箱体 | HTSSOP-28 |

| 工作温度 | -40°C ~ 85°C |

| 工作温度范围 | - 40 C to + 85 C |

| 工厂包装数量 | 50 |

| 开关频率 | 700 kHz |

| 拓扑结构 | Buck |

| 最大工作温度 | + 85 C |

| 最大输入电压 | 4 V |

| 最小工作温度 | - 40 C |

| 最小输入电压 | 3 V |

| 标准包装 | 50 |

| 电压-输入 | 3 V ~ 4 V |

| 电压-输出 | 0.9 V ~ 2.5 V |

| 电流-输出 | 9A |

| 类型 | 降压(降压) |

| 系列 | TPS54980 |

| 输出数 | 1 |

| 输出电压 | 900 mV to 2.5 V |

| 输出电流 | 9 A |

| 输出端数量 | 1 Output |

| 输出类型 | 可调式 |

| 配用 | /product-detail/zh/XILINXPWR-082/296-17304-ND/684804/product-detail/zh/TPS54980EVM-022/296-18967-ND/863790 |

| 频率-开关 | 350kHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Typical Size 6,4 mm X 9,7 mm (cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 (cid:9)(cid:10)(cid:11) (cid:1)(cid:12) (cid:5)(cid:10)(cid:11) (cid:13)(cid:14)(cid:2)(cid:15)(cid:1)(cid:16) (cid:6)(cid:10)(cid:17) (cid:12)(cid:15)(cid:1)(cid:2)(cid:15)(cid:1) (cid:1)(cid:18)(cid:17)(cid:19)(cid:20)(cid:13)(cid:14)(cid:21) (cid:3)(cid:22)(cid:14)(cid:19)(cid:23)(cid:18)(cid:12)(cid:14)(cid:12)(cid:15)(cid:3) (cid:24)(cid:15)(cid:19)(cid:20) (cid:2)(cid:25)(cid:26) (cid:3)(cid:25)(cid:13)(cid:1)(cid:19)(cid:23)(cid:27)(cid:18) (cid:25)(cid:13)(cid:1)(cid:23) (cid:13)(cid:14)(cid:1)(cid:27)(cid:21)(cid:18)(cid:17)(cid:1)(cid:27)(cid:28) (cid:29)(cid:27)(cid:1)(cid:30) (cid:31)(cid:3)(cid:25)(cid:13)(cid:29)(cid:1)! (cid:29)(cid:12)(cid:18) (cid:3)(cid:27)"(cid:15)(cid:27)(cid:14)(cid:19)(cid:13)(cid:14)(cid:21) FEATURES DESCRIPTION (cid:1) Power Up/Down Tracking For Sequencing (cid:1) 15-mΩ MOSFET Switches for High Efficiency As a member of the SWIFT family of dc/dc regulators, at 9-A Continuous Output Source or Sink the TPS54980 low-input voltage high-output current Current synchronous buck PWM converter integrates all (cid:1) required active components. Using the TRACKIN pin Wide PWM Frequency: with other regulators, simultaneous power up and down Fixed 350 kHz or Adjustable 280 kHz to are easily implemented. Included on the substrate with 700 kHz (cid:1) the listed features are a true, high performance, voltage Power Good and Enable error amplifier that enables maximum performance and (cid:1) Load Protected by Peak Current Limit and flexibility in choosing the output filter L and C Thermal Shutdown components; an under-voltage-lockout circuit to (cid:1) Integrated Solution Reduces Board Area and prevent start-up until the input voltage reaches 3 V; an Component Count internally or externally set slow-start circuit to limit inrush currents; and a power good output useful for APPLICATIONS processor/logic reset. (cid:1) Low-Voltage, High-Density Distributed Power The TPS54980 is available in a thermally enhanced Systems 28-pin TSSOP (PWP) PowerPAD package, which (cid:1) Point of Load Regulation for High eliminates bulky heatsinks. TI provides evaluation Performance DSPs, FPGAs, ASICs and modules and the SWIFT designer software tool to aid Microprocessors Requiring Sequencing in quickly achieving high-performance power supply (cid:1) Broadband, Networking and Optical designs to meet aggressive equipment development Communications Infrastructure cycles. SIMPLIFIED SCHEMATIC I/O Supply START-UP WAVEFORM RL = 1 Ω Input Core Supply VIN PH VI/O = 3.3 V TPS54980 BOOT v TRACKIN PGND di VBIAS VSENSE 0 mv/ V(core) = 1.8 V 0 AGNDCOMP 5 t − Time − 1 ms/div Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD and SWIFT are trademarks of Texas Instruments. (cid:2)(cid:18)(cid:12)(cid:28)(cid:15)(cid:19)(cid:1)(cid:13)(cid:12)(cid:14) (cid:28)(cid:17)(cid:1)(cid:17) #$%&’()*#&$ #(cid:30) +,’’-$* )(cid:30) &% .,/0#+)*#&$ 1)*-2 (cid:2)’&1,+*(cid:30) Copyright 2003 − 2005, Texas Instruments Incorporated +&$%&’( *& (cid:30).-+#%#+)*#&$(cid:30) .-’ *3- *-’((cid:30) &% (cid:1)-4)(cid:30) (cid:13)$(cid:30)*’,(-$*(cid:30) (cid:30)*)$1)’1 5)’’)$*62 (cid:2)’&1,+*#&$ .’&+-(cid:30)(cid:30)#$7 1&-(cid:30) $&* $-+-(cid:30)(cid:30))’#06 #$+0,1- *-(cid:30)*#$7 &% )00 .)’)(-*-’(cid:30)2

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates. ORDERING INFORMATION TA OUTPUT VOLTAGE PACKAGE PART NUMBER −40°C to 85°C 0.9 V to 2.5 V Plastic HTSSOP (PWP)(1) TPS54980PWP (1)The PWP package is also available taped and reeled. Add an R suffix to the device type (i.e., TPS54980PWPR). See the application section of the data sheet for PowerPAD drawing and layout information. (2)For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com. ABSOLUTE MAXIMUM RATINGS over operating free-air temperature range unless otherwise noted(1) TPS54980 UNIT VIN −0.3 V to 4.5 V ENA −0.3 V to 7 V IInnppuutt vvoollttaaggee rraannggee,, VVII RT −0.3 V to 6 V VV VSENSE, TRACKIN −0.3 V to 4V BOOT −0.3 V to 10 V VBIAS, COMP, PWRGD −0.3 V to 7 V OOuuttppuutt vvoollttaaggee rraannggee,, VVOO VV PH −0.6 V to 6 V PH Internally Limited SSoouurrccee ccuurrrreenntt,, IIOO COMP, VBIAS 6 mA PH 16 A SSiinnkk ccuurrrreenntt,, IISS COMP 6 mmAA ENA, PWRGD 10 Voltage differential AGND to PGND ±0.3 V Operating virtual junction temperature range, TJ −40 to 125 °C Storage temperature, Tstg −65 to 150 °C Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 300 °C (1)Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. RECOMMENDED OPERATING CONDITIONS MIN NOM MAX UNIT Input voltage, VI 3 4 V Operating junction temperature, TJ −40 125 °C DISSIPATION RATINGS(1)(2) THERMAL IMPEDANCE TA =25°C TA = 70°C TA = 85°C PACKAGE JUNCTION-TO-AMBIENT POWER RATING POWER RATING POWER RATING 28 Pin PWP with solder 14.4 °C/W 6.94 W(3) 3.81 W 2.77 W 28 Pin PWP without solder 27.9 °C/W 3.58 W 1.97 W 1.43 W (1)For more information on the PWP package, refer to TI technical brief, literature number SLMA002. (2)Test board conditions: 1. 3” x 3”, 4 layers, thickness: 0.062” 2. 1.5 oz. copper traces located on the top of the PCB 3. 1.5 oz. copper ground plane on the bottom of the PCB 4. 0.5 oz. copper ground planes on the two internal layers 5. 12 thermal vias (see “Recommended Land Pattern” in applications section of this data sheet) (3)Maximum power dissipation may be limited by over current protection. 2

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 ELECTRICAL CHARACTERISTICS over operating free-air temperature range unless otherwise noted PARAMETER TEST CONDITIONS MIN TYP MAX UNIT SUPPLY VOLTAGE, VIN Input voltage range, VIN 3.0 4.0 V fs = 350 kHz, RT open, 9.8 17 PH pin open II((QQ)) QQuuiieesscceenntt ccuurrrreenntt fs = 500 kHz, RT = 100 kΩ, PH pin open 14 23 mmAA Shutdown, ENA = 0 V 1 1.4 UNDER VOLTAGE LOCK OUT Start threshold voltage, UVLO 2.95 3.0 V Stop threshold voltage, UVLO 2.70 2.80 V Hysteresis voltage, UVLO 0.14 0.16 V Rising and falling edge deglitch, UVLO(1) 2.5 µs BIAS VOLTAGE Output voltage, VBIAS I(VBIAS) = 0 2.70 2.80 2.90 V Output current, VBIAS (2) 100 µA CUMULATIVE REFERENCE Vref Accuracy 0.882 0.891 0.900 V REGULATION LLiinnee rreegguullaattiioonn((11))((33)) IL = 4.5 A,fs = 350 kHz, TJ = 85°C 0.04 %%//VV IL = 4.5 A,fs = 550 kHz, TJ = 85°C 0.04 LLooaadd rreegguullaattiioonn((11))((33)) IL = 0 A to 9 A, fs = 350 kHz, TJ = 85°C 0.03 %%//AA IL = 0 A to 9 A, fs = 550 kHz, TJ = 85°C 0.03 OSCILLATOR Internally set—free running frequency RT open 280 350 420 kHz RT = 180 kΩ (1% resistor to AGND) 252 280 308 EExxtteerrnnaallllyy sseett——ffrreeee rruunnnniinngg ffrreeqquueennccyy rraannggee RT = 100 kΩ (1% resistor to AGND) 460 500 540 kkHHzz RT = 68 kΩ (1% resistor to AGND) 663 700 762 Ramp valley(1) 0.75 V Ramp amplitude (peak-to-peak)(1) 1 V Minimum controllable on time(1) 200 ns Maximum duty cycle 90% (1)Specified by design (2)Static resistive loads only (3)Specified by the circuit used in Figure 9 3

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 ELECTRICAL CHARACTERISTICS (continued) over operating free-air temperature range unless otherwise noted PARAMETER TEST CONDITIONS MIN TYP MAX UNIT ERROR AMPLIFIER Error amplifier open loop voltage gain 1 kΩ COMP to AGND(1) 90 110 dB Error amplifier unity gain bandwidth Parallel 10 kΩ, 160 pF COMP to AGND(1) 3 5 MHz Error amplifier common mode input voltage Powered by internal LDO(1) 0 VBIAS V range Input bias current, VSENSE VSENSE = Vref 60 250 nA Output voltage slew rate (symmetric), COMP 1.0 1.4 V/µs PWM COMPARATOR PWM comparator propagation delay time, PWM comparator input to PH pin (excluding 10-mV overdrive(1) 70 85 ns deadtime) ENABLE Enable threshold voltage, ENA 0.82 1.20 1.40 V Enable hysteresis voltage, ENA 0.03 V Falling edge deglitch, ENA(1) 2.5 µs Leakage current, ENA VI = 3.6 V 1 µA POWER GOOD Power good threshold voltage VSENSE falling 90 %Vref Power good hysteresis voltage(1) 3 %Vref Power good falling edge deglitch(1) 35 µs Output saturation voltage, PWRGD I(sink) = 2.5 mA 0.18 0.3 V Leakage current, PWRGD VI = 3.6 V 1 µA CURRENT LIMIT Current limit trip point VI = 3.6 VOutput shorted(1) 11 15 A Current limit leading edge blanking time 100 ns Current limit total response time 200 ns THERMAL SHUTDOWN Thermal shutdown trip point(1) 135 150 165 °C Thermal shutdown hysteresis(1) 10 °C OUTPUT POWER MOSFETS VI = 3.6 V(4) 14 28 rrDDSS((oonn)) PPoowweerr MMOOSSFFEETT sswwiittcchheess VI = 3 V(4) 15 30 mmΩΩ TRACKIN Input offset, TRACKIN VSENSE = TRACKIN = 1.25 V −1.5 1.5 mV Input voltage range, TRACKIN See Note 1 0 Vref V (1)Specified by design (2)Static resistive loads only (3)Specified by the circuit used in Figure 9 (4)Matched MOSFETs low-side rDS(on) production tested, high-side rDS(on) specified by design 4

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 PWP PACKAGE (TOP VIEW) AGND 1 28 RT VSENSE 2 27 ENA COMP 3 26 TRACKIN PWRGD 4 25 VBIAS BOOT 5 24 VIN PH 6 23 VIN PH 7 THERMAL 22 VIN PH 8 PAD 21 VIN PH 9 20 VIN PH 10 19 PGND PH 11 18 PGND PH 12 17 PGND PH 13 16 PGND PH 14 15 PGND TERMINAL FUNCTIONS TERMINAL DDEESSCCRRIIPPTTIIOONN NAME NO. AGND 1 Analog ground. Return for compensation network/output divider, slow-start capacitor, VBIAS capacitor, RT resistor. Connect PowerPAD to AGND. BOOT 5 Bootstrap output. 0.022-µF to 0.1-µF low-ESR capacitor connected from BOOT to PH generates floating drive for the high-side FET driver. COMP 3 Error amplifier output. Connect frequency compensation network from COMP to VSENSE ENA 27 Enable input. Logic high enables oscillator, PWM control and MOSFET driver circuits. Logic low disables operation and places device in low quiescent current state. PGND 15−19 Power ground. High current return for the low-side driver and power MOSFET. Connect PGND with large copper areas to the input and output supply returns, and negative terminals of the input and output capacitors. A single point connection to AGND is recommended. PH 6−14 Phase output. Junction of the internal high-side and low-side power MOSFETs, and output inductor. PWRGD 4 Power good open drain output. High when VSENSE ≥ 90% Vref, otherwise PWRGD is low. RT 28 Frequency setting resistor input. Connect a resistor from RT to AGND to set the switching frequency. TRACKIN 26 External reference input. High impedance input to internal reference/multiplexer and error amplifier circuits. VBIAS 25 Internal bias regulator output. Supplies regulated voltage to internal circuitry. Bypass VBIAS pin to AGND pin with a high quality, low-ESR 0.1-µF to 1.0-µF ceramic capacitor. VIN 20−24 Input supply for the power MOSFET switches and internal bias regulator. Bypass VIN pins to PGND pins close to device package with a high quality, low-ESR 10-µF ceramic capacitor. VSENSE 2 Error amplifier inverting input. Connect to output voltage through compensation network/output divider. 5

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 INTERNAL BLOCK DIAGRAM AGND VBIAS Enable Comparator VBIAS REG ENA Falling SHUTDOWN 1.2 V Edge ILIM VIN Deglitch Thermal Comparator VIN Hysteresis: 0.03 V 2.5 µs Shutdown Leading 150°C Edge VIN UVLO Blanking Comparator Falling 100 ns and VIN BOOT Rising 2.95 V Edge Sense Hysteresis: 0.16 V Deglitch FET 15 mΩ I/O 2.5 µs SS_DIS SHUTDOWN PH LOUT Core TRACKIN Multiplexer + R Q Adaptive Dead-Time CO − and Error S Control Logic Amplifier PWM Reference Comparator 25 ns Adaptive VIN Dead Time 15 mΩ OSC PGND Powergood Comparator PWRGD VSENSE Falling 0.90 Vref Edge TPS54980 Deglitch Hysteresis: 0.03 Vref SHUTDOWN 35 µs VSENSE COMP RT 6

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 TYPICAL CHARACTERISTICS DRAIN-SOURCE DRAIN-SOURCE INTERNALLY SET ON-STATE RESISTANCE ON-STATE RESISTANCE OSCILLATOR FREQUENCY vs vs vs JUNCTION TEMPERATURE JUNCTION TEMPERATURE JUNCTION TEMPERATURE 25 ΩDrain Source On-State Reststance − m 11205005−40VIOIN = =9 3A.00 V 25 85 125 ΩDrain Source On-State Reststance − m 1122050505−40VIOIN = =9 3A.06 V 25 85 125 f − Internally Set Oscillator Frequency − kHz 234567555555000000−40 0 25 85 125 TJ − Junction Temperature − °C TJ − Junction Temperature − °C TJ − Junction Temperature − °C Figure 1 Figure 2 Figure 3 EXTERNALLY SET OSCILLATOR FREQUENCY VOLTAGE REFERENCE DEVICE POWER LOSSES vs vs vs JUNCTION TEMPERATURE JUNCTION TEMPERATURE LOAD CURRENT Hz 800 0.895 8 y − k 7 VTJI == 31.235 V°C ernally Set Oscillator Frequenc 345670000000000 RRTT == 6180 0k k − Voltage Reference − VVref0000....888888997913 Device Power Losses − W 123456 Ext RT = 180 k f − 200−40 0 25 85 125 0.885−40 0 25 85 125 00 2 4 6 8 10 12 14 16 TJ − Junction Temperature − °C TJ − Junction Temperature − °C IL − Load Current − A Figure 4 Figure 5 Figure 6 OUTPUT VOLTAGE REGULATION vs ERROR AMPLIFIER INPUT VOLTAGE OPEN LOOP RESPONSE 0.895 140 0 ation − V 0.893 110200 RCTALL === 211560°0 kC ΩpF,, −−4200 ul −60 g s ut Voltage Re 00..888991 Gain − dB468000 Phase −−−11820000ase − Degree p h Out 20 Gain −140P − O0.887 −160 V 0 −180 0.885 −20 −200 3 3.1 3.2 3.3 3.4 3.5 3.6 1 10 100 1 k 10 k 100 k 1 M 10 M VI − Input Voltage − V f − Frequency − Hz Figure 7 Figure 8 7

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 APPLICATION INFORMATION Figure 9 shows the schematic diagram for a typical board. To provide power up tracking, the enable of the I/O TPS54980 application. The TPS54980 (U1) can provide supply should be used. If the I/O enable is not used to greater than 9 A of output current at a nominal output power up, then devices with similar undervoltage lockout voltage of 1.8 V. For proper thermal performance, the thresholds need to be implemented to ensure power up exposed thermal PowerPAD underneath the integrated tracking. To ensure power down tracking, the enable pin circuit package must be soldered to the printed-circuit should be used. TPS54910 VOUT_I/O I/O Power Supply TPS54980 R1 U1 10 kΩ R2 28 1 10 RkΩ4 71.5 kΩ 2276 RETRNTAACKINVSCAEOGNMNSDPE 32 C1 R5 10R 3kΩ 25 VBIAS PWRGD4 470 pF 10 kΩ R7 C3 24 5 R6 C2 23 VIN BOOT 6 C5 C4 301 Ω 470 pF 9.76 kΩ 1 µF 22 VVIINN PPHH 7 0.047 µF 12 pF R8 21 VIN PH 8 9.76 kΩ 20 VIN PH 9 19 10 PGND PH 18 11 VOUT_CORE VIN PGND PH L1 C6 C7 1176 PGND PH 1132 R2.92 Ω 0.65 µH C8 C9 C10 10 µF 10 µF PGND PH 22 µF 22 µF 22 µF 15 PGND PH 14 C11 PwrPad 3300 pF Analog and Power Grounds are Tied at the Power Pad Under the Package of IC Figure 9. Application Circuit COMPONENT SELECTION at 1.8 V. R3, along with R7, R5, C1, C3, and C4, forms the loop compensation network for the circuit. For this design, The values for the components used in this design a Type 3 topology is used. example were selected for low output ripple voltage and small PCB area. Additional design information is available at www.ti.com. OPERATING FREQUENCY INPUT FILTER In the application circuit, the 350 kHz operation is selected by leaving RT open. Connecting a 180kΩ to 68 kΩ resistor The input voltage is a nominal 3.3 Vdc. The input filter C6 between RT (pin 28) and analog ground can be used to set is a 10-µF ceramic capacitor (Taiyo Yuden). C7 also a the switching frequency to 280kHz to 700 kHz. To 10-µF ceramic capacitor (Taiyo Yuden) provides high calculate the RT resistor, use the equation below: frequency decoupling of the TPS54980 from the input supply and must be located as close as possible to the R(cid:1) 500kHz (cid:2)100[k(cid:1)] SwitchingFrequency (1) device. Ripple current is carried in both C6 and C7, and the return path to PGND must avoid the current circulating in OUTPUT FILTER the output capacitors C8, C9, and C10. The output filter is composed of a 0.65-µH inductor and 3 FEEDBACK CIRCUIT x 22-µF capacitor. The inductor is a low dc resistance (0.017 Ω) type, Pulse Engineering PA0227. The The values for these components have been selected to capacitors used are 22-µF, 6.3 V ceramic types with X5R provide low output ripple voltage. The resistor divider dielectric. The feedback loop is compensated so that the network of R3 and R8 sets the output voltage for the circuit unity gain frequency is approximately 75 kHz. 8

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 PCB LAYOUT input voltage decoupling capacitor, and the PGND pins of the TPS54980. Use a separate wide trace for the analog Figure 10 shows a generalized PCB layout guide for the ground signal path. This analog ground should be used for TPS54980. The PVIN pins should be connected together the voltage set point divider, timing resistor RT, and bias on the printed circuit board (PCB) and bypassed with a low capacitor grounds. Connect this trace directly to AGND ESR ceramic bypass capacitor. Care should be taken to (Pin 1). minimize the loop area formed by the bypass capacitor The PH pins should be tied together and routed to the connections, the VIN pins, and the TPS54980 ground output inductor. Since the PH connection is the switching pins. The minimum recommended bypass capacitance is node, the inductor should be located very close to the PH 10 µF ceramic with a X5R or X7R dielectric and the pins and the area of the PCB conductor minimized to optimum placement is closest to the VIN pins and the prevent excessive capacitive coupling. PGND pins. Connect the boot capacitor between the phase node and The TPS54980 has two internal grounds (analog and the BOOT pin as shown. Keep the boot capacitor close to power). The analog ground ties to all of the noise sensitive the IC and minimize the conductor trace lengths. signals, while the power ground ties to the noisier power signals. Noise injected between the two grounds can Connect the output filter capacitor(s) as shown between degrade the performance of the TPS54980, particularly at the VOUT trace and PGND. It is important to keep the loop higher output currents. Ground noise on an analog ground formed by the PH pins, Lout, Cout, and PGND as small as plane can also cause problems with some of the control practical. and bias signals. For these reasons, separate analog and Place the compensation components from the VOUT trace power ground traces are recommended. There should be to the VSENSE and COMP pins. Do not place these an area of ground on the top layer directly under the IC, components too close to the PH trace. Due to the size of with an exposed area for connection to the PowerPAD. the IC package and the device pinout, the components will Use vias to connect this ground area to any internal ground have to be routed somewhat close, but maintain as much planes. Use additional vias at the ground side of the input separation as possible while still keeping the layout and output filter capacitors as well. The AGND and PGND compact. pins should be tied to the PCB ground by connecting them to the ground area under the device as shown. The only Connect the bias capacitor from the VBIAS pin to analog components that should tie directly to the power ground ground using the isolated analog ground trace. If an RT plane are the input capacitors, the output capacitors, the resistor is used, connect it to this trace as well. 9

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 ANALOG GROUND TRACE AGND RT VSENSE ENA TRACKING VOLTAGE COMPENSATION COMP TRACKIN RESISTOR DIVIDER NETWORK BIAS CAPACITOR NETWORK PWRGD VBIAS BOOT CAPACITOR BOOT VIN EXPOSED PH POWERPAD VIN VOUT AREA PH VIN PH VIN VIN PH PH VIN PH PGND OUTPUT INDUCTOR PH PGND OUTPUT PH PGND FILTER CAPACITOR PH PGND INPUT INPUT PH PGND BYPASS BULK CAPACITOR FILTER TOPSIDE GROUND AREA VIA to Ground Plane Figure 10. TPS54980 PCB Layout 10

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 LAYOUT CONSIDERATIONS FOR THERMAL any area available must be used when 9 A or greater PERFORMANCE operation is desired. Connection from the exposed area of the PowerPAD to the analog ground plane layer must be For operation at full rated load current, the analog ground made using 0.013 inch diameter vias to avoid solder plane must provide an adequate heat dissipating area. A wicking through the vias. Eight vias must be in the 3-inch by 3-inch plane of 1 ounce copper is recommended, PowerPAD area with four additional vias located under the though not mandatory, depending on ambient temperature device package. The size of the vias under the package, and airflow. Most applications have larger areas of internal but not in the exposed thermal pad area, can be increased ground plane available, and the PowerPAD must be to 0.018. Additional vias beyond the twelve recommended connected to the largest area available. Additional areas that enhance thermal performance must be included in on the top or bottom layers also help dissipate heat, and areas not under the device package. Minimum Recommended Thermal Vias: 8 x 0.013 Diameter Inside 8 PL Ø0.0130 Powerpad Area 4 x 0.018 Diameter Under Device as Shown. Additional 0.018 Diameter Vias May Be Used if Top Side Analog Ground 4 PL Ø0.0180 Area Is Extended. Connect Pin 1 to Analog Ground Plane in This Area for Optimum Performance 0.0150 0.06 0.0339 0.0650 0.0500 0.3820 0.3478 0.0500 0.2090 0.0500 0.0256 0.0650 0.0339 Minimum Recommended Exposed Copper Area for Powerpad. 5mil 0.1700 Stencils May Require 10 Percent 0.1340 Larger Area Minimum Recommended Top Side Analog Ground Area 0.0630 0.0400 Figure 11. Recommended Land Pattern for 28-Pin PWP PowerPAD 11

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 PERFORMANCE GRAPHS EFFICIENCY OUTPUT VOLTAGE OUTPUT VOLTAGE vs vs vs OUTPUT CURRENT OUTPUT CURRENT INPUT VOLTAGE 100 1.81 1.81 95 1.808 VI = 3.3 V 1.808 IO = 9 A Efficiency − % 677889505050 VI = 3.3 V − Output Voltage − VVO11111.....77888199000.682468 − Output Voltage − VVO11111.....77888199000.682468 IO = 0 A IO = 4.5 A 60 1.794 1.794 55 1.792 1.792 1.79 1.79 500 2 4 6 8 10 0 2 4 6 8 10 3 3.25 3.5 3.75 4 IO − Output Current − A IO − Output Current − A VI − Input Voltage − V Figure 12 Figure 13 Figure 14 AMBIENT TEMPERATURE vs LOOP RESPONSE LOAD CURRENT(1) OUTPUT AND INPUT RIPPLE 60 180 125 v 50 150 115 fTsJ = = 7 10205 °kCH,z, mV/di 3400 Phase 91020 °e − C 10955 VVIO = = 3 1.3.8 V V, 50 Gain − dB−1210000 Gain −0360030se − Degrees nt Temperatur 678555 10 mV/div a e −20 −60Ph mbi 55 −−4300 VI = 5 V, −−19200 A 45 V/div IO = 0 A, 35 2 −50 fS = 700 kHz −150 −60 −180 250 2 4 6 8 10 12 14 16 t − Time − 1 µs/div 100 1 k 10 k 100 k 1 M f − Frequency − Hz IO − Output Current − A Figure 15 Figure 16 Figure 17 LOAD TRANSIENT RESPONSE START-UP TIMING POWER DOWN TIMING I = 2.25 A to 6.75 A mV/div 1 V/div V(coVreIO) 1 V/div VV(cIOore) 0 2 PWRGD(I/O) PWRGD(I/O) V/div V/div 5 5 PWRGD(CORE) PWRGD(CORE) v 2 V/di V/div V/div 5 5 t − Time −100 µs/div t − Time −1 ms/div t − Time −100 ms/div Figure 18 Figure 19 Figure 20 (1)Safe operating area is applicable to the test board conditions in the Dissipation Ratings 12

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 DETAILED DESCRIPTION VOLTAGE REFERENCE The voltage reference system produces a precise V UNDERVOLTAGE LOCKOUT (UVLO) ref signal by scaling the output of a temperature stable The TPS54980 incorporates an undervoltage lockout bandgap circuit. During manufacture, the bandgap and circuit to keep the device disabled when the input voltage scaling circuits are trimmed to produce 0.891 V at the (VIN) is insufficient. During power up, internal circuits are output of the error amplifier, with the amplifier connected held inactive until VIN exceeds the nominal UVLO as a voltage follower. The trim procedure adds to the high threshold voltage of 2.95 V. Once the UVLO start threshold precision regulation of the TPS54980, since it cancels is reached, device start-up begins. The device operates offset errors in the scale and error amplifier circuits. until VIN falls below the nominal UVLO stop threshold of OSCILLATOR AND PWM RAMP 2.8 V. Hysteresis in the UVLO comparator, and a 2.5-µs rising and falling edge deglitch circuit reduce the likelihood The oscillator frequency is set internally to 350 kHz. If a of shutting the device down due to noise on VIN. different frequency of operation is required for the application, the oscillator frequency can be externally TRACKIN/INTERNAL SLOW-START adjusted from 280 to 700 kHz by connecting a resistor The internal slow-start circuit provides start-up slope between the RT pin and AGND. The switching frequency control of the output voltage. The nominal internal is approximated by the following equation, where R is the slow-start rate is 25 V/ms. When the voltage on TRACKIN resistance from RT to AGND: rises faster than the internal slope or is present when SwitchingFrequency(cid:1)100k(cid:1)(cid:2)500[kHz] (2) device operation is enabled, the output rises at the internal R rate. If the reference voltage on TRACKIN rises more SWITCHING FREQUENCY RT PIN slowly, then the output rises at about the same rate as TRACKIN. 350 kHz, internally set Float Externally set 280 kHz to 700 kHz R = 180 kΩ to 68 kΩ Once the voltage on the TRACKIN pin is greater than the internal reference of 0.891 V, the multiplexer switches the ERROR AMPLIFIER noninverting node to the high precision reference. The high performance, wide bandwidth, voltage error amplifier sets the TPS54980 apart from most dc/dc ENABLE (ENA) converters. The user is given the flexibility to use a wide The enable pin, ENA, provides a digital control enable or range of output L and C filter components to suit the disable (shut down) for the TPS54980. An input voltage of particular application needs. Type 2 or type 3 1.4 V or greater ensures that the TPS54980 is enabled. An compensation can be employed using external input of 0.82 V or less ensures that device operation is compensation components. disabled. These are not standard logic thresholds, even PWM CONTROL though they are compatible with TTL outputs. Signals from the error amplifier output, oscillator, and When ENA is low, the oscillator, slow-start, PWM control current limit circuit are processed by the PWM control and MOSFET drivers are disabled and held in an initial logic. Referring to the internal block diagram, the control state ready for device start-up. On an ENA transition from logic includes the PWM comparator, OR gate, PWM latch, low to high, device start-up begins with the output starting and portions of the adaptive dead-time and control logic from 0 V. block. During steady-state operation below the current limit threshold, the PWM comparator output and oscillator VBIAS REGULATOR (VBIAS) pulse train alternately reset and set the PWM latch. Once the PWM latch is reset, the low-side FET remains on for a The VBIAS regulator provides internal analog and digital minimum duration set by the oscillator pulse width. During blocks with a stable supply voltage over variations in this period, the PWM ramp discharges rapidly to its valley junction temperature and input voltage. A high quality, voltage. When the ramp begins to charge back up, the low-ESR, ceramic bypass capacitor is required on the low-side FET turns off and high-side FET turns on. As the VBIAS pin. X7R or X5R grade dielectrics are PWM ramp voltage exceeds the error amplifier output recommended because their values are more stable over voltage, the PWM comparator resets the latch, thus temperature. The bypass capacitor must be placed close turning off the high-side FET and turning on the low-side to the VBIAS pin and returned to AGND. FET. The low-side FET remains on until the next oscillator External loading on VBIAS is allowed, with the caution that pulse discharges the PWM ramp. internal circuits require a minimum VBIAS of 2.70V, and During transient conditions, the error amplifier output external loads on VBIAS with ac or digital switching noise could be below the PWM ramp valley voltage or above the may degrade performance. The VBIAS pin may be useful PWM peak voltage. If the error amplifier is high, the PWM as a reference voltage for external circuits. latch is never reset, and the high-side FET remains on until 13

(cid:1)(cid:2)(cid:3)(cid:4)(cid:5)(cid:6)(cid:7)(cid:8) www.ti.com SLVS452A − FEBRUARY 2003 − REVISED FEBRUARY 2005 the oscillator pulse signals the control logic to turn the OVERCURRENT PROTECTION high-side FET off and the low-side FET on. The device The cycle-by-cycle current limiting is achieved by sensing operates at its maximum duty cycle until the output voltage the current flowing through the high-side MOSFET and rises to the regulation set-point, setting VSENSE to comparing this signal to a preset overcurrent threshold. approximately the same voltage as VREF. If the error The high side MOSFET is turned off within 200 ns of amplifier output is low, the PWM latch is continually reset reaching the current limit threshold. A 100-ns leading edge and the high-side FET does not turn on. The low-side FET blanking circuit prevents the current limit from false remains on until the VSENSE voltage decreases to a tripping. Current limit detection occurs only when current range that allows the PWM comparator to change states. flows from VIN to PH when sourcing current to the output The TPS54980 is capable of sinking current continuously filter. Load protection during current sink operation is until the output reaches the regulation set-point. provided by thermal shutdown. If the current limit comparator trips for longer than 100 ns, THERMAL SHUTDOWN the PWM latch resets before the PWM ramp exceeds the error amplifier output. The high-side FET turns off and The device uses the thermal shutdown to turn off the power low-side FET turns on to decrease the energy in the output MOSFETs and disable the controller if the junction inductor and consequently the output current. This temperature exceeds 150°C. The device is released from process is repeated each cycle in which the current limit shutdown automatically when the junction temperature comparator is tripped. decreases to 10°C below the thermal shutdown trip point, and starts up under control of the slow-start circuit. DEAD-TIME CONTROL AND MOSFET Thermal shutdown provides protection when an overload DRIVERS condition is sustained for several milliseconds. With a persistent fault condition, the device cycles continuously; Adaptive dead-time control prevents shoot-through starting up by control of the soft-start circuit, heating up due current from flowing in both N-channel power MOSFETs to the fault condition, and then shutting down upon during the switching transitions by actively controlling the reaching the thermal shutdown trip point. This sequence turnon times of the MOSFET drivers. The high-side driver repeats until the fault condition is removed. does not turn on until the voltage at the gate of the low-side FET is below 2 V. While the low-side driver does not turn POWER-GOOD (PWRGD) on until the voltage at the gate of the high-side MOSFET The power good circuit monitors for undervoltage is below 2 V. conditions on VSENSE. If the voltage on VSENSE is 10% The high-side and low-side drivers are designed with below the reference voltage, the open-drain PWRGD 300-mA source and sink capability to quickly drive the output is pulled low. PWRGD is also pulled low if VIN is power MOSFETs gates. The low-side driver is supplied less than the UVLO threshold or ENA is low, or a thermal from VIN, while the high-side drive is supplied from the shutdown occurs. When VIN ≥ UVLO threshold, ENA ≥ BOOT pin. A bootstrap circuit uses an external BOOT enable threshold, and VSENSE > 90% of V , the open ref capacitor and an internal 2.5-Ω bootstrap switch drain output of the PWRGD pin is high. A hysteresis connected between the VIN and BOOT pins. The voltage equal to 3% of V and a 35 µs falling edge deglitch ref integrated bootstrap switch improves drive efficiency and circuit prevent tripping of the power good comparator due reduces external component count. to high frequency noise. 14

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 PACKAGING INFORMATION Orderable Device Status Package Type Package Pins Package Eco Plan Lead/Ball Finish MSL Peak Temp Op Temp (°C) Device Marking Samples (1) Drawing Qty (2) (6) (3) (4/5) TPS54980PWP ACTIVE HTSSOP PWP 28 50 Green (RoHS NIPDAU Level-2-260C-1 YEAR 0 to 70 TPS54980 & no Sb/Br) TPS54980PWPR ACTIVE HTSSOP PWP 28 2000 Green (RoHS NIPDAU Level-2-260C-1 YEAR 0 to 70 TPS54980 & no Sb/Br) TPS54980PWPRG4 ACTIVE HTSSOP PWP 28 2000 Green (RoHS NIPDAU Level-2-260C-1 YEAR 0 to 70 TPS54980 & no Sb/Br) (1) The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs. LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. (2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free". RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption. Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement. (3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device. (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device. (6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width. Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release. Addendum-Page 1

PACKAGE OPTION ADDENDUM www.ti.com 6-Feb-2020 In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis. Addendum-Page 2

PACKAGE MATERIALS INFORMATION www.ti.com 12-Feb-2019 TAPE AND REEL INFORMATION *Alldimensionsarenominal Device Package Package Pins SPQ Reel Reel A0 B0 K0 P1 W Pin1 Type Drawing Diameter Width (mm) (mm) (mm) (mm) (mm) Quadrant (mm) W1(mm) TPS54980PWPR HTSSOP PWP 28 2000 330.0 16.4 6.9 10.2 1.8 12.0 16.0 Q1 PackMaterials-Page1

PACKAGE MATERIALS INFORMATION www.ti.com 12-Feb-2019 *Alldimensionsarenominal Device PackageType PackageDrawing Pins SPQ Length(mm) Width(mm) Height(mm) TPS54980PWPR HTSSOP PWP 28 2000 350.0 350.0 43.0 PackMaterials-Page2

GENERIC PACKAGE VIEW PWP 28 PowerPADTM TSSOP - 1.2 mm max height 4.4 x 9.7, 0.65 mm pitch SMALL OUTLINE PACKAGE Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details. 4224765/A www.ti.com

None

None

None

IMPORTANTNOTICEANDDISCLAIMER TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources. TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated

Datasheet下载

Datasheet下载