ICGOO在线商城 > 开发板,套件,编程器 > 评估板 - 嵌入式 - MCU,DSP > TMDSDOCK28069

- 型号: TMDSDOCK28069

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

TMDSDOCK28069产品简介:

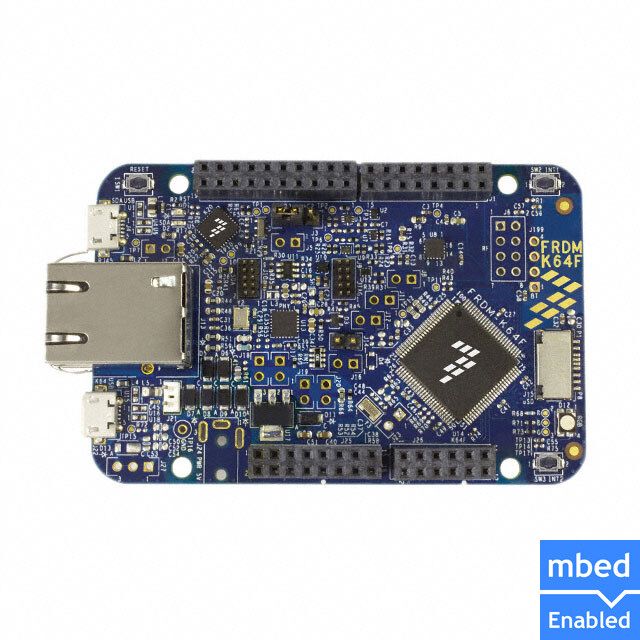

ICGOO电子元器件商城为您提供TMDSDOCK28069由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 TMDSDOCK28069价格参考¥830.72-¥830.72。Texas InstrumentsTMDSDOCK28069封装/规格:评估板 - 嵌入式 - MCU,DSP, TMS320F28069 Experimenter Kit C2000™, Piccolo™ MCU 32-Bit C28x Embedded Evaluation Board。您可以下载TMDSDOCK28069参考资料、Datasheet数据手册功能说明书,资料中有TMDSDOCK28069 详细功能的应用电路图电压和使用方法及教程。

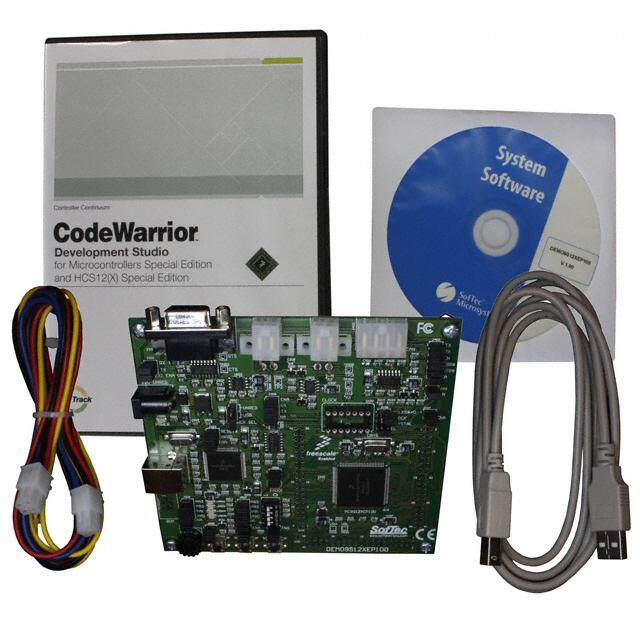

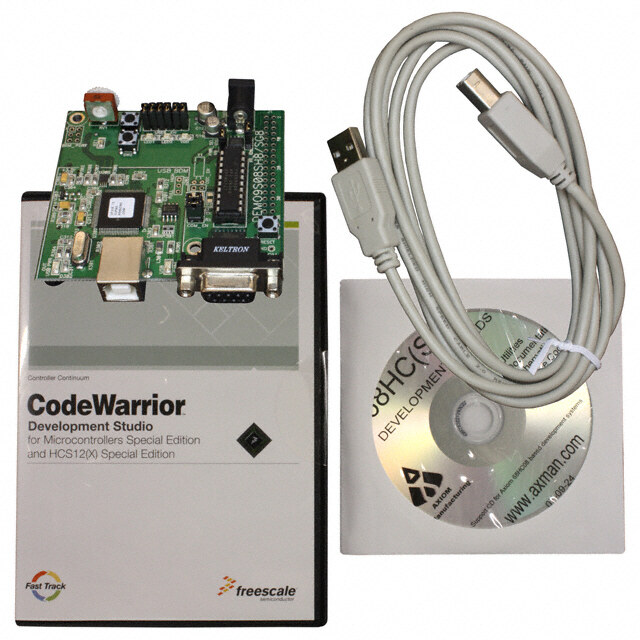

TMDSDOCK28069 是由 Texas Instruments(德州仪器)生产的一款评估板,专为嵌入式系统中的微控制器单元(MCU)和数字信号处理器(DSP)设计。这款评估板主要用于支持 TMS320F28069 系列的 MCU 和 DSP 芯片,广泛应用于电机控制、电源管理、工业自动化等领域。 应用场景: 1. 电机控制: TMDSDOCK28069 适用于各种电机控制应用,如交流感应电机、永磁同步电机(PMSM)、无刷直流电机(BLDC)等。通过集成的高速 ADC 和 PWM 模块,该评估板可以实现高精度的速度和位置控制,适用于家电、工业设备和电动车辆等场合。 2. 电源管理: 在电源管理领域,TMDSDOCK28069 可用于开发高效的电源转换器和逆变器。它支持多种电源拓扑结构,如开关模式电源(SMPS)、不间断电源(UPS)和太阳能逆变器。评估板提供的高性能计算能力和实时处理能力,使得复杂的电源算法得以高效实现。 3. 工业自动化: 该评估板在工业自动化中也有广泛应用,例如可编程逻辑控制器(PLC)、运动控制系统和智能传感器。它能够处理复杂的工业通信协议,如 CAN、EtherCAT 和 Modbus,从而实现设备之间的高效通信和协同工作。 4. 智能家居与物联网: TMDSDOCK28069 还可用于开发智能家居设备和物联网(IoT)节点。它具备强大的数据处理能力和低功耗特性,适合用于智能照明、环境监测和家庭自动化系统。通过连接 Wi-Fi 或 Zigbee 模块,可以轻松实现远程监控和控制功能。 5. 开发与调试工具: 对于开发者而言,TMDSDOCK28069 提供了丰富的开发资源和调试工具。它兼容 Code Composer Studio(CCS)集成开发环境(IDE),支持在线调试和仿真,帮助工程师快速验证和优化代码。此外,TI 还提供了详细的用户手册和技术文档,方便用户进行二次开发和定制化设计。 总之,TMDSDOCK28069 是一款功能强大且灵活多样的评估板,适用于多种嵌入式系统的开发和测试,特别是在电机控制、电源管理和工业自动化等领域具有显著优势。

| 参数 | 数值 |

| 产品目录 | 编程器,开发系统嵌入式解决方案 |

| 描述 | EVAL KIT FOR TMS320F28X开发板和工具包 - TMS320 F28069 Piccolo Experimenter Kit |

| 产品分类 | 评估板 - 嵌入式 - MCU, DSP工程工具 |

| 品牌 | Texas Instruments |

| 产品手册 | |

| 产品图片 |

|

| rohs | 否含铅 / 不受限制有害物质指令(RoHS)规范要求限制 |

| 产品系列 | 嵌入式开发工具,嵌入式处理器开发套件,开发板和工具包 - TMS320,Texas Instruments TMDSDOCK28069C2000™, Piccolo™ |

| 数据手册 | 点击此处下载产品Datasheethttp://www.ti.com/lit/pdf/spruh18点击此处下载产品Datasheet |

| 产品型号 | TMDSDOCK28069 |

| 产品 | Experiment Kits |

| 产品种类 | 开发板和工具包 - TMS320 |

| 其它名称 | 296-36883 |

| 兼容软件 | controlSUITE |

| 内容 | 板,电缆 |

| 商标 | Texas Instruments |

| 安装类型 | 固定 |

| 工作电源电压 | 5 V |

| 工具用于评估 | TMS320F28069 |

| 平台 | 试验套件 |

| 接口类型 | USB |

| 描述/功能 | F28069 Piccolo experimenter kit |

| 操作系统 | - |

| 数据总线宽度 | 32 bit |

| 板类型 | 评估平台 |

| 标准包装 | 1 |

| 核心 | TMS320 |

| 核心处理器 | C28x |

| 用于 | TMDSCNCD28069ISO |

| 类型 | MCU 32-位 |

| 配套使用产品/相关产品 | TMS320F28069 |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

TMS320x2806x Technical Reference Manual LiteratureNumber:SPRUH18H January2011–RevisedNovember2019

Contents Preface....................................................................................................................................... 43 1 SystemControlandInterrupts............................................................................................. 45 1.2 FlashandOTPMemoryBlocks.......................................................................................... 46 1.2.1 FlashMemory...................................................................................................... 46 1.2.2 OTPMemory....................................................................................................... 46 1.2.3 FlashandOTPPowerModes................................................................................... 47 1.2.4 FlashandOTPRegisters........................................................................................ 52 1.3 CodeSecurityModule(CSM)............................................................................................. 58 1.3.1 FunctionalDescription............................................................................................ 58 1.3.2 CSMImpactonOtherOn-ChipResources.................................................................... 60 1.3.3 IncorporatingCodeSecurityinUserApplications ............................................................ 60 1.3.4 Do'sandDon'tstoProtectSecurityLogic...................................................................... 66 1.3.5 CSMFeatures-Summary....................................................................................... 66 1.4 Clocking ..................................................................................................................... 67 1.4.1 ClockingandSystemControl.................................................................................... 67 1.4.2 OSCandPLLBlock............................................................................................... 74 1.4.3 Low-PowerModesBlock......................................................................................... 99 1.4.4 CPUWatchdogBlock........................................................................................... 101 1.4.5 32-BitCPUTimers0/1/2........................................................................................ 107 1.5 General-PurposeInput/Output(GPIO)................................................................................. 112 1.5.1 GPIOModuleOverview......................................................................................... 112 1.5.2 ConfigurationOverview......................................................................................... 118 1.5.3 DigitalGeneralPurposeI/OControl........................................................................... 120 1.5.4 InputQualification................................................................................................ 121 1.5.5 GPIOandPeripheralMultiplexing(MUX) .................................................................... 126 1.5.6 RegisterBitDefinitions.......................................................................................... 130 1.6 PeripheralFrames........................................................................................................ 156 1.6.1 PeripheralFrameRegisters.................................................................................... 156 1.6.2 EALLOW-ProtectedRegisters................................................................................. 158 1.6.3 DeviceEmulationRegisters.................................................................................... 162 1.6.4 Write-Followed-by-ReadProtection........................................................................... 165 1.7 PeripheralInterruptExpansion(PIE)................................................................................... 166 1.7.1 OverviewofthePIEController................................................................................. 166 1.7.2 VectorTableMapping........................................................................................... 169 1.7.3 InterruptSources................................................................................................. 171 1.7.4 PIEConfigurationRegisters.................................................................................... 180 1.7.5 PIEInterruptRegisters.......................................................................................... 181 1.7.6 ExternalInterruptControlRegisters .......................................................................... 189 1.8 VREG/BOR/POR......................................................................................................... 191 1.8.1 On-chipVoltageRegulator(VREG)........................................................................... 191 1.8.2 On-chipPower-OnReset(POR)andBrown-OutReset(BOR)Circuit................................... 192 2 BootROM........................................................................................................................ 193 2.1 BootROMMemoryMap................................................................................................. 194 2.1.1 On-ChipBootROMMathTables.............................................................................. 196 2.1.2 On-ChipBootROMIQmathFunctions........................................................................ 198 2 Contents SPRUH18H–January2011–RevisedNovember2019 SubmitDocumentationFeedback Copyright©2011–2019,TexasInstrumentsIncorporated

www.ti.com 2.1.3 On-ChipFlashAPI............................................................................................... 198 2.1.4 CPUVectorTable............................................................................................... 198 2.2 BootloaderFeatures...................................................................................................... 201 2.2.1 BootloaderFunctionalOperation.............................................................................. 201 2.2.2 BootloaderDeviceConfiguration.............................................................................. 202 2.2.3 PLLMultiplierandDIVSELSelection......................................................................... 202 2.2.4 WatchdogModule ............................................................................................... 203 2.2.5 TakinganITRAPInterrupt...................................................................................... 203 2.2.6 InternalPullupResisters........................................................................................ 203 2.2.7 PIEConfiguration................................................................................................ 203 2.2.8 ReservedMemory............................................................................................... 203 2.2.9 BootloaderModes............................................................................................... 205 2.2.10 Device_Cal ...................................................................................................... 211 2.2.11 BootloaderDataStreamStructure........................................................................... 211 2.2.12 BasicTransferProcedure ..................................................................................... 216 2.2.13 InitBootAssemblyRoutine .................................................................................... 217 2.2.14 SelectBootModeFunction .................................................................................... 218 2.2.15 CopyDataFunction............................................................................................. 221 2.2.16 SCI_BootFunction ............................................................................................. 221 2.2.17 Parallel_BootFunction(GPIO)................................................................................ 223 2.2.18 SPI_BootFunction.............................................................................................. 228 2.2.19 I2CBootFunction .............................................................................................. 231 2.2.20 eCANBootFunction ........................................................................................... 234 2.2.21 ExitBootAssemblyRoutine................................................................................... 236 2.3 BuildingtheBootTable.................................................................................................. 237 2.3.1 TheC2000HexUtility........................................................................................... 237 2.3.2 Example:PreparingaCOFFFileForeCANBootloading.................................................. 238 2.4 BootloaderCodeOverview.............................................................................................. 242 2.4.1 BootROMVersionandChecksumInformation ............................................................. 242 3 EnhancedPulseWidthModulator(ePWM)Module................................................................ 243 3.1 Introduction................................................................................................................ 244 3.1.1 SubmoduleOverview............................................................................................ 244 3.1.2 RegisterMapping................................................................................................ 247 3.2 ePWMSubmodules...................................................................................................... 250 3.2.1 Overview.......................................................................................................... 250 3.2.2 Time-Base(TB)Submodule.................................................................................... 252 3.2.3 Counter-Compare(CC)Submodule........................................................................... 261 3.2.4 Action-Qualifier(AQ)Submodule.............................................................................. 267 3.2.5 Dead-BandGenerator(DB)Submodule...................................................................... 282 3.2.6 PWM-Chopper(PC)Submodule............................................................................... 287 3.2.7 Trip-Zone(TZ)Submodule..................................................................................... 291 3.2.8 Event-Trigger(ET)Submodule................................................................................ 296 3.2.9 DigitalCompare(DC)Submodule............................................................................. 301 3.3 ApplicationstoPowerTopologies...................................................................................... 307 3.3.1 OverviewofMultipleModules ................................................................................. 307 3.3.2 KeyConfigurationCapabilities................................................................................. 307 3.3.3 ControllingMultipleBuckConvertersWithIndependentFrequencies.................................... 308 3.3.4 ControllingMultipleBuckConvertersWithSameFrequencies............................................ 312 3.3.5 ControllingMultipleHalfH-Bridge(HHB)Converters....................................................... 315 3.3.6 ControllingDual3-PhaseInvertersforMotors(ACIandPMSM).......................................... 317 3.3.7 PracticalApplicationsUsingPhaseControlBetweenPWMModules.................................... 321 3.3.8 Controllinga3-PhaseInterleavedDC/DCConverter....................................................... 322 3.3.9 ControllingZeroVoltageSwitchedFullBridge(ZVSFB)Converter....................................... 327 SPRUH18H–January2011–RevisedNovember2019 Contents 3 SubmitDocumentationFeedback Copyright©2011–2019,TexasInstrumentsIncorporated

www.ti.com 3.3.10 ControllingaPeakCurrentModeControlledBuckModule............................................... 329 3.3.11 ControllingH-BridgeLLCResonantConverter............................................................. 331 3.4 Registers................................................................................................................... 334 3.4.1 Time-BaseSubmoduleRegisters.............................................................................. 334 3.4.2 Counter-CompareSubmoduleRegisters..................................................................... 341 3.4.3 Action-QualifierSubmoduleRegisters........................................................................ 345 3.4.4 Dead-BandSubmoduleRegisters............................................................................. 348 3.4.5 PWM-ChopperSubmoduleControlRegister................................................................. 351 3.4.6 Trip-ZoneSubmoduleControlandStatusRegisters........................................................ 353 3.4.7 DigitalCompareSubmoduleRegisters....................................................................... 360 3.4.8 Event-TriggerSubmoduleRegisters.......................................................................... 365 3.4.9 ProperInterruptInitializationProcedure...................................................................... 371 4 High-ResolutionPulseWidthModulator(HRPWM)................................................................ 372 4.1 Introduction................................................................................................................ 373 4.2 OperationalDescriptionofHRPWM.................................................................................... 375 4.2.1 ControllingtheHRPWMCapabilities.......................................................................... 376 4.2.2 ConfiguringtheHRPWM........................................................................................ 378 4.2.3 PrincipleofOperation........................................................................................... 379 4.2.4 ScaleFactorOptimizingSoftware(SFO)..................................................................... 389 4.2.5 HRPWMExamplesUsingOptimizedAssemblyCode...................................................... 389 4.3 HRPWMRegisterDescriptions......................................................................................... 395 4.3.1 RegisterSummary............................................................................................... 395 4.3.2 RegistersandFieldDescriptions.............................................................................. 396 4.4 AppendixA:SFOLibrarySoftware-SFO_TI_Build_V6.lib......................................................... 400 4.5 ScaleFactorOptimizerFunction-intSFO().......................................................................... 400 4.6 SoftwareUsage........................................................................................................... 401 4.7 SFOLibraryVersionSoftwareDifferences............................................................................ 402 5 HighResolutionCapture(HRCAP)...................................................................................... 404 5.1 Introduction................................................................................................................ 405 5.2 Description................................................................................................................. 405 5.3 OperationalDetails....................................................................................................... 406 5.3.1 HRCAPClocking................................................................................................. 406 5.3.2 HRCAPModesofOperation................................................................................... 407 5.3.3 HRCAPInterrupts................................................................................................ 410 5.4 RegisterDescriptions..................................................................................................... 411 5.4.1 HRCAPControlRegister(HCCTL)–EALLOWprotected ................................................. 411 5.4.2 HRCAPInterruptFlagRegister(HCIFR)–EALLOWprotected........................................... 412 5.4.3 HRCAPInterruptClearRegister(HCICLR)–EALLOWprotected........................................ 414 5.4.4 HRCAPInterruptForceRegister(HCIFRC)–EALLOWprotected........................................ 415 5.4.5 HRCAPCounterRegister(HCCOUNTER)................................................................... 415 5.4.6 HRCAPCaptureCounterOnRisingEdge0Register(HCCAPCNTRISE0)............................. 416 5.4.7 HRCAPCaptureCounterOnRisingEdge1Register(HCCAPCNTRISE1)............................. 416 5.4.8 HRCAPCaptureCounterOnFallingEdge0Register(HCCAPCNTFALL0)............................ 416 5.4.9 HRCAPCaptureCounterOnFallingEdge1Register(HCCAPCNTFALL1)............................ 417 5.5 HRCAPCalibrationLibrary ............................................................................................. 417 5.5.1 HRCAPCalibrationLibraryFunctions ........................................................................ 418 5.5.2 HRCAPCalibrationLibrarySoftwareUsage................................................................. 422 6 EnhancedCapture(eCAP)................................................................................................. 425 6.1 Introduction................................................................................................................ 426 6.2 Features.................................................................................................................... 426 6.3 Description................................................................................................................. 426 6.4 CaptureandAPWMOperatingMode.................................................................................. 428 6.5 CaptureModeDescription............................................................................................... 429 4 Contents SPRUH18H–January2011–RevisedNovember2019 SubmitDocumentationFeedback Copyright©2011–2019,TexasInstrumentsIncorporated

www.ti.com 6.5.1 EventPrescaler.................................................................................................. 430 6.5.2 EdgePolaritySelectandQualifier............................................................................. 431 6.5.3 Continuous/One-ShotControl.................................................................................. 431 6.5.4 32-BitCounterandPhaseControl............................................................................. 432 6.5.5 CAP1-CAP4Registers.......................................................................................... 433 6.5.6 eCAPSynchronization.......................................................................................... 433 6.5.7 InterruptControl.................................................................................................. 433 6.5.8 ShadowLoadandLockoutControl............................................................................ 435 6.5.9 APWMModeOperation......................................................................................... 435 6.6 ApplicationoftheeCAPModule ....................................................................................... 437 6.6.1 Example1-AbsoluteTime-StampOperationRisingEdgeTrigger....................................... 437 6.6.2 Example2-AbsoluteTime-StampOperationRisingandFallingEdgeTrigger ........................ 438 6.6.3 Example3-TimeDifference(Delta)OperationRisingEdgeTrigger..................................... 439 6.6.4 Example4-TimeDifference(Delta)OperationRisingandFallingEdgeTrigger ...................... 440 6.7 ApplicationoftheAPWMMode......................................................................................... 441 6.7.1 Example1-SimplePWMGeneration(IndependentChannel/s).......................................... 441 6.8 eCAPRegisters........................................................................................................... 442 6.8.1 eCAPBaseAddresses.......................................................................................... 442 6.8.2 ECAP_REGSRegisters......................................................................................... 443 7 EnhancedQuadratureEncoderPulse(eQEP)....................................................................... 460 7.1 Introduction................................................................................................................ 461 7.2 ConfiguringDevicePins................................................................................................. 463 7.3 Description................................................................................................................. 463 7.3.1 EQEPInputs...................................................................................................... 463 7.3.2 FunctionalDescription........................................................................................... 464 7.3.3 eQEPMemoryMap ............................................................................................. 465 7.4 QuadratureDecoderUnit(QDU)....................................................................................... 466 7.4.1 PositionCounterInputModes.................................................................................. 466 7.4.2 eQEPInputPolaritySelection.................................................................................. 469 7.4.3 Position-CompareSyncOutput................................................................................ 469 7.5 PositionCounterandControlUnit(PCCU)............................................................................ 469 7.5.1 PositionCounterOperatingModes............................................................................ 469 7.5.2 PositionCounterLatch.......................................................................................... 471 7.5.3 PositionCounterInitialization.................................................................................. 473 7.5.4 eQEPPosition-compareUnit................................................................................... 474 7.6 eQEPEdgeCaptureUnit................................................................................................ 475 7.7 eQEPWatchdog.......................................................................................................... 479 7.8 UnitTimerBase........................................................................................................... 479 7.9 eQEPInterruptStructure ................................................................................................ 480 7.10 eQEPRegisters........................................................................................................... 481 7.10.1 eQEPBaseAddresses ........................................................................................ 481 7.10.2 EQEP_REGSRegisters....................................................................................... 482 8 Analog-to-DigitalConverter(ADC)...................................................................................... 516 8.1 ADCOverview............................................................................................................. 517 8.2 Features.................................................................................................................... 517 8.3 BlockDiagram............................................................................................................. 517 8.4 SOCPrincipleofOperation.............................................................................................. 518 8.4.1 ADCAcquisition(SampleandHold)Window................................................................ 520 8.4.2 TriggerOperation................................................................................................ 524 8.4.3 ChannelSelection............................................................................................... 525 8.5 ONESHOTSingleConversionSupport................................................................................ 525 8.6 ADCConversionPriority................................................................................................. 526 8.7 SequentialSamplingMode.............................................................................................. 529 SPRUH18H–January2011–RevisedNovember2019 Contents 5 SubmitDocumentationFeedback Copyright©2011–2019,TexasInstrumentsIncorporated

www.ti.com 8.8 SimultaneousSamplingMode.......................................................................................... 529 8.9 EOCandInterruptOperation............................................................................................ 530 8.10 Power-UpSequence..................................................................................................... 530 8.11 ADCCalibration........................................................................................................... 531 8.11.1 FactorySettingsandCalibrationFunction .................................................................. 531 8.11.2 ADCZeroOffsetCalibration .................................................................................. 531 8.11.3 ADCFullScaleGainCalibration.............................................................................. 532 8.11.4 ADCBiasCurrentCalibration................................................................................. 532 8.12 Internal/ExternalReferenceVoltageSelection........................................................................ 532 8.12.1 InternalReferenceVoltage.................................................................................... 532 8.12.2 ExternalReferenceVoltage................................................................................... 532 8.13 ADCRegisters............................................................................................................ 534 8.13.1 ADCControlRegister1(ADCCTL1) ........................................................................ 534 8.13.2 ADCControlRegister2(ADCCTL2)......................................................................... 536 8.13.3 ADCInterruptRegisters ....................................................................................... 537 8.13.4 ADCPriorityRegister .......................................................................................... 541 8.13.5 ADCSOCRegisters............................................................................................ 543 8.13.6 ADCCalibrationRegisters..................................................................................... 549 8.13.7 ComparatorHysteresisControlRegister.................................................................... 550 8.13.8 ADCRevisionRegister ........................................................................................ 550 8.13.9 ADCResultRegisters.......................................................................................... 550 8.14 ADCTimings.............................................................................................................. 551 8.15 InternalTemperatureSensor............................................................................................ 555 8.15.1 TransferFunction............................................................................................... 555 9 Comparator...................................................................................................................... 557 9.1 Introduction................................................................................................................ 558 9.2 Features.................................................................................................................... 558 9.3 BlockDiagram............................................................................................................. 558 9.4 ComparatorFunction..................................................................................................... 558 9.5 DACReference........................................................................................................... 559 9.6 RampGeneratorInput................................................................................................... 559 9.7 Initialization................................................................................................................ 561 9.8 DigitalDomainManipulation............................................................................................. 561 9.9 ComparatorRegisters.................................................................................................... 562 9.9.1 ComparatorControl(COMPCTL)Register .................................................................. 562 9.9.2 CompareOutputStatus(COMPSTS)Register.............................................................. 563 9.9.3 DACControl(DACCTL)Register ............................................................................. 563 9.9.4 DACValue(DACVAL)Register................................................................................ 564 9.9.5 RampGeneratorMaximumReferenceActive(RAMPMAXREF_ACTIVE)Register ................... 564 9.9.6 RampGeneratorMaximumReferenceShadow(RAMPMAXREF_SHDW)Register................... 565 9.9.7 RampGeneratorDecrementValueActive(RAMPDECVAL_ACTIVE)Register........................ 565 9.9.8 RampGeneratorDecrementValueShadow(RAMPDECVAL_SHDW)Register....................... 565 9.9.9 RampGeneratorStatus(RAMPSTS)Register.............................................................. 565 10 ControlLawAccelerator(CLA)........................................................................................... 567 10.1 Introduction................................................................................................................ 568 10.2 Features.................................................................................................................... 568 10.3 CLAInterface.............................................................................................................. 570 10.3.1 CLAMemory.................................................................................................... 570 10.3.2 CLAMemoryBus............................................................................................... 570 10.3.3 SharedPeripheralsandEALLOWProtection............................................................... 571 10.3.4 CLATasksandInterruptVectors............................................................................. 572 10.4 CLAandCPUArbitration................................................................................................ 573 10.4.1 CLAandCPUArbitration...................................................................................... 573 6 Contents SPRUH18H–January2011–RevisedNovember2019 SubmitDocumentationFeedback Copyright©2011–2019,TexasInstrumentsIncorporated

www.ti.com 10.5 CLAConfigurationandDebug.......................................................................................... 578 10.5.1 BuildingaCLAApplication.................................................................................... 578 10.5.2 TypicalCLAInitializationSequence.......................................................................... 578 10.5.3 DebuggingCLACode.......................................................................................... 579 10.5.4 CLAIllegalOpcodeBehavior................................................................................. 580 10.5.5 ResettingtheCLA.............................................................................................. 580 10.6 Pipeline..................................................................................................................... 582 10.6.1 PipelineOverview............................................................................................... 582 10.6.2 CLAPipelineAlignment........................................................................................ 582 10.6.3 ParallelInstructions............................................................................................. 586 10.7 InstructionSet............................................................................................................. 587 10.7.1 InstructionDescriptions........................................................................................ 587 10.7.2 AddressingModesandEncoding............................................................................ 589 10.7.3 Instructions...................................................................................................... 591 10.8 RegisterSet............................................................................................................... 702 10.8.1 RegisterMemoryMapping .................................................................................... 702 10.8.2 TaskInterruptVectorRegisters............................................................................... 703 10.8.3 ConfigurationRegisters........................................................................................ 704 10.8.4 ExecutionRegisters............................................................................................ 716 11 DirectMemoryAccess(DMA)Module ................................................................................ 719 11.1 Introduction ............................................................................................................... 720 11.2 DMAOverview............................................................................................................ 720 11.3 Architecture................................................................................................................ 720 11.3.1 BlockDiagram................................................................................................... 720 11.3.2 PeripheralInterruptEventTriggerSources................................................................. 721 11.3.3 DMABus......................................................................................................... 723 11.4 PipelineTimingandThroughput........................................................................................ 724 11.5 CPUArbitration ........................................................................................................... 725 11.6 ChannelPriority........................................................................................................... 725 11.6.1 Round-RobinMode............................................................................................. 725 11.6.2 Channel1HighPriorityMode................................................................................. 726 11.7 AddressPointerandTransferControl................................................................................. 726 11.8 OverrunDetectionFeature.............................................................................................. 731 11.9 RegisterDescriptions..................................................................................................... 733 11.9.1 DMAControlRegister(DMACTRL)—EALLOWProtected.............................................. 734 11.9.2 DebugControlRegister(DEBUGCTRL)—EALLOWProtected......................................... 736 11.9.3 RevisionRegister(REVISION) ............................................................................... 736 11.9.4 PriorityControlRegister1(PRIORITYCTRL1)—EALLOWProtected................................. 737 11.9.5 PriorityStatusRegister(PRIORITYSTAT).................................................................. 738 11.9.6 ModeRegister(MODE)—EALLOWProtected............................................................ 739 11.9.7 ControlRegister(CONTROL)—EALLOWProtected..................................................... 741 11.9.8 BurstSizeRegister(BURST_SIZE)—EALLOWProtected.............................................. 743 11.9.9 BURST_COUNTRegister..................................................................................... 743 11.9.10 SourceBurstStepRegisterSize(SRC_BURST_STEP)—EALLOWProtected.................... 744 11.9.11 DestinationBurstStepRegisterSize(DST_BURST_STEP)—EALLOWProtected................ 745 11.9.12 TransferSizeRegister(TRANSFER_SIZE)—EALLOWProtected................................... 745 11.9.13 TransferCountRegister(TRANSFER_COUNT) ......................................................... 746 11.9.14 SourceTransferStepSizeRegister(SRC_TRANSFER_STEP)—EALLOWProtected........... 746 11.9.15 DestinationTransferStepSizeRegister(DST_TRANSFER_STEP)—EALLOWProtected....... 747 11.9.16 Source/DestinationWrapSizeRegister(SRC/DST_WRAP_SIZE)—EALLOWprotected)........ 747 11.9.17 Source/DestinationWrapCountRegister(SCR/DST_WRAP_COUNT) .............................. 748 11.9.18 Source/DestinationWrapStepSizeRegisters(SRC/DST_WRAP_STEP)—EALLOWProtected 748 11.9.19 ShadowSourceBeginandCurrentAddressPointerRegisters SPRUH18H–January2011–RevisedNovember2019 Contents 7 SubmitDocumentationFeedback Copyright©2011–2019,TexasInstrumentsIncorporated

www.ti.com (SRC_BEG_ADDR_SHADOW/DST_BEG_ADDR_SHADOW)—AllEALLOWProtected............ 749 11.9.20 ActiveSourceBeginandCurrentAddressPointerRegisters (SRC_BEG_ADDR/DST_BEG_ADDR)....................................................................... 749 11.9.21 ShadowDestinationBeginandCurrentAddressPointerRegisters (SRC_ADDR_SHADOW/DST_ADDR_SHADOW)—AllEALLOWProtected.......................... 750 11.9.22 ActiveDestinationBeginandCurrentAddressPointerRegisters(SRC_ADDR/DST_ADDR)..... 750 12 SerialPeripheralInterface(SPI).......................................................................................... 751 12.1 Introduction................................................................................................................ 752 12.1.1 Features.......................................................................................................... 752 12.1.2 BlockDiagram.................................................................................................. 752 12.2 System-LevelIntegration................................................................................................ 753 12.2.1 SPIModuleSignals............................................................................................. 753 12.2.2 ConfiguringDevicePins....................................................................................... 754 12.2.3 SPIInterrupts.................................................................................................... 754 12.3 SPIOperation............................................................................................................. 756 12.3.1 IntroductiontoOperation...................................................................................... 756 12.3.2 MasterMode.................................................................................................... 757 12.3.3 SlaveMode...................................................................................................... 758 12.3.4 DataFormat..................................................................................................... 758 12.3.5 BaudRateSelection ........................................................................................... 759 12.3.6 SPIClockingSchemes......................................................................................... 760 12.3.7 SPIFIFODescription........................................................................................... 761 12.3.8 SPI3-WireModeDescription................................................................................. 762 12.4 ProgrammingProcedure................................................................................................. 764 12.4.1 InitializationUponReset....................................................................................... 764 12.4.2 ConfiguringtheSPI............................................................................................. 764 12.4.3 DataTransferExample........................................................................................ 764 12.4.4 SPI3-WireModeCodeExamples............................................................................ 766 12.4.5 SPISTEINVBitinDigitalAudioTransfers.................................................................. 767 12.5 SPIRegisters.............................................................................................................. 769 12.5.1 SPIBaseAddresses........................................................................................... 769 12.5.2 SPI_REGSRegisters .......................................................................................... 770 13 SerialCommunicationsInterface(SCI)................................................................................ 789 13.1 Introduction................................................................................................................ 790 13.2 Architecture................................................................................................................ 792 13.3 SCIModuleSignalSummary ........................................................................................... 792 13.4 ConfiguringDevicePins................................................................................................. 792 13.5 MultiprocessorandAsynchronousCommunicationModes......................................................... 792 13.6 SCIProgrammableDataFormat ....................................................................................... 793 13.7 SCIMultiprocessorCommunication.................................................................................... 793 13.7.1 RecognizingtheAddressByte................................................................................ 794 13.7.2 ControllingtheSCITXandRXFeatures.................................................................... 794 13.7.3 ReceiptSequence.............................................................................................. 794 13.8 Idle-LineMultiprocessorMode.......................................................................................... 794 13.8.1 Idle-LineModeSteps........................................................................................... 795 13.8.2 BlockStartSignal............................................................................................... 796 13.8.3 Wake-UPTemporary(WUT)Flag............................................................................ 796 13.8.4 ReceiverOperation............................................................................................. 796 13.9 Address-BitMultiprocessorMode ...................................................................................... 796 13.9.1 SendinganAddress............................................................................................ 796 13.10 SCICommunicationFormat............................................................................................. 797 13.10.1 ReceiverSignalsinCommunicationModes............................................................... 798 13.10.2 TransmitterSignalsinCommunicationModes............................................................ 798 8 Contents SPRUH18H–January2011–RevisedNovember2019 SubmitDocumentationFeedback Copyright©2011–2019,TexasInstrumentsIncorporated

www.ti.com 13.11 SCIPortInterrupts ....................................................................................................... 799 13.12 SCIBaudRateCalculations............................................................................................ 800 13.13 SCIEnhancedFeatures................................................................................................. 800 13.13.1 SCIFIFODescription......................................................................................... 800 13.13.2 SCIAuto-Baud................................................................................................. 802 13.13.3 Autobaud-DetectSequence ................................................................................. 802 13.14 SCIRegisters............................................................................................................. 803 13.14.1 SCIBaseAddresses.......................................................................................... 803 13.14.2 SCI_REGSRegisters......................................................................................... 804 14 Inter-IntegratedCircuitModule(I2C) ................................................................................... 824 14.1 Introduction................................................................................................................ 825 14.1.1 Features.......................................................................................................... 825 14.1.2 FeaturesNotSupported....................................................................................... 826 14.1.3 FunctionalOverview............................................................................................ 826 14.1.4 ClockGeneration............................................................................................... 827 14.1.5 I2CClockDividerRegisters(I2CCLKLandI2CCLKH).................................................... 828 14.2 ConfiguringDevicePins................................................................................................. 828 14.3 I2CModuleOperationalDetails......................................................................................... 829 14.3.1 InputandOutputVoltageLevels............................................................................. 829 14.3.2 DataValidity..................................................................................................... 829 14.3.3 OperatingModes ............................................................................................... 829 14.3.4 I2CModuleSTARTandSTOPConditions.................................................................. 830 14.3.5 SerialDataFormats............................................................................................ 831 14.3.6 NACKBitGeneration........................................................................................... 833 14.3.7 ClockSynchronization ......................................................................................... 834 14.3.8 Arbitration........................................................................................................ 834 14.3.9 DigitalLoopbackMode......................................................................................... 835 14.4 InterruptRequestsGeneratedbytheI2CModule.................................................................... 836 14.4.1 BasicI2CInterruptRequests.................................................................................. 836 14.4.2 I2CFIFOInterrupts............................................................................................. 838 14.5 ResettingorDisablingtheI2CModule................................................................................. 839 14.6 I2CRegisters.............................................................................................................. 840 14.6.1 I2CBaseAddresses ........................................................................................... 840 14.6.2 I2C_REGSRegisters........................................................................................... 841 15 MultichannelBufferedSerialPort(McBSP).......................................................................... 865 15.1 Overview................................................................................................................... 866 15.1.1 FeaturesoftheMcBSP........................................................................................ 866 15.1.2 McBSPPins/Signals............................................................................................ 867 15.1.3 McBSPOperation............................................................................................... 868 15.1.4 DataTransferProcessofMcBSP............................................................................ 869 15.1.5 Companding(CompressingandExpanding)Data......................................................... 869 15.2 ClockingandFramingData ............................................................................................. 871 15.2.1 Clocking.......................................................................................................... 871 15.2.2 SerialWords..................................................................................................... 871 15.2.3 FramesandFrameSynchronization......................................................................... 872 15.2.4 GeneratingTransmitandReceiveInterrupts ............................................................... 872 15.2.5 IgnoringFrame-SynchronizationPulses..................................................................... 872 15.2.6 FrameFrequency............................................................................................... 873 15.2.7 MaximumFrameFrequency.................................................................................. 873 15.3 FramePhases............................................................................................................. 873 15.3.1 NumberofPhases,Words,andBitsPerFrame........................................................... 874 15.3.2 Single-PhaseFrameExample................................................................................ 874 15.3.3 Dual-PhaseFrameExample.................................................................................. 874 SPRUH18H–January2011–RevisedNovember2019 Contents 9 SubmitDocumentationFeedback Copyright©2011–2019,TexasInstrumentsIncorporated

www.ti.com 15.3.4 ImplementingtheAC97StandardWithaDual-PhaseFrame............................................ 875 15.3.5 McBSPReception.............................................................................................. 875 15.3.6 McBSPTransmission.......................................................................................... 877 15.3.7 InterruptsandDMAEventsGeneratedbyaMcBSP...................................................... 878 15.4 McBSPSampleRateGenerator........................................................................................ 878 15.4.1 BlockDiagram................................................................................................... 879 15.4.2 FrameSynchronizationGenerationintheSampleRateGenerator..................................... 882 15.4.3 SynchronizingSampleRateGeneratorOutputstoanExternalClock .................................. 882 15.4.4 ResetandInitializationProcedurefortheSampleRateGenerator...................................... 884 15.5 McBSPException/ErrorConditions.................................................................................... 885 15.5.1 TypesofErrors.................................................................................................. 885 15.5.2 OverrunintheReceiver........................................................................................ 885 15.5.3 UnexpectedReceiveFrame-SynchronizationPulse....................................................... 887 15.5.4 OverwriteintheTransmitter................................................................................... 889 15.5.5 UnexpectedTransmitFrame-SynchronizationPulse...................................................... 891 15.6 MultichannelSelectionModes.......................................................................................... 893 15.6.1 Channels,Blocks,andPartitions............................................................................. 893 15.6.2 MultichannelSelection......................................................................................... 894 15.6.3 ConfiguringaFrameforMultichannelSelection............................................................ 894 15.6.4 UsingTwoPartitions........................................................................................... 894 15.6.5 UsingEightPartitions.......................................................................................... 896 15.6.6 ReceiveMultichannelSelectionMode....................................................................... 897 15.6.7 TransmitMultichannelSelectionModes..................................................................... 897 15.7 SPIOperationUsingtheClockStopMode............................................................................ 900 15.7.1 SPIProtocol..................................................................................................... 900 15.7.2 ClockStopMode................................................................................................ 901 15.7.3 BitsUsedtoEnableandConfiguretheClockStopMode ................................................ 901 15.7.4 ClockStopModeTimingDiagrams.......................................................................... 902 15.7.5 ProcedureforConfiguringaMcBSPforSPIOperation................................................... 904 15.7.6 McBSPastheSPIMaster..................................................................................... 904 15.7.7 McBSPasanSPISlave....................................................................................... 906 15.8 ReceiverConfiguration................................................................................................... 907 15.8.1 ProgrammingtheMcBSPRegistersfortheDesiredReceiverOperation............................... 907 15.8.2 ResettingandEnablingtheReceiver........................................................................ 908 15.8.3 SettheReceiverPinstoOperateasMcBSPPins......................................................... 908 15.8.4 Enable/DisabletheDigitalLoopbackMode................................................................. 909 15.8.5 Enable/DisabletheClockStopMode........................................................................ 909 15.8.6 Enable/DisabletheReceiveMultichannelSelectionMode................................................ 910 15.8.7 ChooseOneorTwoPhasesfortheReceiveFrame...................................................... 910 15.8.8 SettheReceiveWordLength(s).............................................................................. 911 15.8.9 SettheReceiveFrameLength............................................................................... 911 15.8.10 Enable/DisabletheReceiveFrame-SynchronizationIgnoreFunction................................. 912 15.8.11 SettheReceiveCompandingMode........................................................................ 913 15.8.12 SettheReceiveDataDelay................................................................................. 914 15.8.13 SettheReceiveSign-ExtensionandJustificationMode................................................. 916 15.8.14 SettheReceiveInterruptMode............................................................................. 917 15.8.15 SettheReceiveFrame-SynchronizationMode........................................................... 917 15.8.16 SettheReceiveFrame-SynchronizationPolarity......................................................... 919 15.8.17 SettheReceiveClockMode ................................................................................ 921 15.8.18 SettheReceiveClockPolarity.............................................................................. 922 15.8.19 SettheSRGClockDivide-DownValue.................................................................... 924 15.8.20 SettheSRGClockSynchronizationMode................................................................ 924 15.8.21 SettheSRGClockMode(ChooseanInputClock)...................................................... 924 10 Contents SPRUH18H–January2011–RevisedNovember2019 SubmitDocumentationFeedback Copyright©2011–2019,TexasInstrumentsIncorporated

www.ti.com 15.8.22 SettheSRGInputClockPolarity........................................................................... 926 15.9 TransmitterConfiguration................................................................................................ 926 15.9.1 ProgrammingtheMcBSPRegistersfortheDesiredTransmitterOperation............................ 926 15.9.2 ResettingandEnablingtheTransmitter..................................................................... 927 15.9.3 SettheTransmitterPinstoOperateasMcBSPPins...................................................... 928 15.9.4 Enable/DisabletheDigitalLoopbackMode................................................................. 928 15.9.5 Enable/DisabletheClockStopMode........................................................................ 928 15.9.6 Enable/DisableTransmitMultichannelSelection........................................................... 929 15.9.7 ChooseOneorTwoPhasesfortheTransmitFrame...................................................... 931 15.9.8 SettheTransmitWordLength(s)............................................................................. 931 15.9.9 SettheTransmitFrameLength............................................................................... 932 15.9.10 Enable/DisabletheTransmitFrame-SynchronizationIgnoreFunction................................ 933 15.9.11 SettheTransmitCompandingMode....................................................................... 934 15.9.12 SettheTransmitDataDelay................................................................................. 935 15.9.13 SettheTransmitDXENAMode............................................................................. 937 15.9.14 SettheTransmitInterruptMode............................................................................ 937 15.9.15 SettheTransmitFrame-SynchronizationMode........................................................... 938 15.9.16 SettheTransmitFrame-SynchronizationPolarity........................................................ 939 15.9.17 SettheSRGFrame-SynchronizationPeriodandPulseWidth.......................................... 940 15.9.18 SettheTransmitClockMode................................................................................ 941 15.9.19 SettheTransmitClockPolarity ............................................................................. 941 15.10 EmulationandResetConsiderations.................................................................................. 943 15.10.1 McBSPEmulationMode..................................................................................... 943 15.10.2 ResettingandInitializingMcBSP............................................................................ 943 15.11 DataPackingExamples................................................................................................. 945 15.11.1 DataPackingUsingFrameLengthandWordLength.................................................... 945 15.11.2 DataPackingUsingWordLengthandtheFrame-SynchronizationIgnoreFunction................ 947 15.12 McBSPRegisters......................................................................................................... 947 15.12.1 RegisterSummary............................................................................................ 947 15.12.2 DataReceiveRegisters(DRR[1,2])......................................................................... 948 15.12.3 DataTransmitRegisters(DXR[1,2])........................................................................ 949 15.12.4 SerialPortControlRegisters(SPCR[1,2])................................................................. 950 15.12.5 ReceiveControlRegisters(RCR[1,2]) .................................................................... 955 15.12.6 TransmitControlRegisters(XCR1andXCR2)........................................................... 957 15.12.7 SampleRateGeneratorRegisters(SRGR1andSRGR2)............................................... 960 15.12.8 MultichannelControlRegisters(MCR[1,2])................................................................ 962 15.12.9 PinControlRegister(PCR).................................................................................. 967 15.12.10 ReceiveChannelEnableRegisters(RCERA,RCERB,RCERC,RCERD,RCERE,RCERF, RCERG,RCERH) ............................................................................................... 969 15.12.11 TransmitChannelEnableRegisters(XCERA,XCERB,XCERC,XCERD,XCERE,XCERF, XCERG,XCERH)................................................................................................ 971 15.12.12 InterruptGeneration......................................................................................... 973 16 ControllerAreaNetwork(CAN)........................................................................................... 977 16.1 CANOverview............................................................................................................. 978 16.1.1 Features.......................................................................................................... 978 16.1.2 BlockDiagram................................................................................................... 978 16.2 eCANCompatibilityWithOtherTICANModules.................................................................... 979 16.3 TheCANNetworkandModule ......................................................................................... 979 16.3.1 CANProtocolOverview........................................................................................ 980 16.4 eCANControllerOverview............................................................................................... 981 16.4.1 StandardCANController(SCC)Mode...................................................................... 982 16.4.2 MemoryMap.................................................................................................... 983 16.5 MessageObjects......................................................................................................... 985 16.6 MessageMailbox......................................................................................................... 985 SPRUH18H–January2011–RevisedNovember2019 Contents 11 SubmitDocumentationFeedback Copyright©2011–2019,TexasInstrumentsIncorporated

www.ti.com 16.6.1 TransmitMailbox................................................................................................ 987 16.6.2 ReceiveMailbox................................................................................................ 988 16.6.3 CANModuleOperationinNormalConfiguration........................................................... 988 16.7 eCANConfiguration...................................................................................................... 989 16.7.1 CANModuleInitialization...................................................................................... 989 16.7.2 StepstoConfigureeCAN...................................................................................... 992 16.7.3 HandlingofRemoteFrameMailboxes....................................................................... 994 16.7.4 Interrupts......................................................................................................... 995 16.7.5 CANPower-DownMode..................................................................................... 1000 16.8 eCANRegisters......................................................................................................... 1001 16.8.1 MailboxEnableRegister(CANME)......................................................................... 1001 16.8.2 Mailbox-DirectionRegister(CANMD)....................................................................... 1002 16.8.3 Transmission-RequestSetRegister(CANTRS).......................................................... 1003 16.8.4 Transmission-Request-ResetRegister(CANTRR)....................................................... 1004 16.8.5 Transmission-AcknowledgeRegister(CANTA)........................................................... 1005 16.8.6 Abort-AcknowledgeRegister(CANAA)..................................................................... 1006 16.8.7 Received-Message-PendingRegister(CANRMP)........................................................ 1007 16.8.8 Received-Message-LostRegister(CANRML)............................................................. 1008 16.8.9 Remote-Frame-PendingRegister(CANRFP)............................................................. 1009 16.8.10 GlobalAcceptanceMaskRegister(CANGAM).......................................................... 1011 16.8.11 MasterControlRegister(CANMC)........................................................................ 1012 16.8.12 Bit-TimingConfigurationRegister(CANBTC)............................................................ 1015 16.8.13 ErrorandStatusRegister(CANES)....................................................................... 1017 16.8.14 CANErrorCounterRegisters(CANTEC/CANREC).................................................... 1019 16.8.15 InterruptRegisters........................................................................................... 1020 16.8.16 OverwriteProtectionControlRegister(CANOPC)...................................................... 1027 16.8.17 eCANI/OControlRegisters(CANTIOC,CANRIOC)................................................... 1028 16.8.18 TimerManagementUnit.................................................................................... 1030 16.8.19 MailboxLayout............................................................................................... 1036 16.9 MessageDataRegisters(CANMDL,CANMDH).................................................................... 1039 16.10 AcceptanceFilter........................................................................................................ 1040 16.10.1 Local-AcceptanceMasks(CANLAM)..................................................................... 1040 17 UniversalSerialBus(USB)Controller................................................................................ 1042 17.1 Introduction............................................................................................................... 1043 17.2 Features.................................................................................................................. 1043 17.2.1 BlockDiagram................................................................................................. 1043 17.2.2 SignalDescription............................................................................................. 1044 17.2.3 SignalPinoutTables ......................................................................................... 1044 17.2.4 VBusRecommendations..................................................................................... 1044 17.3 FunctionalDescription.................................................................................................. 1045 17.3.1 OperationasaDevice........................................................................................ 1045 17.3.2 OperationasaHost........................................................................................... 1049 17.3.3 DMAOperation................................................................................................ 1052 17.3.4 Address/DataBusBridge.................................................................................... 1053 17.4 InitializationandConfiguration......................................................................................... 1054 17.4.1 PinConfiguration.............................................................................................. 1054 17.4.2 EndpointConfiguration....................................................................................... 1055 17.5 USBRegisters........................................................................................................... 1056 17.5.1 RegisterMap................................................................................................... 1056 17.5.2 RegisterDescriptions......................................................................................... 1061 RevisionHistory...................................................................................................................... 1125 12 Contents SPRUH18H–January2011–RevisedNovember2019 SubmitDocumentationFeedback Copyright©2011–2019,TexasInstrumentsIncorporated

www.ti.com List of Figures 1-1. FlashPowerModeStateDiagram....................................................................................... 48 1-2. FlashPipeline............................................................................................................... 50 1-3. FlashConfigurationAccessFlowDiagram............................................................................. 51 1-4. FlashOptionsRegister(FOPT).......................................................................................... 53 1-5. FlashPowerRegister(FPWR)........................................................................................... 53 1-6. FlashStatusRegister(FSTATUS)....................................................................................... 54 1-7. FlashStandbyWaitRegister(FSTDBYWAIT) ......................................................................... 55 1-8. FlashStandbytoActiveWaitCounterRegister(FACTIVEWAIT) .................................................. 55 1-9. FlashWait-StateRegister(FBANKWAIT) .............................................................................. 56 1-10. OTPWait-StateRegister(FOTPWAIT) ................................................................................. 57 1-11. CSMStatusandControlRegister(CSMSCR)......................................................................... 62 1-12. PasswordMatchFlow(PMF) ............................................................................................ 63 1-13. ClockandResetDomains ................................................................................................ 68 1-14. PeripheralClockControl0Register(PCLKCR0)...................................................................... 69 1-15. PeripheralClockControl1Register(PCLKCR1)...................................................................... 71 1-16. PeripheralClockControl2Register(PCLKCR2) ..................................................................... 72 1-17. PeripheralClockControl3Register(PCLKCR3)...................................................................... 73 1-18. Low-SpeedPeripheralClockPrescalerRegister(LOSPCP)......................................................... 74 1-19. ClockingOptions........................................................................................................... 75 1-20. InternalOscillatorTrim(INTOSCnTRIM)Register .................................................................... 76 1-21. Clocking(XCLK)Register................................................................................................. 77 1-22. ClockControl(CLKCTL)Register ....................................................................................... 77 1-23. OSCandPLLBlock........................................................................................................ 80 1-24. PLLCRChangeProcedureFlowChart.................................................................................. 82 1-25. PLLCRRegisterLayout................................................................................................... 83 1-26. PLLStatusRegister(PLLSTS)........................................................................................... 83 1-27. PLLLockPeriod(PLLLOCKPRD)Register............................................................................. 85 1-28. PLL2InputandOutputConfigurations.................................................................................. 86 1-29. PLL2Configuration(PLL2CTL)Register(EALLOWprotected)...................................................... 86 1-30. PLL2Multiplier(PLL2MULT)Register(EALLOWprotected)......................................................... 86 1-31. PLL2LockStatus(PLL2STS)Register ................................................................................. 87 1-32. SYSCLK2ClockCounter(SYSCLK2CNTR)Register................................................................. 87 1-33. EPWMDMA/CLAConfiguration(EPWMCFG)Register.............................................................. 88 1-34. ClockingandResetLogic................................................................................................. 89 1-35. ClockFailInterrupt......................................................................................................... 93 1-36. NMIConfiguration(NMICFG)Register.................................................................................. 94 1-37. NMIFlag(NMIFLG)RegisterRegister ................................................................................. 94 1-38. NMIFlag(NMIFLGCLR)RegisterRegister ............................................................................ 95 1-39. NMIFlag(NMIFLGFRC)RegisterRegister ............................................................................ 96 1-40. NMIWatchdogCounter(NMIWDCNT)Register....................................................................... 96 1-41. NMIWatchdogPeriod(NMIWDPRD)Register......................................................................... 96 1-42. XCLKOUTGeneration..................................................................................................... 98 1-43. Low-PowerModeControl0Register(LPMCR0)..................................................................... 100 1-44. CPUWatchdogModule.................................................................................................. 101 1-45. SystemControlandStatusRegister(SCSR) ........................................................................ 104 1-46. WatchdogCounterRegister(WDCNTR).............................................................................. 105 1-47. WatchdogResetKeyRegister(WDKEY) ............................................................................. 105 SPRUH18H–January2011–RevisedNovember2019 ListofFigures 13 SubmitDocumentationFeedback Copyright©2011–2019,TexasInstrumentsIncorporated