ICGOO在线商城 > 射频/IF 和 RFID > RF 收发器 IC > CYRF6936-40LTXC

- 型号: CYRF6936-40LTXC

- 制造商: Cypress Semiconductor

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

CYRF6936-40LTXC产品简介:

ICGOO电子元器件商城为您提供CYRF6936-40LTXC由Cypress Semiconductor设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 CYRF6936-40LTXC价格参考¥7.27-¥9.09。Cypress SemiconductorCYRF6936-40LTXC封装/规格:RF 收发器 IC, IC RF TxRx + MCU General ISM > 1GHZ 2.4GHz 40-VFQFN Exposed Pad。您可以下载CYRF6936-40LTXC参考资料、Datasheet数据手册功能说明书,资料中有CYRF6936-40LTXC 详细功能的应用电路图电压和使用方法及教程。

CYRF6936-40LTXC是Cypress Semiconductor Corp推出的一款高性能、低功耗的2.4GHz RF收发器IC,广泛应用于需要可靠无线通信的短距离无线系统中。其主要应用场景包括无线鼠标、键盘等计算机外设,智能家居设备(如无线照明控制、温控器、传感器网络),工业无线控制系统(如远程监控、数据采集),以及消费类电子产品中的无线音频传输和遥控装置。该芯片支持多种调制方式(如GFSK、FSK、OOK),具备高抗干扰能力,适合在复杂电磁环境中稳定工作。同时,CYRF6936-40LTXC集成度高、外围电路简洁,有助于降低整体设计成本和产品体积,适用于对功耗和空间敏感的便携式设备。其工作电压范围宽(1.8V至3.6V),可兼容多种电源方案,进一步提升了应用灵活性。总体而言,CYRF6936-40LTXC是一款适用于中低数据速率无线通信系统的理想选择,特别适合强调稳定性、低功耗与成本效益的应用场景。

| 参数 | 数值 |

| 产品目录 | |

| 描述 | IC WIRELESS USB LP 2.4GHZ 40QFN射频收发器 Wireless USB |

| 产品分类 | RF 收发器集成电路 - IC |

| 品牌 | Cypress Semiconductor Corp |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | RF集成电路,射频收发器,Cypress Semiconductor CYRF6936-40LTXCWirelessUSB™ |

| 数据手册 | http://www.cypress.com/?docID=48819 |

| 产品型号 | CYRF6936-40LTXC |

| 产品目录页面 | |

| 产品种类 | 射频收发器 |

| 其它名称 | 428-2962 |

| 功率-输出 | 4dBm |

| 包装 | 托盘 |

| 商标 | Cypress Semiconductor |

| 商标名 | WirelessUSB |

| 天线连接器 | PCB,表面贴装 |

| 存储容量 | - |

| 安装风格 | SMD/SMT |

| 封装 | Tray |

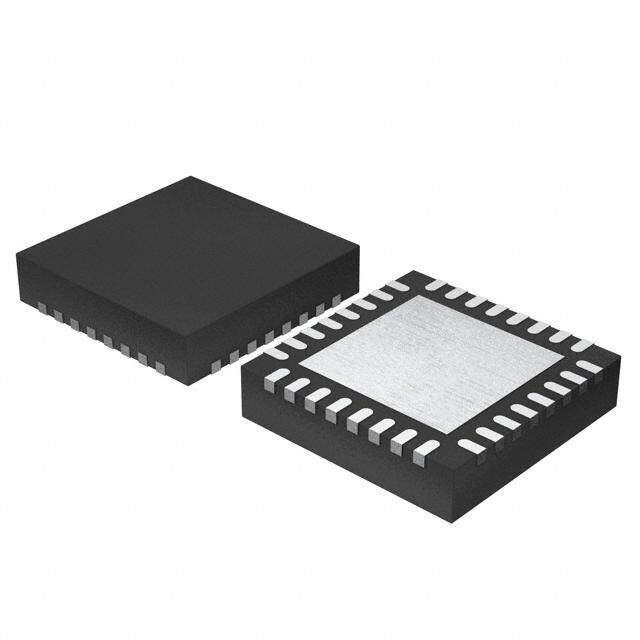

| 封装/外壳 | 40-VFQFN 裸露焊盘 |

| 封装/箱体 | QFN-40 |

| 工作温度 | 0°C ~ 70°C |

| 工作电源电压 | 1.8 V to 3.6 V |

| 工厂包装数量 | 490 |

| 应用 | ISM |

| 数据接口 | PCB,表面贴装 |

| 数据速率(最大值) | 1Mbps |

| 最大工作温度 | + 125 C |

| 最小工作温度 | - 55 C |

| 标准包装 | 490 |

| 灵敏度 | -97dBm |

| 特色产品 | http://www.digikey.com/cn/zh/ph/Cypress/USBmicrocontrollers.html |

| 电压-电源 | 1.8 V ~ 3.6 V |

| 电流-传输 | 34mA |

| 电流-接收 | 21.2mA |

| 系列 | CYRF6936 |

| 调制或协议 | DSSS,GFSK |

| 频率 | 2.4GHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

CYRF6936 WirelessUSB™ LP 2.4 GHz Radio SoC WirelessUSB™ LP 2.4 GHz Radio SoC Features ■Battery Voltage Monitoring Circuitry ■Supports coin-cell operated applications ■2.4 GHz Direct Sequence Spread Spectrum (DSSS) radio transceiver ■Operating voltage from 1.8 V to 3.6 V ■Operates in the unlicensed worldwide Industrial, Scientific, and ■Operating temperature from 0 °C to 70 °C Medical (ISM) band (2.400 GHz to 2.483 GHz) s ■Space saving 40-pin QFN 6 × 6 mm package n ■21 mA operating current (Transmit at –5 dBm) Applications g ■Transmit power up to +4 dBm i ■Receive sensitivity up to –97 dBm ■Wireless Keyboards and Mice s e ■Sleep Current less than 1 A ■Wireless Gamepads d ■DSSS data rates up to 250 kbps, GFSK data rate of 1 Mbps ■Remote Controls w ■Low external component count ■Toys e ■Auto Transaction Sequencer (ATS) - no MCU intervention ■VOIP and Wireless Headsets n ■Framing, Length, CRC16, and Auto ACK ■White Goods ■Power Management Unit (PMU) for MCU/Sensor ■Consumer Electronics r o ■Fast Startup and Fast Channel Changes ■Home Automation f ■Separate 16-byte Transmit and Receive FIFOs ■Automatic Meter Readers d ■AutoRate™ - dynamic data rate reception ■Personal Health and Entertainment e d ■Receive Signal Strength Indication (RSSI) Applications Support n ■Serial Peripheral Interface (SPI) control while in sleep mode See www.cypress.com for development tools, reference e ■4 MHz SPI microcontroller interface designs, and application notes. m m Logic Block Diagram o c V L/D V V V PACTL BAT REG DD CC e r Power Management GFSK RF P t Modulator RFN o Data DSSS RFBIAS N IRQ Interface Baseband SS and & Framer SCK Sequencer SPI MISO GFSK MOSI Demodulator RSSI Xtal Osc Synthesizer RST XTAL XOUT GND CypressSemiconductorCorporation • 198 Champion Court • SanJose, CA 95134-1709 • 408-943-2600 Document Number: 38-16015 Rev. *L Revised May 19, 2017

CYRF6936 Contents Functional Description .....................................................3 Absolute Maximum Ratings ..........................................16 Pinouts ..............................................................................3 Operating Conditions .....................................................16 Pin Definitions ..................................................................3 DC Characteristics .........................................................16 Functional Overview ........................................................4 AC Characteristics .........................................................18 Data Transmission Modes ...........................................4 SPI Interface ..............................................................18 Link Layer Modes ........................................................4 RF Characteristics ..........................................................19 Packet Buffers .............................................................5 Radio Parameters .....................................................19 Auto Transaction Sequencer (ATS) ............................6 Typical Operating Characteristics ................................21 Data Rates ..................................................................6 AC Test Loads and Waveforms for Digital Pins ..........23 s Functional Block Overview ..............................................6 Ordering Information ......................................................24 n 2.4 GHz Radio .............................................................6 Ordering Code Definitions .........................................24 g Frequency Synthesizer ................................................6 Package Diagrams ..........................................................25 i Baseband and Framer .................................................6 Acronyms ........................................................................27 s Packet Buffers and Radio Configuration Registers .....6 Document Conventions .................................................27 e SPI Interface ................................................................6 Units of Measure .......................................................27 d Interrupts .....................................................................8 Document History Page .................................................28 Clocks ..........................................................................8 Sales, Solutions, and Legal Information ......................30 w Power Management ....................................................8 Worldwide Sales and Design Support .......................30 Low Noise Amplifier and Products ....................................................................30 e Received Signal Strength Indication ...................................9 PSoC® Solutions ......................................................30 n Receive Spurious Response .......................................9 Cypress Developer Community .................................30 Application Examples ....................................................10 Technical Support .....................................................30 r o Registers .........................................................................15 f d e d n e m m o c e r t o N Document Number: 38-16015 Rev. *L Page 2 of 30

CYRF6936 Functional Description The CYRF6936 WirelessUSB™ LP radio is a second generation member of the Cypress WirelessUSB Radio System-On-Chip (SoC) family. The CYRF6936 is interoperable with the first generation CYWUSB69xx devices. The CYRF6936 IC adds a range of enhanced features, including increased operating voltage range, reduced supply current in all operating modes, higher data rate options, reduced crystal start up, synthesizer settling, and link turnaround times. Pinouts Figure 1. 40-pin QFN pinout s Ctoarbnser REGV NC BAT0V L/D NC DDV RST I/OV NC NC n 4 3 3 3 3 3 3 3 3 3 g 0 9 8 7 6 5 4 3 2 1 i XTAL 1 30 PACTL / GPIO s NC 2 29 XOUT / GPIO e VCC 3 28 MISO / GPIO d NC 4 CYRF6936 27 MOSI / SDAT w NC 5 WirelessUSB LP 26 IRQ / GPIO 40-Pin QFN VBAT1 6 25 SCK e VCC 7 24 SS n VBAT2 8 23 NC r NC 9 22 NC * E-PAD Bottom Side o RFBIAS 10 21 NC f 11 12 13 14 15 16 17 18 19 20 d R G R N N V N N R N PF ND NF C C CC C C ES C e V d n e Pin Definitions m Pin Number Name Type Default Description m 1 XTAL I I 12 MHz crystal. o 2, 4, 5, 9, 14, NC NC Connect to GND. 15, 17, 18, 20, c 21, 22, 23, 31, e 32, 36, 39 r 3, 7, 16 VCC Pwr VCC = 2.4 V to 3.6 V. Typically connected to VREG. t o 6, 8, 38 V Pwr V = 1.8 V to 3.6 V. Main supply. BAT(0-2) BAT N 10 RF O O RF I/O 1.8 V reference voltage. BIAS 11 RF I/O I Differential RF signal to and from antenna. P 12 GND GND Ground. 13 RF I/O I Differential RF signal to and from antenna. N 19 RESV I Must be connected to GND. 24 SS I I SPI enable, active LOW assertion. Enables and frames transfers. 25 SCK I I SPI clock. 26 IRQ I/O O Interrupt output (configurable active HIGH or LOW), or GPIO. 27 MOSI I/O I SPI data input pin (Master Out Slave In), or SDAT. 28 MISO I/O Z SPI data output pin (Master In Slave Out), or GPIO (in SPI 3-pin mode). Tri-states when SPI 3PIN = 0 and SS is deasserted. Document Number: 38-16015 Rev. *L Page 3 of 30

CYRF6936 Pin Definitions (continued) Pin Number Name Type Default Description 29 XOUT I/O O Buffered 0.75, 1.5, 3, 6, or 12 MHz clock, PACTL, or GPIO. Tri-states in sleep mode (configure as GPIO drive LOW). 30 PACTL I/O O Control signal for external PA, T/R switch, or GPIO. 33 V Pwr I/O interface voltage, 1.8–3.6 V. I/O 34 RST I I Device reset. Internal 10 kohm pull down resistor. Active HIGH, connect through a 0.47 F capacitor to V Must have RST=1 event the first time BAT. power is applied to the radio. Otherwise the state of the radio control registers s is unknown. n 35 VDD Pwr Decoupling pin for 1.8 V logic regulator, connect through a 0.47 F capacitor g to GND. i s 37 L/D O PMU inductor/diode connection, when used. If not used, connect to GND. e 40 V Pwr PMU boosted output voltage feedback. REG d E-PAD GND GND Must be soldered to Ground. w Corner Tabs NC NC Do Not solder the tabs and keep other signal traces clear. All tabs are common to the lead frame or paddle which is grounded after the pad is grounded. While e they are visible to the user, they do not extend to the bottom. n Functional Overview Data Transmission Modes r The SoC supports four different data transmission modes: o The CYRF6936 IC provides a complete WirelessUSB SPI to f antenna wireless MODEMs. The SoC is designed to implement ■In GFSK mode, data is transmitted at 1 Mbps, without any wireless device links operating in the worldwide 2.4GHz ISM DSSS. d frequency band. It is intended for systems compliant with e ■In 8DR mode, eight bits are encoded in each derived code worldwide regulations covered by ETSI EN 301 489-1 V1.41, symbol transmitted. d ETSI EN 300 328-1 V1.3.1 (Europe), FCC CFR 47 Part 15 (USA and Industry Canada), and TELEC ARIB_T66_March, 2003 ■In DDR mode, two bits are encoded in each derived code n (Japan). symbol transmitted (As in the CYWUSB6934 DDR mode). e The SoC contains a 2.4 GHz, 1 Mbps GFSK radio transceiver, ■In SDR mode, one bit is encoded in each derived code symbol m packet data buffering, packet framer, DSSS baseband controller, transmitted (As in the CYWUSB6934 standard modes). Received Signal Strength Indication (RSSI), and SPI interface m for data transfer and device configuration. Both 64 chip and 32 chip Pseudo Noise (PN) codes are supported. The four data transmission modes apply to the data The radio supports 98 discrete 1 MHz channels (regulations may o after the SOP. In particular the length, data, and CRC16 are all limit the use of some of these channels in certain jurisdictions). sent in the same mode. In general, lower data rates reduce c The baseband performs DSSS spreading/despreading, Start of packet error rate in any given environment. e Packet (SOP), End of Packet (EOP) detection, and CRC16 r generation and checking. The baseband may also be configured Link Layer Modes to automatically transmit Acknowledge (ACK) handshake t The CYRF6936 IC device supports the following data packet o packets whenever a valid packet is received. framing features: N When in receive mode, with packet framing enabled, the device is always ready to receive data transmitted at any of the SOP supported bit rates. This enables the implementation of Packets begin with a two-symbol SoP marker. This is required in mixed-rate systems in which different devices use different data GFSK and 8DR modes, but is optional in DDR mode and is not rates. This also enables the implementation of dynamic data rate supported in SDR mode. If framing is disabled then an SOP systems that use high data rates at shorter distances or in a event is inferred whenever two successive correlations are low-moderate interference environment or both. It changes to detected. The SOP_CODE_ADR code used for the SOP is lower data rates at longer distances or in high interference different from that used for the “body” of the packet, and if desired environments or both. may be a different length. SOP must be configured to be the In addition, the CYRF6936 IC has a Power Management Unit same length on both sides of the link. (PMU), which enables direct connection of the device to any Length battery voltage in the range 1.8 V to 3.6 V. The PMU conditions the battery voltage to provide the supply voltages required by the There are two options for detecting the end of a packet. If SOP device, and may supply external devices. is enabled, then the length field must be enabled. GFSK and 8DR must enable the length field. This is the first eight bits after Document Number: 38-16015 Rev. *L Page 4 of 30

CYRF6936 the SOP symbol, and is transmitted at the payload data rate. calculated using either the loaded seed value or a zero seed; the When the length field is enabled, an EoP condition is inferred received data CRC16 is checked against both the configured after reception of the number of bytes defined in the length field, and zero CRC16 seeds. plus two bytes for the CRC16. The alternative to using the length CRC16 detects the following errors: field is to infer an EOP condition from a configurable number of successive noncorrelations; this option is not available in GFSK ■Any one bit in error. mode and is only recommended when using SDR mode. ■Any two bits in error (irrespective of how far apart, which CRC16 column, and so on). The device may be configured to append a 16 bit CRC16 to each ■Any odd number of bits in error (irrespective of the location). packet. The CRC16 uses the USB CRC polynomial with the added programmability of the seed. If enabled, the receiver ■An error burst as wide as the checksum itself. s verifies the calculated CRC16 for the payload data against the Figure2 shows an example packet with SOP, CRC16, and n received value in the CRC16 field. The seed value for the CRC16 lengths fields enabled, and Figure3 shows a standard ACK g calculation is configurable, and the CRC16 transmitted may be packet. i s Figure 2. Example Packet Format e Preamble 2nd Framing d n x 16us Symbol* w P SOP 1 SOP 2 Length Payload Data CRC 16 e n 1st Framing Packet length r Symbol* 1 Byte *Note:32 or 64us o Period f d e Figure 3. Example ACK Packet Format d Preamble 2nd Framing n x 16us Symbol* n e P SOP 1 SOP 2 CRC 16 m m CRC field from 1st Framing received packet. *Note:32 or 64us Symbol* o 2 Byte periods c e r Packet Buffers The CYRF6936 IC supports packets up to 255 bytes. However, t the actual maximum packet length depends on the accuracy of o All data transmission and reception use the 16 byte packet the clock on each end of the link and the data mode. Interrupts N buffers - one for transmission and one for reception. are provided to allow an MCU to use the transmit and receive The transmit buffer allows loading a complete packet of up to 16 buffers as FIFOs. When transmitting a packet longer than 16 bytes of payload data in one burst SPI transaction. This is then bytes, the MCU can load 16 bytes initially, and add further bytes transmitted with no further MCU intervention. Similarly, the to the transmit buffer as transmission of data creates space in receive buffer allows receiving an entire packet of payload data the buffer. Similarly, when receiving packets longer than 16 up to 16 bytes with no firmware intervention required until the bytes, the MCU must fetch received data from the FIFO packet reception is complete. periodically during packet reception to prevent it from overflowing. Document Number: 38-16015 Rev. *L Page 5 of 30

CYRF6936 Auto Transaction Sequencer (ATS) The CYRF6936 IC provides automated support for transmission Table 1. Internal PA Output Power Step Table and reception of acknowledged data packets. PA Setting Typical Output Power (dBm) When transmitting in transaction mode, the device automatically: 7 +4 ■starts the crystal and synthesizer 6 0 ■enters transmit mode 5 –5 ■transmits the packet in the transmit buffer 4 –13 ■transitions to receive mode and waits for an ACK packet 3 –18 s 2 –24 ■transitions to the transaction end state when an ACK packet is n received or a timeout period expires 1 –30 g Similarly, when receiving in transaction mode, the device 0 –35 i automatically: s ■waits in receive mode for a valid packet to be received Frequency Synthesizer e ■transitions to transmit mode, transmits an ACK packet Before transmission or reception may begin, the frequency d synthesizer must settle. The settling time varies depending on ■transitions to the transaction end state (receive mode to await channel; 25 fast channels are provided with a maximum settling w the next packet, and so on.) time of 100 s. e The contents of the packet buffers are not affected by the The ‘fast channels’ (less than 100 s settling time) are every third n transmission or reception of ACK packets. channel, starting at 0 up to and including 72 (for example, 0, 3, In each case, the entire packet transaction takes place without 6, 9 …. 69, 72). r any need for MCU firmware action (as long as packets of 16 o Baseband and Framer bytes or less are used). To transmit data, the MCU must load the f data packet to be transmitted, set the length, and set the TX GO The baseband and framer blocks provide the DSSS encoding d bit. Similarly, when receiving packets in transaction mode, and decoding, SOP generation and reception, CRC16 firmware must retrieve the fully received packet in response to generation and checking, and EOP detection and length field. e an interrupt request indicating reception of a packet. d Packet Buffers and Radio Configuration Registers Data Rates n Packet data and configuration registers are accessed through e The CYRF6936 IC supports the following data rates by the SPI interface. All configuration registers are directly combining the PN code lengths and data transmission modes addressed through the address field in the SPI packet (as in the m described in the previous sections: CYWUSB6934). Configuration registers allow configuration of DSSS PN codes, data rate, operating mode, interrupt masks, m ■1000 kbps (GFSK) interrupt status, and so on. ■250 kbps (32 chip 8DR) o SPI Interface c ■125 kbps (64 chip 8DR) The CYRF6936 IC has an SPI interface supporting e ■62.5 kbps (32 chip DDR) communication between an application MCU and one or more r slave devices (including the CYRF6936). The SPI interface ■31.25 kbps (64 chip DDR) supports single-byte and multi-byte serial transfers using either t o ■15.625 kbps (64 chip SDR) 4-pin or 3-pin interfacing. The SPI communications interface consists of Slave Select (SS), Serial Clock (SCK), Master N Functional Block Overview Out-Slave In (MOSI), Master In-Slave Out (MISO), or Serial Data (SDAT). 2.4 GHz Radio SPI communication may be described as the following: The radio transceiver is a dual conversion low IF architecture ■Command Direction (bit 7) = ‘1’ enables SPI write transaction. optimized for power, range, and robustness. The radio employs A ‘0’ enables SPI read transactions. channel-matched filters to achieve high performance in the presence of interference. An integrated Power Amplifier (PA) ■Command Increment (bit 6) = ‘1’ enables SPI auto address provides up to +4 dBm transmit power, with an output power increment. When set, the address field automatically control range of 34 dB in seven steps. The supply current of the increments at the end of each data byte in a burst access. device is reduced as the RF output power is reduced. Otherwise the same address is accessed. ■Six bits of address ■Eight bits of data Document Number: 38-16015 Rev. *L Page 6 of 30

CYRF6936 The device receives SCK from an application MCU on the SCK ensure that the MOSI pin on the MCU is in a high impedance pin. Data from the application MCU is shifted in on the MOSI pin. state except when MOSI is actively transmitting data. Data to the application MCU is shifted out on the MISO pin. The The device registers may be written to or read from one byte at active LOW Slave Select (SS) pin must be asserted to initiate an a time, or several sequential register locations may be written or SPI transfer. read in a single SPI transaction using incrementing burst mode. The application MCU can initiate SPI data transfers using a In addition to single byte configuration registers, the device multi-byte transaction. The first byte is the Command/Address includes register files. Register files are FIFOs written to and byte, and the following bytes are the data bytes shown in Table2 read from using nonincrementing burst SPI transactions. through Figure 6 on page 8. The IRQ pin function may be optionally multiplexed onto the The SPI communications interface has a burst mechanism, MOSI pin. When this option is enabled, the IRQ function is not where the first byte can be followed by as many data bytes as available while the SS pin is LOW. When using this configuration, s required. A burst transaction is terminated by deasserting the user firmware must ensure that the MOSI pin on the MCU is in a n slave select (SS = 1). high impedance state whenever the SS pin is HIGH. g The SPI communications interface single read and burst read The SPI interface is not dependent on the internal 12 MHz clock. i sequences are shown in Figure 4 on page 7 and Figure 5 on Registers may therefore be read from or written to when the s page 7, respectively. device is in sleep mode, and the 12 MHz oscillator disabled. e The SPI communications interface single write and burst write The SPI interface and the IRQ and RST pins have a separate d sequences are shown in Figure 6 on page 8 and Figure 7 on voltage reference pin (V ). This enables the device to interface I/O page 8, respectively. directly to MCUs operating at voltages below the CYRF6936 IC w supply voltage. This interface may be optionally operated in a 3-pin mode with e the MISO and MOSI functions combined in a single bidirectional data pin (SDAT). When using 3-pin mode, user firmware must n r Table 2. SPI Transaction Format o f Parameter Byte 1 Byte 1+N d Bit # 7 6 [5:0] [7:0] e Bit Name DIR INC Address Data d Figure 4. SPI Single Read Sequence n e m SCK m SS cmd addr o MOSI D0IR INC A5 A4 A3 A2 A1 A0 c data to mcu e MISO D7 D6 D5 D4 D3 D2 D1 D0 r t Figure 5. SPI Incrementing Burst Read Sequence o N SCK SS cmd addr MOSI DIR INC A5 A4 A3 A2 A1 A0 0 data to mcu1 data to mcu1+N MISO D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0 Document Number: 38-16015 Rev. *L Page 7 of 30

CYRF6936 Figure 6. SPI Single Write Sequence SCK SS cmd addr data from mcu MOSI DIR INC A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0 1 MISO s n Figure 7. SPI Incrementing Burst Write Sequence g i s SCK e d SS cmd addr data from mcu1 data from mcu1+N w MOSI DIR INC A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0 1 e MISO n r Interrupts ■Frequency Stability: ±30 ppm o The device provides an interrupt (IRQ) output, which is configu- ■Series Resistance: <60 ohms f rable to indicate the occurrence of various different events. The d IRQ pin may be programmed to be either active HIGH or active ■Load Capacitance: 10 pF e LOW, and be either a CMOS or open drain output. The available ■Drive Level: 100 µW interrupts are described in the section Registers on page 15. d The CYRF6936 IC features three sets of interrupts: transmit, Power Management n receive, and system interrupts. These interrupts all share a The operating voltage of the device is 1.8 V to 3.6 V DC, which e single pin (IRQ), but can be independently enabled or disabled. is applied to the VBAT pin. The device can be shut down to a fully m The contents of the enable registers are preserved when static sleep mode by writing to the FRC END = 1 and switching between transmit and receive modes. END STATE = 000 bits in the XACT_CFG_ADR register over the m If more than one interrupt is enabled at any time, it is necessary SPI interface. The device enters sleep mode within 35 µs after to read the relevant status register to determine which event the last SCK positive edge at the end of this SPI transaction. o caused the IRQ pin to assert. Even when a given interrupt source Alternatively, the device may be configured to automatically c is disabled, the status of the condition that would otherwise enter sleep mode after completing the packet transmission or cause an interrupt can be determined by reading the appropriate reception. When in sleep mode, the on-chip oscillator is stopped, e status register. It is therefore possible to use the devices without but the SPI interface remains functional. The device wakes from r the IRQ pin, by polling the status registers to wait for an event, sleep mode automatically when the device is commanded to t rather than using the IRQ pin. enter transmit or receive mode. When resuming from sleep o mode, there is a short delay while the oscillator restarts. The N Clocks device can be configured to assert the IRQ pin when the oscillator has stabilized. A 12 MHz crystal (30 ppm or better) is directly connected between XTAL and GND without the need for external The output voltage (VREG) of the Power Management Unit capacitors. A digital clock out function is provided, with (PMU) is configurable to several minimum values between 2.4 V selectable output frequencies of 0.75, 1.5, 3, 6, or 12 MHz. This and 2.7 V. VREG may be used to provide up to 15 mA (average output may be used to clock an external microcontroller (MCU) load) to external devices. It is possible to disable the PMU and or ASIC. This output is enabled by default, but may be disabled. provide an externally regulated DC supply voltage to the device’s main supply in the range 2.4 V to 3.6 V. The PMU also provides The requirements to directly connect the crystal to the XTAL pin a regulated 1.8 V supply to the logic. and GND are: The PMU is designed to provide high boost efficiency (74–85% ■Nominal Frequency: 12 MHz depending on input voltage, output voltage, and load) when using a Schottky diode and power inductor, eliminating the need ■Operating Mode: Fundamental Mode for an external boost converter in many systems where other ■Resonance Mode: Parallel Resonant components require a boosted voltage. However, reasonable efficiencies (69–82% depending on input voltage, output voltage, Document Number: 38-16015 Rev. *L Page 8 of 30

CYRF6936 and load) may be achieved when using low cost components ranges. Disabling AGC and enabling LNA is recommended, such as SOT23 diodes and 0805 inductors. unless receiving from a device using external PA. The current through the diode must stay within the linear When the device is in receive mode the RSSI_ADR register operating range of the diode. For some loads the SOT23 diode returns the relative signal strength of the on-channel signal is sufficient, but with higher loads it is not and an SS12 diode power. must be used to stay within this linear range of operation. Along When receiving, the device automatically measures and stores with the diode, the inductor used must not saturate its core. In the relative strength of the signal being received as a five bit higher loads, a lower resistance/higher saturation coil such as value. An RSSI reading is taken automatically when the SoP is the inductor from Sumida must be used. detected. In addition, a new RSSI reading is taken every time the The PMU also provides a configurable low battery detection previous reading is read from the RSSI_ADR register, allowing function, which may be read over the SPI interface. One of seven the background RF energy level on any given channel to be s thresholds between 1.8 V and 2.7 V may be selected. The easily measured when RSSI is read while no signal is being n interrupt pin may be configured to assert when the voltage on the received. A new reading can occur as fast as once every 12 µs. g V pin falls below the configured threshold. LV IRQ is not a BAT latched event. Battery monitoring is disabled when the device is Receive Spurious Response i s in sleep mode. The transmitter may exhibit spurs around 50 MHz offset at levels e approximately 50dB to 60dB below the carrier power. Receivers Low Noise Amplifier and Received Signal Strength operating at the transmit spur frequency may receive the spur if d Indication the spur level power is greater than the receive sensitivity level. w The gain of the receiver can be controlled directly by clearing the The workaround for this is to program an additional byte in the AGC EN bit and writing to the Low Noise Amplifier (LNA) bit of packet header which contains the transmitter channel number. e the RX_CFG_ADR register. Clearing the LNA bit reduces the After the packet is received, the channel number can be receiver gain approximately 20 dB, allowing accurate reception checked. If the channel number does not match the receive n of very strong received signals (for example, when operating a channel then the packet is rejected. receiver very close to the transmitter). Approximately 30 dB of r o receiver attenuation can be added by setting the Attenuation (ATT) bit. This limits data reception to devices at very short f d e d n e m m o c e r t o N Document Number: 38-16015 Rev. *L Page 9 of 30

CYRF6936 Application Examples Figure 8. Recommended Circuit for Systems where VBAT 2.4 V ANT1WIGGLE 63 12 C4 1.5 pFd C15 20400.047 uFdC16 20400.047 uFdC11Radio Decoupling Caps20400.047 uFdC9 20400.047 uFdC10 20400.047 uFd C5 20400.47 uFd 60513743 DG312CCCDEIND0603CCCVRVVVVL110RFbiasC122 nH11RFp2IND0402040L215 pFd13RFn1.8 nHC320400402PACTL2.0 pFdTV630PACTL 1XTAL CLKOUTY1TV129XOUT12 MHz Crystal19RESV20NC921NC1022NC1123NC1231NC1332NC1436NC1539NC16DAP-E 14E-PAD must be soldered to ground. designs VBATVCCR2 08051 1%C7080510 uFd 6.3V R3 0402RF VCO47C8and VCO0402Buffer1 uFd 6.3VFilter C1304020.047 uFd VBATU1CYRF6936388633 O210TTTC17IVAAA0.47 uFdBBBVVV0402 RSTTV834RST nSSTV224SSSCKTV325SCKMOSITV427MOSIMISOTV528MISO IRQTV726IRQ 37L/D 2NC14NC25NC39NC414NC515NC617NC718NC81DNG 21 VCCD1SOT23TP121BAT400DC12080510 uFd 6.3V TP2 or new The power supply decoupling shown for VBAT0is a recommended cost effectiveconfiguration:C6=No Load R2= 1ohm C7=10uF ceramic.For this configuration, it is required thatC18 be installed. An alternate decoupling configuration isthe following:C6=47uF ceramic R2=0ohm C7=.047uF.For this configuration, it is not requiredto load C18. For reference design part numbers, pleaserefer to the Bill of Materials file121-26504_A.xls. EVCC C20C19040204020.01 uFd0.01 uFd U2752 12DDBINDDDVVP1_0COL12523P1_0P0_0 / CLKINP1_1COL2S12622P0_1 / CLKOUTP1_1COL3SW128211A1BP0_2 / INT0P1_2COL4nSS29202A2BP1_3 / SSELP0_3 / INT1SCKCOL53019P1_4 / SCLKP0_4 / INT2COL6MOSI1831SW PUSHBUTTONP1_5 / SMOSIP0_5 / TIO0MISOCOL71732P1_6 / SMISOP0_6 / TIO1IRQCOL81633P1_7P0_7 COL9ROW13415P2_0P3_0COL10ROW23514P2_1P3_1COL11ROW33613P2_2P3_2COL12ROW41237P3_3P2_3COL13ROW53811P3_4P2_4COL14ROW61039P3_5P2_5COL15ROW7409P3_6P2_6COL16ROW8418P3_7P2_7 COL1771P4_0NC1J4COL1862P4_1NC2Serial debug423NC3P4_23434headerNC42P4_345NC5146NC647NC73 PIN HDR48NC821SSSSVVCY7C60123-PVXC 4424 VBAT L3 10 uHE+C18C6A 2-pin jumperVCCEVCC1210100 uFd 10vNo Loadinstalled from J3.1R1to J2.1 enables theISSP0603radio to power theNO LOADprocessor. JumperJ3J2removal is required11when programming U221 PIN HDRXRES3P1_0to disconnect theSCLK4P1_1SDATAradio from the55 PIN HDRMiniprog 5V source. Layout J3 and J2.1 in aR1 is a zero ohm0.100" spacingresistor that shouldconfigurationbe installed forproduction unitsonly, followingprogramming. Not recommended f Power Supply BH1VBAT"+"1POS "-"2NEG13NEG2 BATT CON 2xAA Keyboard Interface J1ROW111ROW222ROW333ROW444ROW555ROW666ROW777ROW888COL1899COL171010COL161111COL151212COL141313COL131414COL121515COL111616COL101717COL91818COL81919COL72020COL62121COL52222COL42323COL32424COL22525COL12626KB 26 Pin Document Number: 38-16015 Rev. *L Page 10 of 30

CYRF6936 Table 3. Recommended BoM for Systems where VBAT 2.4 V Item Qty CY Part Number Reference Description Manufacturer Mfr Part Number 1 1 NA ANT1 2.5 GHZ H-STUB WIGGLE NA NA ANTENNA FOR 63 MIL PCB 2 1 NA BH1 BATTERY CLIPS 2AA CELL 3 1 730-10012 C1 CAP 15 PF 50 V CERAMIC NPO Panasonic ECJ-0EC1H150J 0402 4 1 730-11955 C3 CAP 2.0 PF 50 V CERAMIC NPO Kemet C0402C209C5GACTU s 0402 n 5 1 730-11398 C4 CAP 1.5 PF 50 V CERAMIC NPO PANASONIC ECJ-0EC1H1R5C g 0402 SMD i 6 2 730R-13322 C5, C17 CAP CER 0.47 UF 6.3 V X5R 0402 Murata GRM155R60J474KE19D s e 7 2 730-13037 C12, C7 CAP CERAMIC 10 UF 6.3 V X5R Kemet C0805C106K9PACTU 0805 d 8 1 730-13400 C8 CAP 1 uF 6.3 V CERAMIC X5R 0402 Panasonic ECJ-0EB0J105M w 9 6 730-13404 C9, C10, C11, CAP 0.047 uF 16 V CERAMIC X5R AVX 0402YD473KAT2A C13, C15, 0402 e C16 n 10 1 710-13201 C18 CAP 100 UF 10 V ELECT FC Panasonic - ECG EEU-FC1A101S r 11 2 730-10794 C20,C19 CAP 10000 PF 16 V CERAMIC 0402 Panasonic - ECG ECJ-0EB1C103K o SMD f 12 1 800-13317 D1 DIODE SCHOTTKY 0.5 A 40 V DIODES INC BAT400D-7-F d SOT23 e 13 1 NA J1 PCB COPPER PADS NONE d 14 1 420-11496 J2 CONN HDR BRKWAY 5POS STR AMP Division of 103185-5 AU PCB TYCO n e 15 1 420-11964 J3 HEADER 1 POS 0.230 HT MODII AMP/Tyco 103185-1 .100 CL m 16 1 800-13401 L1 INDUCTOR 22 NH 2% FIXED 0603 Panasonic - ECG ELJ-RE22NGF2 m SMD 17 1 800-11651 L2 INDUCTOR 1.8 NH +/-.3 NH FIXED Panasonic - ECG ELJ-RF1N8DF o 0402 SMD c 18 1 800-10594 L3 COIL 10 UH 1100MA CHOKE 0805 Newark 30K5421 e 19 1 630-11356 R2 RES 1.00 OHM 1/8 W 1% 0805 SMD Yageo 9C08052A1R00FKHFT r 20 1 610-13402 R3 RES 47 OHM 1/16 W 5% 0402 SMD Panasonic - ECG ERJ-2GEJ470X t o 21 1 800-13368 S1 LT SWITCH 6 MM 100 GF H = 7 MM Panasonic - ECG EVQ-PAC07K TH N 22 1 CYRF6936-40LF U1 IC, LP 2.4 GHz RADIO SoC QFN-40 Cypress CYRF6936 Rev A5 C Semiconductor 23 1 CY7C60123-PVX U2 IC WIRELESS EnCore II Cypress CY7C60123-PVXC C CONTROLLER SSOP48 Semiconductor 24 1 800-13259 Y1 CRYSTAL 12.00 MHZ HC49 SMD eCERA GF-1200008 25 1 PDC-9265-*B PCB PRINTED CIRCUIT BOARD Cypress PDC-9265-*B Semiconductor 26 1 920-11206 LABEL1 Serial Number 27 1 920-26504 *A LABEL2 PCA # 121-26504 *A Document Number: 38-16015 Rev. *L Page 11 of 30

CYRF6936 Table 3. Recommended BoM for Systems where VBAT 2.4 V (continued) Item Qty CY Part Number Reference Description Manufacturer Mfr Part Number No Load Components - Do Not Install 28 1 730-13403 C6 CAP 47UF 6.3 V CERAMIC X5R Panasonic ECJ-4YB0J476M 1210 29 1 630-10242 R2 RES CHIP 0.0 OHM 1/10W 5% 0805 Phycomp USA Inc 9C08052A0R00JLHFT SMD 30 1 730-13404 C7 CAP 0.047 uF 50 V CERAMIC X5R AVX 0402YD473KAT2A 0402 s 31 1 420-10921 J4 HEADER 3POS FRIC STRGHT MTA AMP/Tyco 644456-3 n 100 g 32 1 620-10519 R1 RES ZERO OHM 1/16W 5% 0603 Panasonic - ECG ERJ-3GEY0R00V SMD i s e d w e n r o f d e d n e m m o c e r t o N Document Number: 38-16015 Rev. *L Page 12 of 30

CYRF6936 Figure 9. Recommended Circuit for Systems where V is 2.4 V–3.6 V (PMU Disabled) BAT ANT1ANT1WIGGLE 32WIGGLE 32 12 C4C404020402 1.5 pFd1.5 pFd C1C12200440015 pFd15 pFd C3C3220044002.0 pFd2.0 pFd Y1Y1 12 MHz Crystal12 MHz Crystal round. C11C11 0.047 uFd0.047 uFd s g o 04020402 n IND0603IND0603 L1L122 nH22 nH IND0402IND0402L2L21.8 nH1.8 nH TV-20RTV-20R oldered t C10C10 040204020.047 uFd0.047 uFd sig C5C5220044000.47 uFd0.47 uFd 0365431373 D312GOCCCDEIVCCCVRVVVV10RFbias 11RFp 13RFn 30PACTL 1XTAL TV1TV129XOUT 19RESV20NC921NC1022NC1123NC1231NC1332NC1436NC1539NC16D1ADPN-GE 1241E-PAD must be s C9C9C7C7C8C8 04020402040204020.047 uFd0.047 uFd0.047 uFd0.047 uFd0.047 uFd0.047 uFd new de VCC 8863 210TTTAAABBBVVV 34RST 24SS25SCK27MOSI28MISO 26IRQ 37L/D 2NC14NC25NC39NC414NC515NC617NC718NC8 VCC C6C6 04020402040204020.047 uFd0.047 uFd for d U1U1CYRF6936CYRF6936 RST nSSSCKMOSIMISO IRQ de VCC C15C150.47 uFd0.47 uFd04020402 pply VCC C14C14 080508052.2 uFd2.2 uFd en Su m r Powe C13C13 4.7 uFd4.7 uFd m VCC nLED2nLED1IRQSW1 RST 5V 08050805 o c C12C12220044001500 pFd1500 pFd 12VREG 7P0_06P0_15P0_2/INT04P0_3/INT13P0_4/INT22P0_5/TIO01P0_6/TIO1 re 5V U2U211 CCV 10DM/P1_19DP/P1_0 nSS13SSEL/P1_3SCK14SCLK/P1_4MOSI15MOSI/P1_5MISO16MISO/P1_6 SSVCY7C63803-SXCCY7C63803-SXC8 CONNECT/ACTIVITY" D1D1 nLED113GRCnLED224RDC LED Green RedLED Green Red "BIND" S1S1SW11A2A1B2B SW RA PUSHSW RA PUSH Not " R2R262062004020402 5V 5V VBUSDMDP R1R1zerozero 22004400 GG 123456 MT PLUMT PLU J1J1 VBUSDMDPGNDS1S2USB A SUSB A S Document Number: 38-16015 Rev. *L Page 13 of 30

CYRF6936 Table 4. Recommended BoM for Systems where V is 2.4 V–3.6 V (PMU disabled) BAT Item Qty CY Part Number Reference Description Manufacturer Mfr Part Number 1 1 NA ANT1 2.5 GHZ H-STUB WIGGLE ANTENNA NA NA FOR 32MIL PCB 2 1 730-10012 C1 CAP 15 PF 50 V CERAMIC NPO 0402 Panasonic ECJ-0EC1H150J 3 1 730-11955 C3 CAP 2.0 PF 50 V CERAMIC NPO 0402 Kemet C0402C209C5GACTU 4 1 730-11398 C4 CAP 1.5 PF 50 V CERAMIC NPO 0402 PANASONIC ECJ-0EC1H1R5C SMD s 5 1 730-13322 C5, C15 CAP 0.47 uF 6.3 V CERAMIC X5R 0402 Murata GRM155R60J474KE19D n 6 g 7 6 730-13404 C6, C7, C8, CAP 0.047 uF 16 V CERAMIC X5R 0402 AVX 0402YD473KAT2A i C9, C10, s C11 e 8 1 730-11953 C12 CAP 1500 PF 50 V CERAMIC X7R 0402 Kemet C0402C152K5RACTU d 9 1 730-13040 C13 CAP CERAMIC 4.7 UF 6.3 V XR5 0805 Kemet C0805C475K9PACTU w 10 1 730-12003 C14 CAP CER 2.2 UF 10 V 10% X7R 0805 Murata GRM21BR71A225KA01L Electronics North e America n 11 1 800-13333 D1 LED GREEN/RED BICOLOR 1210 SMD LITEON LTST-C155KGJRKT r 12 1 420-13046 J1 CONN USB PLUG TYPE A PCB SMT ACON UAR72-4N5J10 o 13 1 800-13401 L1 INDUCTOR 22NH 2% FIXED 0603 SMD Panasonic - ECG ELJ-RE22NGF2 f 14 1 800-11651 L2 INDUCTOR 1.8 NH +/-.3 NH FIXED 0402 Panasonic - ECG ELJ-RF1N8DF d SMD e 15 1 610-10343 R1 RES ZERO OHM 1/16W 0402 SMD Panasonic - ECG ERJ-2GE0R00X d 16 1 610-13472 R2 RES CHIP 620 OHM 1/16W 5% 0402 Panasonic - ECG ERJ-2GEJ621X n SMD e 17 1 200-13471 S1 SWITCH LT 3.5 MM X 2.9 MM 160 GF Panasonic - ECG EVQ-P7J01K SMD m 18 1 CYRF6936-40LFC U1 IC, LP 2.4 GHz RADIO SoC QFN-40 Cypress CYRF6936 Rev A5 m Semiconductor 19 1 CY7C63803-SXC U2 IC LOW SPEED USB ENCORE II Cypress CY7C63803-SXC o CONTROLLER SOIC16 Semiconductor c 20 1 800-13259 Y1 CRYSTAL 12.00 MHZ HC49 SMD eCERA GF-1200008 e 21 1 PDC-9263-*B PCB PRINTED CIRCUIT BOARD Cypress PDC-9263-*B r Semiconductor t 22 1 LABEL1 Serial Number XXXXXX o N 23 1 LABEL2 PCA # 121-26305 ** Document Number: 38-16015 Rev. *L Page 14 of 30

CYRF6936 Registers All registers are read and writable, except where noted. Registers may be written to or read from individually or in sequential groups.[1, 2] Table 5. Register Map Summary Address Mnemonic b7 b6 b5 b4 b3 b2 b1 b0 Default[1] Access[1] 0x00 CHANNEL_ADR Not Used Channel -1001000 -bbbbbbb 0x01 TX_LENGTH_ADR TX Length 00000000 bbbbbbbb TXB15 TXB8 TXB0 TXBERR TXC TXE 00000011 bbbbbbbb 0x02 TX_CTRL_ADR TX GO TX CLR IRQEN IRQEN IRQEN IRQEN IRQEN IRQEN DATA CODE --000101 --bbbbbb 0x03 TX_CFG_ADR Not Used Not Used LENGTH DATA MODE PA SETTING s OS LV TXB15 TXB8 TXB0 TXBERR TXC TXE -------- rrrrrrrr 0x04 TX_IRQ_STATUS_ADR IRQ IRQ IRQ IRQ IRQ IRQ IRQ IRQ n RXB16 RXB8 RXB1 RXBERR RXC RXE 00000111 bbbbbbbb 0x05 RX_CTRL_ADR RX GO RSVD IRQEN IRQEN IRQEN IRQEN IRQEN IRQEN g 0x06 FAST 10010-10 bbbbb-bb RX_CFG_ADR AGC EN LNA ATT HILO TURN EN Not Used RXOW EN VLD EN i s RXOW SOPDET RXB16 RXB8 RXB1 RXBERR RXC RXE -------- brrrrrrr 0x07 RX_IRQ_STATUS_ADR IRQ IRQ IRQ IRQ IRQ IRQ IRQ IRQ e 0x08 RX_STATUS_ADR RX ACK PKT ERR EOP ERR CRC0 Bad CRC RX Code RX Data Mode -------- rrrrrrrr d 0x09 RX_COUNT_ADR RX Count 00000000 rrrrrrrr 0x0A RX_LENGTH_ADR RX Length 00000000 rrrrrrrr 0x0B[1] PWR_CTRL_ADR PMU EN LVIRQ EN PMFUo rMceode diPsaFbEleT[ 3] LVI TH PMU OUTV 10100000 bbbbbbbb w 0x0C XTAL_CTRL_ADR XOUT FN XSIRQ EN Not Used Not Used FREQ 000--100 bbb--bbb e 0x0D IO_CFG_ADR IRQ OD IRQ POL MISO OD XOUT OD PACTL OD PACTL SPI 3PIN IRQ GPIO 00000000 bbbbbbbb GPIO n 0x0E GPIO_CTRL_ADR XOUT OP MISO OP PACTL OP IRQ OP XOUT IP MISO IP PACTL IP IRQ IP 0000---- bbbbrrrr 0x0F XACT_CFG_ADR ACK EN Not Used FRC END END STATE ACK TO 1-000000 b-bbbbbb r 0x10 FRAMING_CFG_ADR SOP EN SOP LEN LEN EN SOP TH 10100101 bbbbbbbb o 0x11 DATA32_THOLD_ADR Not Used Not Used Not Used Not Used TH32 ----0100 ----bbbb f 0x12 DATA64_THOLD_ADR Not Used Not Used Not Used TH64 ---01010 ---bbbbb 0x13 RSSI_ADR SOP Not Used LNA RSSI 0-100000 r-rrrrrr d 0x14 EOP_CTRL_ADR[4] HEN HINT EOP 10100100 bbbbbbbb e 0x15 CRC_SEED_LSB_ADR CRC SEED LSB 00000000 bbbbbbbb d 0x16 CRC_SEED_MSB_ADR CRC SEED MSB 00000000 bbbbbbbb 0x17 TX_CRC_LSB_ADR CRC LSB -------- rrrrrrrr n 0x18 TX_CRC_MSB_ADR CRC MSB -------- rrrrrrrr e 0x19 RX_CRC_LSB_ADR CRC LSB 11111111 rrrrrrrr 0x1A RX_CRC_MSB_ADR CRC MSB 11111111 rrrrrrrr m 0x1B TX_OFFSET_LSB_ADR STRIM LSB 00000000 bbbbbbbb 0x1C TX_OFFSET_MSB_ADR Not Used Not Used Not Used Not Used STRIM MSB ----0000 ----bbbb m 0x1D MODE_OVERRIDE_ADR RSVD RSVD FRC SEN FRC AWAKE Not Used Not Used RST 00000--0 wwwww--w FRC 0000000- bbbbbbb- 0x1E RX_OVERRIDE_ADR ACK RX RXTX DLY MAN RXACK RXDR DIS CRC0 DIS RXCRC ACE Not Used o MAN 00000000 bbbbbbbb 0x1F TX_OVERRIDE_ADR ACK TX FRC PRE RSVD TXACK OVRD ACK DIS TXCRC RSVD TX INV c 0x26 XTAL_CFG_ADR RSVD RSVD RSVD RSVD START DLY RSVD RSVD RSVD 00000000 wwwwwwww e 0x27 CLK_OVERRIDE_ADR RSVD RSVD RSVD RSVD RSVD RSVD RXF RSVD 00000000 wwwwwwww r 0x28 CLK_EN_ADR RSVD RSVD RSVD RSVD RSVD RSVD RXF RSVD 00000000 wwwwwwww 0x29 RX_ABORT_ADR RSVD RSVD ABORT EN RSVD RSVD RSVD RSVD RSVD 00000000 wwwwwwww t 0x32 AUTO_CAL_TIME_ADR AUTO_CAL_TIME 00000011 wwwwwwww o 0x35 AUTO_CAL_OFFSET_ADR AUTO_CAL_OFFSET 00000000 wwwwwwww N 0x39 ANALOG_CTRL_ADR RSVD RSVD RSVD RSVD RSVD RSVD RX INV ALL SLOW 00000000 wwwwwwww Register Files 0x20 TX_BUFFER_ADR TX Buffer File -------- wwwwwwww 0x21 RX_BUFFER_ADR RX Buffer File -------- rrrrrrrr 0x22 SOP_CODE_ADR SOP Code File Note 5 bbbbbbbb 0x23 DATA_CODE_ADR Data Code File Note 6 bbbbbbbb 0x24 PREAMBLE_ADR Preamble File Note 7 bbbbbbbb 0x25 MFG_ID_ADR MFG ID File NA rrrrrrrr Notes 1. b = read/write; r = read only; w = write only; ‘-’ = not used, default value is undefined. 2. Registers must be configured or accessed only when the radio is in IDLE or SLEEP mode. The PMU, GPIOs, and RSSI registers can be accessed in Active Tx and Rx mode. 3. PFET Bit: Setting this bit to "1" disables the FET, therefore safely allowing Vbat to be connected to a separate reference from Vcc when the PMU is disabled to the radio. 4. EOP_CTRL_ADR[6:4] must never have the value of “000”, that is, EOP Hint Symbol count must never be “0” 5. SOP_CODE_ADR default = 0x17FF9E213690C782. 6. DATA_CODE_ADR default = 0x02F9939702FA5CE3012BF1DB0132BE6F. 7. PREAMBLE_ADR default = 0x333302. The count value must be great than 4 for DDR and greater than 8 for SDR. Document Number: 38-16015 Rev. *L Page 15 of 30

CYRF6936 Absolute Maximum Ratings Static Discharge Voltage (Digital) [9] ........................>2000 V Static Discharge Voltage (RF) [9] .............................. 1100 V Exceeding maximum ratings may shorten the useful life of the Latch Up Current ....................................+200 mA, –200 mA device. User guidelines are not tested. Operating Conditions Storage Temperature ...............................–65 °C to +150 °C Ambient Temperature VCC ..................................................................2.4 V to 3.6 V with Power Applied ..................................–55 °C to +125 °C V ..................................................................1.8 V to 3.6 V I/O Supply Voltage on any power supply pin V .................................................................1.8 V to 3.6 V BAT relative to V ..............................................–0.3 V to +3.9 V SS T (Ambient Temperature Under Bias) ..........0 °C to +70 °C A DC Voltage to Logic Inputs [8] ...............–0.3 V to V +0.3 V I/O Ground Voltage ................................................................0 V s DC Voltage applied to Outputs F (Crystal Frequency) .........................12 MHz ± 30 ppm in High-Z State ......................................–0.3 V to V +0.3 V OSC n I/O g DC Characteristics i s (T = 25C, VBAT = 2.4 V, PMU disabled, fOSC = 12.000000 MHz) e d Parameter Description Conditions Min Typ Max Unit V Battery Voltage 0C–70 C 1.8 – 3.6 V w BAT VREG[10] PMU Output Voltage 2.4 V mode 2.4 2.43 – V e VREG[10] PMU Output Voltage 2.7 V mode 2.7 2.73 – V n V [11] V Voltage 1.8 – 3.6 V I/O I/O r V V Voltage 0C–70 C 2.4[12] – 3.6 V o CC CC V Output High Voltage Condition 1 At I = –100.0 µA V – 0.2 V – V f OH1 OH I/O I/O d V Output High Voltage Condition 2 At I = –2.0 mA V – 0.4 V – V OH2 OH I/O I/O e V Output Low Voltage At I = 2.0 mA – 0 0.45 V OL OL d V Input High Voltage 0.7 V – V V IH I/O I/O n V Input Low Voltage 0 – 0.3 V V IL I/O e IIL Input Leakage Current 0 < VIN < VI/O –1 0.26 +1 µA m C Pin Input Capacitance except XTAL, RF , RF , RF – 3.5 10 pF IN N P BIAS m I (GFSK)[13] Average TX I , 1 Mbps, PA = 5, 2 way, 4 bytes/10 ms – 0.87 – mA CC CC slow channel o ICC (32-8DR)[13] Average TX ICC, 250 kbps, PA = 5, 2 way, 4 bytes/10 ms – 1.2 – mA c fast channel e I [14] Sleep Mode I – 0.8 10 µA SB CC r ISB[14] Sleep Mode ICC PMU enabled – 31.4 – µA t o IDLE I Radio off, XTAL Active XOUT disabled – 1.0 – mA CC N Notes 8. It is permissible to connect voltages above VI/O to inputs through a series resistor limiting input current to 1 mA. AC timing not guaranteed. 9. Human Body Model (HBM). 10.VREG depends on battery input voltage. 11.In sleep mode, the I/O interface voltage reference is VBAT. 12.In sleep mode, VCC min. can be as low as 1.8 V. 13.Includes current drawn while starting crystal, starting synthesizer, transmitting packet (including SOP and CRC16), changing to receive mode, and receiving ACK handshake. Device is in sleep except during this transaction. 14.ISB is not guaranteed if any I/O pin is connected to voltages higher than VI/O. Document Number: 38-16015 Rev. *L Page 16 of 30

CYRF6936 DC Characteristics (continued) (T = 25C, V = 2.4 V, PMU disabled, f = 12.000000 MHz) BAT OSC Parameter Description Conditions Min Typ Max Unit I I during Synth Start – 8.4 – mA synth CC TX I I during Transmit PA = 5 (–5 dBm) – 20.8 – mA CC CC TX I I during Transmit PA = 6 (0 dBm) – 26.2 – mA CC CC TX I I during Transmit PA = 7 (+4 dBm) – 34.1 – mA CC CC s RX I I during Receive LNA off, ATT on – 18.4 – mA CC CC n RX I I during Receive LNA on, ATT off – 21.2 – mA CC CC g Boost Eff PMU Boost Converter Efficiency V = 2.5 V, V = 2.73 V, – 81 – % BAT REG i I = 20 mA s LOAD e I [8] Average PMU External Load V = 1.8 V, V = 2.73 V, – – 15 mA LOAD_EXT BAT REG current 0C–50 C, RX Mode d ILOAD_EXT[8] Average PMU External Load VBAT = 1.8 V, VREG = 2.73 V, – – 10 mA w current 50 C–70 C, RX Mode e n r o f d e d n e m m o c e r t o N Note 8. ILOAD_EXT is dependent on external components and this entry applies when the components connected to L/D are SS12 series diode and DH53100LC inductor from Sumida. Document Number: 38-16015 Rev. *L Page 17 of 30

CYRF6936 AC Characteristics SPI Interface Parameter [9, 10] Description Min Typ Max Unit t SPI Clock Period 238.1 – – ns SCK_CYC t SPI Clock High Time 100 – – ns SCK_HI t SPI Clock Low Time 100 – – ns SCK_LO s t SPI Input Data Setup Time 25 – – ns DAT_SU n t SPI Input Data Hold Time 10 – – ns DAT_HLD g tDAT_VAL SPI Output Data Valid Time 0 – 50 ns i s t SPI Output Data Tri-state (MOSI from Slave Select Deassert) – – 20 ns DAT_VAL_TRI e t SPI Slave Select Setup Time before first positive edge of SCK[11] 10 – – ns SS_SU d tSS_HLD SPI Slave Select Hold Time after last negative edge of SCK 10 – – ns w t SPI Slave Select Minimum Pulse Width 20 – – ns SS_PW e t SPI Slave Select Setup Time 10 – – ns SCK_SU n t SPI SCK Hold Time 10 – – ns SCK_HLD t Minimum RST Pin Pulse Width 10 – – ns r RESET o Figure 10. SPI Timing f d t SCK_CYC e SCK tSCK_HI tSCK_LO tSCK_HLD d t n SCK_SU nSS tSS_SU tSS_HLD e t t m DAT_SU DAT_HLD MOSI input m tDAT_VAL tDAT_VAL_TRI MISO o c e MOSI output r t o N Notes 9. AC values are not guaranteed if voltage on any pin exceeding VI/O. 10.CLOAD = 30 pF 11.SCK must start low at the time SS goes LOW, otherwise the success of SPI transactions are not guaranteed. Document Number: 38-16015 Rev. *L Page 18 of 30

CYRF6936 RF Characteristics Radio Parameters Parameter Description Conditions Min Typ Max Unit RF Frequency Range Note 12 2.400 – 2.497 GHz Receiver (T = 25°C, VCC = VBAT = 3.0 V, fOSC = 12.000000 MHz, BER < 1E-3) Sensitivity 125 kbps 64-8DR BER 1E-3 – –97 – dBm Sensitivity 250 kbps 32-8DR BER 1E-3 – –93 – dBm Sensitivity CER 1E-3 –80 –87 – dBm s Sensitivity GFSK BER 1E-3, ALL SLOW = 1 – –84 – dBm n LNA Gain – 22.8 – dB g ATT Gain – –31.7 – dB i s Maximum Received Signal LNA On –15 –6 – dBm e RSSI Value for LNA On – 21 – Count d PWR –60 dBm [13] in RSSI Slope – 1.9 – dB/Count w Interference Performance (CER 1E-3) e Co-channel Interference C = –60 dBm – 9 – dB n rejection Carrier-to-Interference (C/I) r o Adjacent (±1 MHz) channel C = –60 dBm – 3 – dB selectivity C/I 1 MHz f Adjacent (±2 MHz) channel C = –60 dBm – –30 – dB d selectivity C/I 2 MHz e Adjacent (> 3 MHz) channel C = –67 dBm – –38 – dB d selectivity C/I > 3 MHz n Out-of-Band Blocking 30 C = –67 dBm – –30 – dBm e MHz–12.75 MHz [14] m Intermodulation C = –64 dBm, f = 5, 10 MHz – –36 – dBm Receive Spurious Emission m 800 MHz 100 kHz ResBW – –79 – dBm o 1.6 GHz 100 kHz ResBW – –71 – dBm c 3.2 GHz 100 kHz ResBW – –65 – dBm e r t o N Notes 12.Subject to regulation. 13.RSSI value is not guaranteed. Extensive variation from part to part. 14.Exceptions F/3 & 5C/3. Document Number: 38-16015 Rev. *L Page 19 of 30

CYRF6936 Radio Parameters (continued) Parameter Description Conditions Min Typ Max Unit Transmitter (T = 25°C, VCC = 3.0 V) Maximum RF Transmit Power PA = 7 +2 4 +6 dBm Maximum RF Transmit Power PA = 6 –2 0 +2 dBm Maximum RF Transmit Power PA = 5 –7 –5 –3 dBm Maximum RF Transmit Power PA = 0 – –35 – dBm RF Power Control Range – 39 – dB s RF Power Range Control Step Seven steps, monotonic – 5.6 – dB n Size g Frequency Deviation Min PN Code Pattern 10101010 – 270 – kHz i Frequency Deviation Max PN Code Pattern 11110000 – 323 – kHz s Error Vector Magnitude >0 dBm – 10 – %rms e (FSK error) d Occupied Bandwidth –6 dBc, 100 kHz ResBW 500 876 – kHz w Transmit Spurious Emission (PA = 7) e In-band Spurious Second – –38 – dBm Channel Power (±2 MHz) n In-band Spurious Third Channel – –44 – dBm r Power (>3 MHz) o Non-Harmonically Related Spurs – –38 – dBm f (800 MHz) d Non-Harmonically Related Spurs – –34 – dBm e (1.6 GHz) d Non-Harmonically Related Spurs – –47 – dBm (3.2 GHz) n Harmonic Spurs (Second – –43 – dBm e Harmonic) m Harmonic Spurs (Third – –48 – dBm Harmonic) m Fourth and Greater Harmonics – –59 – dBm o Power Management (Crystal PN# eCERA GF-1200008) c Crystal Start to 10ppm – 0.7 1.3 ms e Crystal Start to IRQ XSIRQ EN = 1 – 0.6 – ms r Synth Settle Slow channels – – 270 µs t o Synth Settle Medium channels – – 180 µs N Synth Settle Fast channels – – 100 µs Link Turnaround Time GFSK – – 30 µs Link Turnaround Time 250 kbps – – 62 µs Link Turnaround Time 125 kbps – – 94 µs Link Turnaround Time <125 kbps – – 31 µs Max Packet Length <60 ppm crystal-to-crystal – – 40 bytes all modes except 64-DDR and 64-SDR Max Packet Length <60 ppm crystal-to-crystal – – 16 bytes 64-DDR and 64-SDR Document Number: 38-16015 Rev. *L Page 20 of 30

CYRF6936 Typical Operating Characteristics Figure 11. Typical Operating Characteristics [15] Transmit Power vs. Temperature Transmit Power vs. Vcc Transmit Power vs. Channel (Vcc = 2.7v) (PMU off) 6 46 PA7 46 PA7 4 PA7 Output Power (dBm) ------1102864220 PPPAAA465 Output Power (dBm) ------1102864220 PPPAAA465 Output Power (dBm) ------1102864220 PPPAAA456 gns -14 -14 -14 si 0 20 40 60 2.4 2.6 2.8 3 3.2 3.4 3.6 0 20 40 60 80 Temp (deg C) Vcc Channel e d Typical RSSI Count vs Input Power Average RSSI vs. Temperature Average RSSI vs. Vcc (Rx signal = -70dBm) (Rx signal = -70dBm) w 32 19 20 18 19 e 18 24 17 17 n RSSI Count 16 LNA ONLNA OFFLANTAT OOFNF RSSI Count 111456 RSSI Count 11113456 or 8 12 f 13 11 0 12 10 d -120 -100 -80 -60 -40 -20 0 20 40 60 2.4 2.6 2.8 3 3.2 3.4 3.6 Input Power (dBm) Temp (deg C) Vcc e d (RRxS SsIi gvnsa.l C=h a-n7n0delBm) Rx Sen(s1iMtbipvsi tCyE Rv)s. Vcc Rx Sensiti(v1iMtbyp sv sC.E RT)emperature n 18 -80 -80 e RSSI Count 111124680246 Receiver Sensitivity (dBm) ------998888208642 8DCRE3R2 Receiver Sensitivity (dBm) ------998888208642 8DCRE3R2 ecomm 0 -94 -94 0 20 40 60 80 2.4 2.6 2.8 3 3.2 3.4 3.6 0 20 40 60 r Channel Vcc Temp (deg C) t o Receiver Sensitivity vs. Frequency Offset Receiver Sensitivity vs Channel Carrier to Interferer (3.0v, Room Temp) (Narrow band, LP modulation) N -80 Receiver Sensitivity (dBm) --------9999888864208642 8DDGDRFRS63K42 Receiver Sensitivity (dBm) -------99888883197531 GCD8FEDDSRRRK3322 C/I (dB) -----125432100000000........00000000 -98 -95 -60.0 -150 -100 -50 0 50 100 150 0 20 40 60 80 -10 -5 0 5 10 Crystal Offset (ppm) Channel Channel Offset (MHz) Note 15.With LNA on, ATT off, above -2dBm erroneous RSSI values may be read. Cross-checking RSSI with LNA off/on is recommended for accurate readings. Document Number: 38-16015 Rev. *L Page 21 of 30

CYRF6936 Typical Operating Characteristics (continued) BER vs. Data Threshold (32-DDR) BER vs. Data Threshold (32-8DR) GFSK vs. BER (SOP Threshold = 5, C38 slow) (SOP Threshold = 5, C38 slow) (SOP Threshold = 5, C38 slow) 10 10 100 1 3 1 0 1 0 Thru 7 10 6 1 0.1 0.1 %BER 0.01 %BER 0.01 %BER 00..011 0.001 0.001 0.001 s 0.0001 0.0001 0.0001 GFSK n 0.00001 0.00001 0.00001 -100 -95 -90 -85 -80 -75 -70 -100 -95 -90 -85 -80 -75 -70 -100 -80 -60 -40 -20 0 g Input Power (dBm) Input Power (dBm) Input Power (dBm) i s ICC RX ICC RX ICC RX SYNTH e (LNA OFF) (LNA ON) 21 25 9.2 d OPERATING CURRENT (mA) 11127890112....8905555 3322....0374 VVVV OPERATING CURRENT (mA)222220123422222.....0123455555 3322....0374 VVVV OPERATING CURRENT (mA) 8888888889..........891234567891 3322....0374 VVVV r new 19.5 7.9 o 17 19 7.8 0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 0 5 10 1520 25 30 35 40 45 5055 60 65 70 0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 f TEMPERATURE (C) TEMPERATURE (C) TEMPERATURE (C) d ICC TX SYNTH ICC TX @ PA0 ICC TX @ PA1 e 9.2 17 17.5 d 9.1 OPERATING CURRENT (mA) 888888888.........89123456789 3322....0374 VVVV OPERATING CURRENT (mA) 11145611...56555 3322....0374 VVVV OPERATING CURRENT (mA) 111456111...567555 3322....0374 VVVV mmen 7.9 o 7.8 14 14 0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 0 5 10 15 20 25 30 3540 45 50 55 60 65 70 0 5 10 15 20 25 30 35 40 45 50 55 60 65 70 c TEMPERATURE (C) TEMPERATURE (C) TEMPERATURE (C) e r ICC TX @ PA2 ICC TX @ PA3 ICC TX @ PA4 18 19 20.5 ot OPERATING CURRENT (mA) 11156711...67555 3322....0374 VVVV OPERATING CURRENT (mA) 111678111...678555 3322....0374 VVVV OPERATING CURRENT (mA) 1117891112...7890555 3322....0374 VVVV N 15 15.5 16.5 0 5 10 15 20 2530 35 4045 50 55 6065 70 0 5 10 15 20 2530 35 4045 50 55 6065 70 0 5 10152025303540455055606570 TEMPERATURE (C) TEMPERATURE (C) TEMPERATURE (C) Document Number: 38-16015 Rev. *L Page 22 of 30

CYRF6936 Typical Operating Characteristics (continued) ICC TX @ PA5 ICC TX @ PA6 ICC TX @ PA7 23.5 30 40.5 40 OPERATING CURRENT (mA)2220122222...0123555 3322....0374 VVVV OPERATING CURRENT (mA) 222225678922222.....5678955555 3322....0374 VVVV OPERATING CURRENT (mA) 333333334567893333333.......34567895555555 3322....0374 VVVV ns 19.5 24.5 32.5 0 5 10152025303540455055606570 0 5 10152025303540455055606570 0 5 10152025303540455055606570 g TEMPERATURE (C) TEMPERATURE (C) TEMPERATURE (C) i s e d AC Test Loads and Waveforms for Digital Pins w Figure 12. AC Test Loads and Waveforms for Digital Pins e n AC Test Loads DC Test Load OUTPUT OUTPUT R1 r VCC o 30 pF 5 pF OUTPUT f IJNIGC LAUNDDING IJNIGC LAUNDDING R2 d SCOPE Max SCOPE Typical e ALL INPUT PULSES d Parameter Unit VCC 90% 90% n R1 1071 10% 10% e R2 937 GND m Fall time: 1 V/ns RTH 500 Rise time: 1 V/ns V 1.4 V m TH Equivalent to: THÉVENIN EQUIVALENT V 3.00 V CC RTH o OUTPUT VTH c e r t o N Document Number: 38-16015 Rev. *L Page 23 of 30

CYRF6936 Ordering Information Part Number Radio Package Name Package Type Operating Range CYRF6936-40LTXC Transceiver 40-pin QFN 40-pin QFN (Sawn type) Commercial Ordering Code Definitions CY RF 6936 - 40 XX X C s Temperature Range: n C = Commercial g Pb-free i s Package Type: XX = LF or LT e LF = 40-pin QFN LT = 40-pin QFN (Sawn Type) d No of pins in package / KGD Level: w 40 = 40 pins e Part Number n Marketing Code: RF = Wireless (radio frequency) product line Company ID: CY = Cypress r o f d e d n e m m o c e r t o N Document Number: 38-16015 Rev. *L Page 24 of 30

CYRF6936 Package Diagrams The recommended dimension of the PCB pad size for the E-PAD underneath the QFN is 3.5 mm × 3.5 mm (width × length). Figure 13. 40-pin QFN (6 × 6 × 1.0 mm) 3.5 × 3.5 E-Pad (Subcon Punch Type Package) Package Outline, 001-12917 s n g i s e d w e n r o f d e d n e m m o 001-12917 *D c e r t o N Document Number: 38-16015 Rev. *L Page 25 of 30

CYRF6936 Package Diagrams (continued) The recommended dimension of the PCB pad size for the E-PAD underneath the QFN is 3.5 mm × 3.5 mm (width × length). Figure 14. 40-pin QFN (6 × 6 × 0.90 mm) 3.5 × 3.5 E-Pad (Sawn) Package Outline, 001-44328 s n g i s e d w e n r o f d e d n e m 001-44328 *G m o c e r t o N Document Number: 38-16015 Rev. *L Page 26 of 30

CYRF6936 Acronyms Document Conventions Table 6. Acronyms Used in this Document Units of Measure Acronym Description Table 7. Units of Measure ACK Acknowledge (packet received, no errors) Symbol Units of Measure BER Bit Error Rate dB decibel BOM Bill Of Materials dBc decibel relative to carrier CMOS Complementary Metal Oxide Semiconductor dBm decibel-milliwatt CRC Cyclic Redundancy Check °C degree Celsius s Hz hertz n GFSK Gaussian Frequency-Shift Keying KB 1024 bytes g HBM Human Body Model Kbit 1024 bits si ISM Industrial, Scientific, and Medical kHz kilohertz e IRQ Interrupt Request k kilohm d MCU Microcontroller Unit MHz megahertz w QFN Quad Flat No-leads M megaohm RSSI Received Signal Strength Indication e A microampere RF Radio Frequency s microsecond n Rx Receive V microvolt r o Tx Transmit Vrms microvolts root-mean-square f W microwatt d mA milliampere e ms millisecond d mV millivolt n nA nanoampere e ns nanosecond m nV nanovolt m ohm pp peak-to-peak o ppm parts per million c ps picosecond e V volt r t o N Document Number: 38-16015 Rev. *L Page 27 of 30

CYRF6936 Document History Page Description Title: CYRF6936, WirelessUSB™ LP 2.4 GHz Radio SoC Document Number: 38-16015 Orig. of Submission Revision ECN Description of Change Change Date ** 307437 TGE See ECN New data sheet *A 377574 TGE See ECN Preliminary release– - updated Section 1.0 - Features s - updated Section 2.0 - Applications - added Section 3.0 - Applications Support n - updated Section 4.0 - Functional Descriptions g - updated Section 5.0 - Pin Description i - added Figure 5-1 s - updated Section 6.0 - Functional Overview e - added Section 7.0 - Functional Block Overview d - added Section 9.0 - Register Descriptions - updated Section 10.0 - Absolute Maximum Ratings w - updated Section 11.0 - Operating Conditions - updated Section 12.0 - DC Characteristics e - updated Section 13.0 - AC Characteristics n - updated Section 14.0 - RF Characteristics - added Section 16.0 - Ordering Information r *B 398756 TGE See ECN ES-10 update- o - changed part no. f - updated Section 9.0 - Register Descriptions d - updated Section 12.0 - DC Characteristics - updated Section 14.0 - RF Characteristics e *C 412778 TGE See ECN ES-10 update- d - updated Section 4.0 - Functional Descriptions n - updated Section 5.0 - Pin Descriptions e - updated Section 6.0 - Functional Overview - updated Section 7.0 - Functional Block Overview m - updated Section 9.0 - Register Descriptions - updated Section 10.0 - Absolute Maximum Ratings m - updated Section 11.0 - Operating Conditions - updated Section 14.0 - RF Characteristics o *D 435578 TGE See ECN - updated Section 1.0 - Features c - updated Section 5.0 - Pin Descriptions e - updated Section 6.0 - Functional Overview r - updated Section 7.0 - Functional Block Overview - updated Section 9.0 - Register Descriptions t o - added Section 10.0 - Recommended Radio Circuit Schematic - updated Section 11.0 - Absolute Maximum Ratings N - updated Section 12.0 - Operating Conditions - updated Section 13.0 - DC Characteristics - updated Section 14.0 - AC Characteristics - updated Section 15.0 - RF Characteristics *E 460458 BOO See ECN Final data sheet - removed “Preliminary” notation Document Number: 38-16015 Rev. *L Page 28 of 30

CYRF6936 Document History Page (continued) Description Title: CYRF6936, WirelessUSB™ LP 2.4 GHz Radio SoC Document Number: 38-16015 Orig. of Submission Revision ECN Description of Change Change Date *F 487261 TGE See ECN - updated Section 1.0 - Features - updated Section 5.0 - Pin Descriptions - updated Section 6.0 - Functional Overview - updated Section 7.0 - Functional Block Overview - updated Section 8.0 - Application Example s - updated Section 9.0 - Register Descriptions n - updated Section 12.0 - DC Characteristics - updated Section 13.0 - AC Characteristics g - updated Section 14.0 - RF Characteristics i - added Section 15.0 - Typical Operating Characteristics s e *G 778236 OYR / ARI See ECN - modified radio function register descriptions - changed L/D pin description d - footnotes added - changed RST Capacitor from 0.1uF to 0.47 uF w - updated Figure 9, Recommended Circuit for Systems - updated Table 3, Recommended bill of materials for systems e - updated package diagram from ** to *A n *H 2640987 VNY / OYR 02/20/2009 - Removed range values in features description / TGE / - Bit level register details removed and appended to the Wireless LP and PRoC r o AESA TRM - updated register summary table 4 f - updated pin description diagram (figure 1) d - updated the schematic of the radio (figure 10). e - Removed Backward Compatibility section. - Removed Table 2 d - Updated RF table characteristics for Payload size n - Added pkg diagram 001-12917 e - Updated BOM Table3 on page11. - Updated Table on page19 with Receiver information (T = 25°C, m V = V = 3.0 V, f = 12.000000 MHz, BER < 1E-3) CC BAT OSC m *I 2673333 TGE / 03/13/2009 Corrected Figure 9 on page 13 PYRS Updated packaging and ordering information for 40 QFN (sawn) package o *J 3232571 JCJC 04/18/2011 Added section Receive Spurious Response on page 9. c Added note # 13 and referred in Table on page 19. Added Ordering Code Definitions under Ordering Information. e Updated Package Diagrams: r spec 001-12917 – Changed revision from *A to *C. spec 001-44328 – Changed revision from *C to *D. t Added Acronyms and Units of Measure. o Updated to new template. N *K 4359286 DEJO 04/24/2014 Updated Package Diagrams: spec 001-12917 – Changed revision from *C to *D. spec 001-44328 – Changed revision from *D to *F. Updated to new template. Completing Sunset Review. *L 5742403 SGUP 05/19/2017 Added watermark “Not recommended for new designs” across the document. Updated Ordering Information: Updated part numbers. Updated Package Diagrams: spec 001-44328 – Changed revision from *F to *G. Updated to new template. Document Number: 38-16015 Rev. *L Page 29 of 30

CYRF6936 Sales, Solutions, and Legal Information Worldwide Sales and Design Support Cypress maintains a worldwide network of offices, solution centers, manufacturer’s representatives, and distributors. To find the office closest to you, visit us at Cypress Locations. Products PSoC® Solutions ARM® Cortex® Microcontrollers cypress.com/arm PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP Automotive cypress.com/automotive Cypress Developer Community Clocks & Buffers cypress.com/clocks Forums | WICED IOT Forums | Projects | Video | Blogs | s Interface cypress.com/interface Training | Components n Internet of Things cypress.com/iot Technical Support g Memory cypress.com/memory i cypress.com/support s Microcontrollers cypress.com/mcu e PSoC cypress.com/psoc d Power Management ICs cypress.com/pmic w Touch Sensing cypress.com/touch USB Controllers cypress.com/usb e Wireless Connectivity cypress.com/wireless n r o f d e d n e m m o c e r © Cypress Semiconductor Corporation, 2005–2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries t worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other o intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to N modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited. TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products. Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners. Document Number: 38-16015 Rev. *L Revised May 19, 2017 Page 30 of 30

Datasheet下载

Datasheet下载