- 型号: XIO2001PNP

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

XIO2001PNP产品简介:

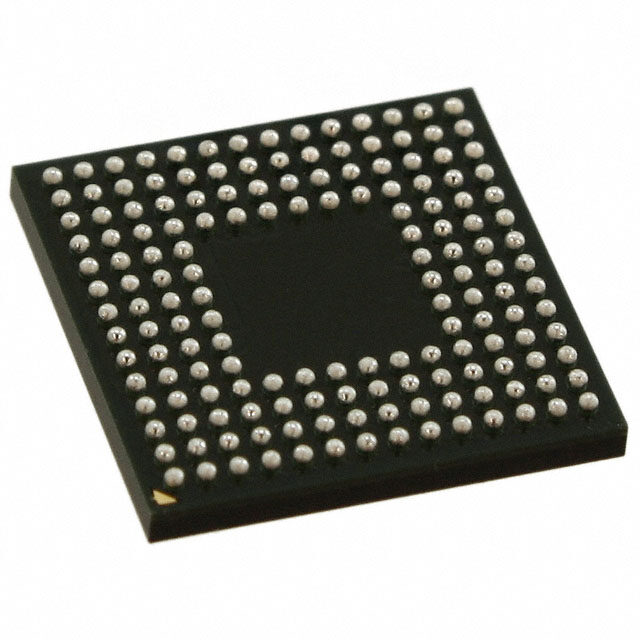

ICGOO电子元器件商城为您提供XIO2001PNP由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 XIO2001PNP价格参考¥20.00-¥37.15。Texas InstrumentsXIO2001PNP封装/规格:接口 - 专用, PCI Express to PCI Translation Bridge Interface 128-HTQFP (14x14)。您可以下载XIO2001PNP参考资料、Datasheet数据手册功能说明书,资料中有XIO2001PNP 详细功能的应用电路图电压和使用方法及教程。

Texas Instruments 的 XIO2001PNP 是一款专用接口器件,主要用于 PCI Express (PCIe) 至 UART(通用异步收发器)桥接应用。它将高速 PCIe 接口转换为串行通信接口,适用于需要串口扩展或设备间串口通信的场景。 典型应用场景包括: 1. 工业自动化与控制系统:在工业设备中提供额外的串口,用于连接PLC、传感器、仪表等设备。 2. 通信设备:用于路由器、交换机等设备中,提供控制台端口或管理接口。 3. 嵌入式系统开发平台:为嵌入式系统提供调试串口或扩展通信接口。 4. 服务器与存储设备:用于系统管理、日志记录或远程维护的串口连接。 5. 测试与测量设备:在测试设备中作为数据采集或控制信号的串口接口。 该芯片支持多通道串口通信,具备高集成度和低功耗特性,适合嵌入式和便携式应用。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC PCI-EXPRESS BRIDGE 128HTQFPPCI接口IC x1 PCI Exp to PCI Bus Trans Bridge |

| DevelopmentKit | XIO2001EVM |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 接口 IC,PCI接口IC,Texas Instruments XIO2001PNP- |

| NumberofLanes | 1 Lane |

| 数据手册 | 点击此处下载产品Datasheethttp://www.ti.com/lit/pdf/slyb174 |

| 产品型号 | XIO2001PNP |

| PCN组件/产地 | |

| 产品种类 | PCI接口IC |

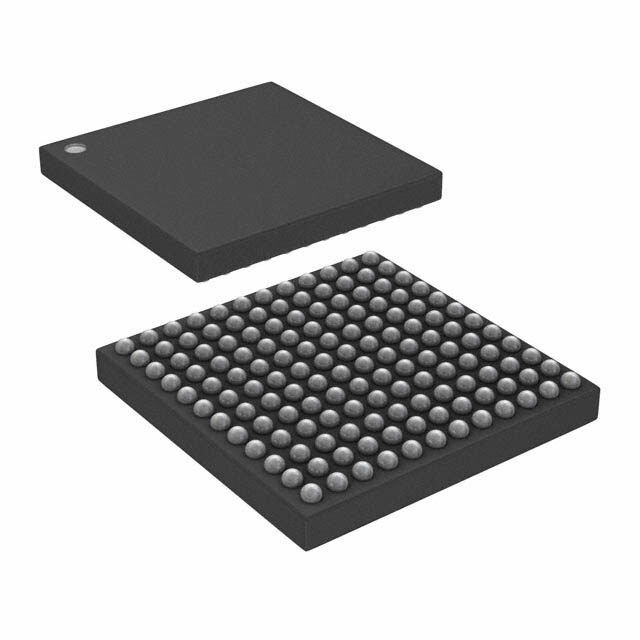

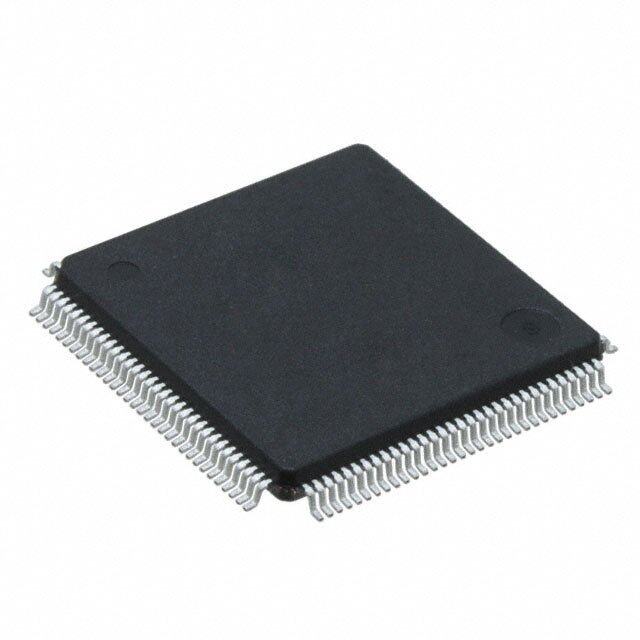

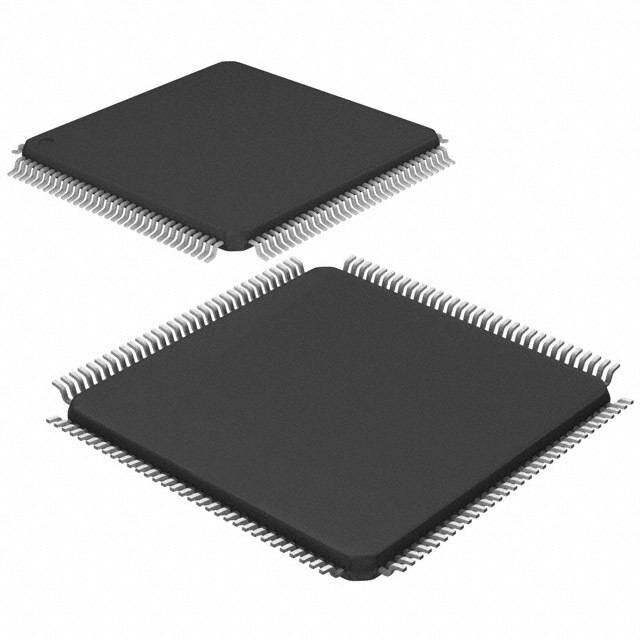

| 供应商器件封装 | 128-HTQFP(14x14) |

| 其它名称 | 296-32787 |

| 包装 | 托盘 |

| 商标 | Texas Instruments |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Tray |

| 封装/外壳 | 128-TQFP 裸露焊盘 |

| 封装/箱体 | HTQFP-128 |

| 工作电源电压 | 3.3 V, 1.5 V |

| 工厂包装数量 | 90 |

| 应用 | PCI Express 至 PCI 转换桥 |

| 接口 | PCI Express |

| 数据总线宽度 | 32 bit |

| 最大工作温度 | + 70 C |

| 最大数据速率 | 2 Gbps |

| 最大时钟频率 | 66 MHz |

| 最小工作温度 | 0 C |

| 标准包装 | 90 |

| 电压-电源 | 1.35 V ~ 1.65 V,3 V ~ 3.6 V |

| 类型 | Bridge - PCIe to PCI |

| 系列 | XIO2001 |

| 通道数 | 1 Lane |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Product Sample & Technical Tools & Support & Folder Buy Documents Software Community XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 XIO2001 PCI Express to PCI Bus Translation Bridge 1 Features • Five3.3-V,Multifunction,General-PurposeI/O Terminals • Full×1PCIExpress™Throughput 1 • Memory-MappedEEPROMSerial-BusController • FullyCompliantWith PCIExpresstoPCI/PCI-X SupportingPCIExpressPowerBudget/Limit BridgeSpecification,Revision1.0 ExtensionsforAdd-InCards • FullyCompliantWith PCIExpressBase • CompactFootprint,Lead-Free144-Ball,ZAJ Specification,Revision2.0 MicroStar™BGA,Lead-Free169-BallZGU • FullyCompliantWith PCILocalBusSpecification, MicroStarBGA,andPowerPad™HTQFP128-Pin Revision2.3 PNPPackage • PCIExpressAdvancedErrorReportingCapability IncludingECRCSupport 2 Applications • SupportforD1,D2,D3 ,andD3 hot cold • ConsumerApplications: • Active-StateLinkPowerManagementSaves – PC PowerWhenPacketActivityonthePCIExpress – Notebooks LinkisIdle,UsingBothL0sandL1States – PCIeAdd-InCards • WakeEventandBeaconSupport – Multi-FunctionPrinters • ErrorForwardingIncludingPCIExpressData PoisoningandPCIBusParityErrors – NetworkRoutersandSwitches • Uses100-MHzDifferentialPCIExpressCommon • IndustrialApplications ReferenceClockor125-MHzSingle-Ended, – IndustrialPCs ReferenceClock – VideoSurveillanceSystems • OptionalSpreadSpectrumReferenceClockis Supported 3 Description • RobustPipelineArchitecturetoMinimize The XIO2001 is a single-function PCI Express to PCI TransactionLatency translation bridge that is fully compliant to the PCI Express to PCI/PCI-X Bridge Specification, Revision • FullPCILocalBus66-MHz/32-BitThroughput 1.0. For downstream traffic, the bridge simultaneously • SupportforSixSubordinatePCIBusMasterswith supports up to eight posted and four non-posted InternalConfigurable,2-LevelPrioritization transactions. For upstream traffic, up to six posted Scheme and four non-posted transactions are simultaneously • InternalPCIArbiterSupportingUpto6External supported. PCIMasters The PCI Express interface is fully compliant to the • AdvancedPCIExpressMessageSignaled PCIExpressBaseSpecification,Revision2.0. InterruptGenerationforSerialIRQInterrupts The PCI Express interface supports a ×1 link • ExternalPCIBusArbiterOption operating at full 250 MB/s packet throughput in each • PCIBus LOCKSupport direction simultaneously. Also, the bridge supports the advanced error reporting including extended CRC • JTAG/BSforProductionTest (ECRC) as defined in the PCI Express Base • PCI-Express CLKREQ Support Specification. Supplemental firmware or software is • ClockRunandPowerOverrideSupport requiredtofullyusebothofthesefeatures. • SixBufferedPCIClockOutputs(25MHz,33MHz, DeviceInformation(1) 50MHz,or66MHz) PARTNUMBER PACKAGE BODYSIZE(NOM) • PCIBusInterface3.3-Vand5.0-V(25MHzor 33MHzonlyat5.0V)ToleranceOptions HTQFP(128) 14.00mm×14.00mm NFBGA(144) 7.00mm×7.00mm • IntegratedAUXPowerSwitchDrainsV Power XIO2001 AUX OnlyWhenMainPowerIsOff BGAMICROSTAR 12.00mm×12.00mm (169) (1) For all available packages, see the orderable addendum at theendofthedatasheet. 1 An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectualpropertymattersandotherimportantdisclaimers.PRODUCTIONDATA.

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com TypicalDiagram 2 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 Table of Contents 1 Features.................................................................. 1 7 ParameterMeasurementInformation................24 2 Applications........................................................... 1 8 DetailedDescription............................................ 26 3 Description............................................................. 1 8.1 Overview.................................................................26 4 RevisionHistory..................................................... 3 8.2 FunctionalBlockDiagram.......................................26 5 PinConfigurationandFunctions......................... 5 8.3 FeatureDescription.................................................26 5.1 PinAssignments.......................................................5 8.4 RegisterMaps ........................................................42 5.2 PinDescriptions........................................................8 8.5 PCIExpressExtendedConfigurationSpace..........91 8.6 Memory-MappedTIProprietaryRegisterSpace..102 6 Specifications....................................................... 15 9 Application,Implementation,andLayout....... 114 6.1 AbsoluteMaximumRatings....................................15 6.2 HandlingRatings.....................................................15 9.1 ApplicationInformation..........................................114 6.3 RecommendedOperatingConditions.....................15 9.2 TypicalApplication................................................114 6.4 ThermalInformation ...............................................16 9.3 Layout................................................................... 124 6.5 NominalPowerConsumption.................................17 9.4 PowerSupplyRecommendations.........................127 6.6 PCIExpressDifferentialTransmitterOutput 10 DeviceandDocumentationSupport............... 130 Ranges.....................................................................17 10.1 DocumentsConventions.....................................130 6.7 PCIExpressDifferentialReceiverInputRanges....18 10.2 DocumentationSupport......................................131 6.8 PCIExpressDifferentialReferenceClockInput 10.3 Trademarks.........................................................131 Ranges.................................................................... 19 10.4 ElectrostaticDischargeCaution..........................131 6.9 PCIBusElectricalCharacteristics .........................20 10.5 Glossary..............................................................131 6.10 3.3-VI/OElectricalCharacteristics ......................20 11 Mechanical,Packaging,andOrderable 6.11 PCIBusTimingRequirements.............................21 Information......................................................... 131 6.12 Power-Up/-DownSequencing...............................21 4 Revision History REVISION REVISION REVISIONCOMMENTS DATE NUMBER 5/2009 – Initialrelease 5/2009 A Correctedtypos 9/2009 B AddedPNPPackageandESDRatings 10/2009 C Removedterminalassignmenttablesforallpackages 1/2010 D CorrectedPNPpinout,replacedOrderingInformationwithPackageOptionAddendum CorrectedViPCIExpressREFCLK(differential)parameters 11/2011 E CorrectedVRX-DIFFp-pparameters RemovedlabelN13onthesignalVDD_15fortheZAJpackage 5/2012 F AddedmissingPNPpinnumberstotheTable2-1andtotheTable2-2 ChangedexternalpartsforCLKRUN_ENtoincludepulldownresostor DeletedNotefromCLKRUIN_ENterminal'sdescription 5/2012 G ChangedexternalPartsforEXT_ARB_ENtoincludepulldownresistor DeletedNotefromEXT_ARB_ENterminal'sdescription AddedPinConfigurationandFunctionssection,HandlingRatingtable,FeatureDescriptionsection, DeviceFunctionalModes,ApplicationandImplementationsection,PowerSupplyRecommendations section,Layoutsection,DeviceandDocumentationSupportsection,andMechanical,Packaging,and 8/2014 H OrderableInformationsection UpdatedPower-UpSequencesection IdentifiedVDD_15_PLLpins Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 3 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com Revision History (continued) REVISION REVISION REVISIONCOMMENTS DATE NUMBER ChangedpinF10From:VDD_15To:VDD_15_PLLintheZGUpackage ChangedpinF11From:VDD_15To:VDD_15_PLLintheZAJpackage Changedpin84From:VDDA_15To:VDD_15_PLLinthePNPpackage ChangedthepinnamefromVDD_15_PULLtoVDD_15_PLLinthePinFunctionstable. 9/2014 I ChangedPCIRdescriptioninthePinFunctionstableFrom:"ConnectthisterminalstothesecondaryPCI bus..."To:"ConnecteachoneoftheseterminalstothesecondaryPCIbus.." DeletedtextfromtheLOCKpindescriptioninthePinFunctionstable:"whenbit12(LOCK_EN)issetin thegeneralcontrolregister(seeGeneralControlRegister)." 4 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 5 Pin Configuration and Functions 5.1 Pin Assignments TheXIO2001isavailableineithera169-ballZGUMicroStarBGAora144−ballZAJMicroStarBGApackage. Figure1 showsapindiagramoftheZGUpackage. Figure2 showsapindiagramoftheZAJpackage. Figure3 showsapindiagramofthePNPpackage. 1 2 3 4 5 6 7 8 9 10 11 12 13 N C/BE[3] AD25 AD27 AD30 AD31 INTB PRST SERIRQ GPIO0// GPIO2 GPIO3//SDA JTAG_TDI GRST NN CLKRUN M AD20 AD22 AD24 AD26 AD28 INTA INTC LOCK GPIO1// GPIO4// JTAG_TDO JTAG_TCK WAKE MM PWR_OVRD SCL L AD18 AD19 AD21 AD23 AD29 M66EN INTD VDD_33 JTAG_ JTAG_TMS VSS PME VDD_15_ LL TRST# COMB K AD16 AD17 PCIR VSS VSS VSS VDD_15 VSS VDD_33 VSSA VDD_33_ REF0_PCIE REF1_PCIE KK COMB_IO J IRDY FRAME C/BE[2] VDD_33 VSS VSS VSS VSS VSS VSS VDD_33_ VDD_33 VDD_33_ JJ AUX COMB H TRDY DEVSEL VDD_33 VSS VSS VSS VSS VSS VSS VDD_15 PERST VSSA VDDA_15 HH G STOP PERR SERR# VDD_15 VSS VSS VSS VSS VSS VDD_15 VSSA TXN TXP GG FF FF PAR C/BE[1] CLK VSS VSS VSS VSS VSS VSS VDD_15_PLL VSS VSS VDDA_15 E AD15 AD14 AD13 VDD_33 VSS VSS VSS VSS VSS VSSA VSSA RXN RXP EE D AD12 AD11 AD8 VSS VDD_33 VSS VDD_15 VSS VDD_33 VSS CLKREQ VREG_PD33 VDDA_33 DD C AD10 AD9 AD7 AD5 AD0 GNT1 VDD_33 REQ3 REQ4 EXT_ARB_EN VSSA REFCLK– REFCLK+ CC B C/BE[0] AD6 AD3 AD2 CLKOUT0 CLKOUT1 CLKOUT3 GNT2 GNT3 GNT5 CLKOUT6 PCLK66_SEL REFCLK125 BB _SEL A PCIR AD4 AD1 REQ0 GNT0 REQ1 CLKOUT2 REQ2 CLKOUT4 CLKOUT5 GNT4 REQ5 CLKRUN_EN AA 1 2 3 4 5 6 7 8 9 10 11 12 13 Figure1. XIO2001ZGUMicroStarBGAPackage(BottomView) Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 5 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com Pin Assignments (continued) 1 2 3 4 5 6 7 8 9 10 11 12 13 N AD21 AD24 AD27 AD28 AD31 INTA INTD LOCK GPIO0// GPIO2 JTAG_TDO JTAG_TCK VDD_15_ NN CLKRUN COMB M AD18 AD22 C/BE[3] AD25 AD29 M66EN INTC SERIRQ GPIO1// GPIO4_ GRST PME REF0_PCIE MM PWR_OVRD SCL L AD16 AD20 AD23 AD26 AD30 INTB PRST GPIO3//SDA JTAG_ JTAG_TDI JTAG_TMS WAKE REF1_PCIE LL TRST K C/BE[2] AD19 AD17 VDD_33_ VDD_33_ VDD_15 KK COMB_IO COMB J FRAME TRDY PCIR VSS VSS VDD_15 VDD_15 VSS VDD_33 VDD_33_ VSSA JJ AUX H STOP DEVSEL IRDY VSS VDD_33 VDD_33 VDD_15 VSS PERST VDDA_15 TXP HH G PAR SERR PERR VSS VDD_33 VDD_33 VDD_15 VSSA VDD_15 VSSA TXN GG FF CLK AD15 C/BE[1] VSS VDD_33 VDD_33 VDD_33 VSS VDD_15_PLL VSS VSSA FF E AD13 AD12 AD14 VDD_33 VSS VSS VSS VSS VREG_PD33 VDDA_15 RXP EE D AD11 AD9 PCIR CLKREQ VSSA RXN DD C AD10 C/BE[0] AD5 AD2 AD1 REQ1 REQ2 REQ3 REQ5 CLKOUT6 CLKRUN_EN VDDA_33 REFCLK+ CC B AD8 AD6 AD0 CLKOUT0 CLKOUT1 CLKOUT2 GNT2 GNT3 GNT4 GNT5 VSSA REFCLK- BB A AD7 AD4 AD3 REQ0 GNT0 GNT1 CLKOUT3 CLKOUT4 REQ4 CLKOUT5 PCLK66_ EXT_ARB_ REFCLK125 AA SEL EN _SEL 1 2 3 4 5 6 7 8 9 10 11 12 13 Figure2. XIO2001ZAJMicroStarBGAPackage(BottomView) 6 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 Pin Assignments (continued) ELEN 33 UT0 UT1 UT215UT333 UT4 UT5 33UT666_SARB_ 65D_43210KOQ0T0KOQ1T1KOD_KOD_Q2T2Q3KOT3Q4KOT4Q5T5D_KOLKT_ DDDDDDDDLENLENLDLDENELNELNENDLCX AAVAAAAACRGCRGCVCVRGRCGRCGRGVCPE 128127126125124123122121120119118117116115114113112111110109108107106105104103102101100999897 AD7 1 96 CLKRUN_EN PCIR 2 95 REFCLK125_SEL C/BE[0] 3 94 REFCLK– AD8 4 93 REFCLK+ AD9 5 92 VDDA_33 AD10 6 91 CLKREQ VDD_33 7 90 VREG_PD33 AD11 8 89 VSSA AD12 9 88 RXN AD13 10 87 RXP AD14 11 86 VSSA AD15 12 85 VDDA_15 CLK 13 84 VDD_15_PLL C/BE[1] 14 83 VDDA_15 PAR 15 82 VSSA SERR 16 81 TXN PERR 17 80 TXP STOP 18 79 VSSA VDD_33 19 78 VDDA_15 DEVSEL 20 77 PERST VDD_15 21 76 VDDA_15 TRDY 22 75 VDD_33_COMB IRDY 23 74 VDDA_33 FRAME 24 73 VDD_33_AUX C/BE[2] 25 72 REF1_PCIE AD16 26 71 REF0_PCIE PCIR 27 70 VDD_33_COM_IO AD17 28 69 VDD_15_COMB AD18 29 68 WAKE AD19 30 67 PME AD20 31 66 GRST AD21 32 65 JTAG_TCK 34567890123456789012345678901234 33333334444444444555555555566666 VDD_33AD22AD23C/BE[3]AD24AD25AD26AD27AD28AD29AD30AD31M66ENVDD_33INTAINTBINTCINTDPRSTSERIRQVDD_15LOCKPIO0 //CLKRUN1 // PWR_OVERGPIO2GPIO3 // SDAGPIO4 // SCLJTAG_TRSTJTAG_TDOVDD_33JTAG_TDIJTAG_TMS GO PI G Figure3. XIO2001PNP PowerPAD™HTQFPPackage(TopView) Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 7 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com 5.2 Pin Descriptions Thefollowinglistdescribesthedifferentinput/outputcelltypesthatappearinthepinfunctiontables: • HSDIFFIN=Highspeeddifferentialinput • HSDIFFOUT=Highspeeddifferentialoutput • PCIBUS=PCIbustri-statebidirectionalbufferwith3.3-Vor5.0-Vclamprail. • LVCMOS=3.3-VlowvoltageCMOSinputoroutputwith3.3-Vclamprail • BIAS=Input/outputterminalsthatgenerateabiasvoltagetodetermineadriver'soperatingcurrent • Feed through = These terminals connect directly to macros within the part and not through an input or output cell. • PWR=Powerterminal • GND=Groundterminal PinFunctions ZGU ZAJ PNP I/O EXTERNAL SIGNAL BALL BALL PIN DESCRIPTION TYPE PARTS NO. NO. NO. POWERSUPPLY PCIR A01, D03,J03 2,27 I/O Resistor PCIRail.5.0-Vor3.3-VPCIbusclampvoltagetosetmaximum K03 I/OvoltagetoleranceofthesecondaryPCIbussignals.Connect eachoneoftheseterminalstothesecondaryPCIbusI/Oclamp railthrougha1kΩresistor. V G04, J08, 21,53, PWR Bypass 1.5-Vdigitalcorepowerterminals DD_15 K07, H08, 113 capacitors D07, J07, H10, G08, G10 K13,G11 V F10 F11 84 PWR Pifilter 1.5-VpowerterminalforinternalPLL.Thisterminalmustbe DD_15_PLL isolatedfromanaloganddigitalpower. V F13, E12,H12 76,78, PWR Pifilter 1.5-Vanalogpowerterminal DDA_15 H13 83,85 V E04, E05, 7,19, PWR Bypass 3.3-VdigitalI/Opowerterminal DD_33 H03, G06, 33,46, capacitors J04, H07, 62,100, L08, G07, 111, K09, H06, 126 D09, F08, C07, F07, D05, F06,J11 J12 V J11 J12 73 PWR Bypass 3.3-VauxiliarypowerterminalNote:Thisterminalisconnected DD_33_AUX capacitors toV throughapulldownresistorifnoauxiliarysupplyis SS present. V D13 C12 74,92 PWR Pifilter 3.3-Vanalogpowerterminal DDA_33 GROUND V D04, E06, GND Digital SS F04, F05, ground H04, G05, terminals K04, H05, K05, J05,J06, K06, J09, K08, H09, L11, E09, J10, E08, D10, E07,F12 D08, ,F09 D06, F11, F12 8 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 Pin Descriptions (continued) PinFunctions(continued) ZGU ZAJ PNP I/O EXTERNAL SIGNAL BALL BALL PIN DESCRIPTION TYPE PARTS NO. NO. NO. V E05, GND Ground SS E06, terminalsfor E07, thermally- E08, enhanced E09, package F05, F06, F07, F08, F09, G05, G06, G07, G08, G09, H05, H06, H07, H08, H09, J05, J06, J07, J08, J09 V K10, G09, 79,82, GND Analog SSA C11, B12,J13, 86,89 ground H12, G12, terminal G11, F13,D12 E11, E10 COMBINEDPOWEROUTPUT V L13 N13 69 Internally-combined1.5-VmainandV poweroutputfor DD_15_COMB AUX externalbypasscapacitorfiltering.Suppliesallinternal1.5-V Feed Bypass circuitrypoweredbyV . through capacitors AUX Caution: Do not use this terminal to supply external power to otherdevices. V J13 K12 75 Internally-combined3.3-VmainandV poweroutputfor DD_33_COMB AUX externalbypasscapacitorfiltering.Suppliesallinternal3.3-V Feed Bypass circuitrypoweredbyV . through capacitors AUX Caution: Do not use this terminal to supply external power to otherdevices. V K11 K11 70 Internally-combined3.3-VmainandV poweroutputfor DD_33_COMBIO AUX externalbypasscapacitorfiltering.Suppliesallinternal3.3-V Feed Bypass input/outputcircuitrypoweredbyV . through capacitors AUX Caution: Do not use this terminal to supply external power to otherdevices. Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 9 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com PinFunctions ZGU ZAJ PNP I/O CELL CLAMP EXTERNAL SIGNAL BALL DESCRIPTION BALLNO. PINNO. TYPE TYPE RAIL PARTS NO. PCIEXPRESS CLKREQ D11 D11 91 0 LV VDD_33_ Clockrequest.Whenassertedlow,requests CMOS COMBIO upstreamdevicestartclockincaseswhereclock mayberemovedinL1. – Note: Since CLKREQ is an open-drain outputbuffer, a system sidepullupresistor isrequired. PERST H11 H11 77 I LV VDD_33_ PCIExpressresetinput.ThePERSTsignal CMOS COMBIO identifieswhenthesystempowerisstableand – generatesaninternalpoweronreset. Note: The PERST input buffer has hysteresis. REFCLK125_SEL B13 A13 95 I LV VDD_33 Referenceclockselect.Thisterminalselectsthe CMOS referenceclockinput. Pullupor 0=100-MHzdifferentialcommonreference pulldown clockused. resistor 1=125-MHzsingle-ended,referenceclock used. REFCLK+ C13 C13 93 DI HSDIFF VDD_33 Referenceclock.REFCLK+andREFCLK– IN comprisethedifferentialinputpairforthe100- – MHzsystemreferenceclock.Forasingle-ended, 125-MHzsystemreferenceclock,usethe REFCLK+input. REFCLK– C12 B13 94 DI HSDIFF VDD_33 Capacitor Referenceclock.REFCLK+andREFCLK– IN comprisethedifferentialinputpairforthe100- forVSSfor MHzsystemreferenceclock.Forasingle-ended, single- 125-MHzsystemreferenceclock,attacha endednode capacitorfromREFCLK–toVSS. REF0_PCIE K12 M13 71 I/O BIAS – Externalreferenceresistor+and–terminalsfor REF1_PCIE K13 L13 72 settingTXdrivercurrent.Anexternalresistance of14,532-ΩisconnectedbetweenREF0_PCIE External andREF1_PCIEterminals.Toeliminatetheneed resistor foracustomresistor,twoseriesresistorsare recommended:a14.3-kΩ,1%resistoranda232- Ω,1%resistor. RXP E13 E13 87 DI HSDIFF VSS High-speedreceivepair.RXPandRXNcomprise RXN E12 D13 88 IN – thedifferentialreceivepairforthesinglePCI Expresslanesupported. TXP G13 H13 80 DO HSDIFF VDD_15 Series High-speedtransmitpair.TXPandTXNcomprise TXN G12 G13 81 OUT thedifferentialtransmitpairforthesinglePCI capacitor Expresslanesupported. WAKE M13 L12 68 O LV VDD_33_ Wakeisanactivelowsignalthatisdrivenlowto CMOS COMBIO reactivatethePCIExpresslinkhierarchy’smain powerrailsandreferenceclocks. – Note:SinceWAKEisanopen-drainoutput buffer, a system side pullup resistor is required. 10 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 PinFunctions(continued) ZGU ZAJ PNP I/O CELL CLAMP EXTERNAL SIGNAL BALL DESCRIPTION BALLNO. PINNO. TYPE TYPE RAIL PARTS NO. PCISYSTEM AD31 N05 N05 44 I/O PCIBus PCIR PCIaddressdatalines AD30 N04 L05 43 AD29 L05 M05 42 AD28 M05 N04 41 AD27 N03 N03 40 AD26 M04 L04 39 AD25 N02 M04 38 AD24 M03 N02 37 AD23 L04 L03 35 AD22 M02 M02 34 AD21 L03 N01 32 AD20 M01 L02 31 AD19 L02 K02 30 AD18 L01 M01 29 AD17 K02 K03 28 AD16 K01 L01 26 – AD15 E01 F02 12 AD14 E02 E03 11 AD13 E03 E01 10 AD12 D01 E02 9 AD11 D02 D01 8 AD10 C01 C01 6 AD9 C02 D02 5 AD8 D03 B01 4 AD7 C03 A01 1 AD6 B02 B03 128 AD5 C04 C03 127 AD4 A02 A02 125 AD3 B03 A03 124 AD2 B04 C04 123 AD1 A03 C05 122 AD0 C05 B04 121 C/BE[3] N01 M03 36 I/O PCIBus PCIR PCIcommandbyteenables C/BE[2] J03 K01 25 – C/BE[1] F02 F03 14 C/BE[0] B01 C02 3 CLK F03 F01 13 I PCIBus PCIR PCIclockinput.ThisistheclockinputtothePCI – buscore. CLKOUT0 B05 B05 120 O PCIBus PCIR PCIclockoutputs.Theseclockoutputsareused CLKOUT1 B06 B06 117 toclockthePCIbus.IfthebridgePCIbusclock CLKOUT2 A07 B07 114 outputsareused,thenCLKOUT6mustbe CLKOUT3 B07 A07 112 – connectedtotheCLKinput. CLKOUT4 A09 A08 107 CLKOUT5 A10 A10 104 CLKOUT6 B11 C10 99 DEVSEL H02 H02 20 I/O PCIBus PCIR Pullup PCIdeviceselect resistorper PCIspec FRAME J02 J01 24 I/O PCIBus PCIR Pullup PCIframe resistorper PCIspec GNT5 B10 B11 101 O PCIBus PCIR PCIgrantoutputs.Thesesignalsareusedfor GNT4 A11 B10 103 arbitrationwhenthePCIbusisthesecondary GNT3 B09 B09 106 busandanexternalarbiterisnotused.GNT0is – GNT2 B08 B08 109 usedastheREQforthebridgewhenanexternal GNT1 C06 A06 115 arbiterisused. GNT0 A05 A05 118 INTA M06 N06 47 I PCIBus PCIR PCIinterruptsA–D.Thesesignalsareinterrupt Pullup INTB N06 L06 48 inputstothebridgeonthesecondaryPCIbus. resistorper INTC M07 M07 49 PCIspec INTD L07 N07 50 IRDY J01 H03 23 I/O PCIBus PCIR Pullup PCIinitiatorready resistorper PCIspec LOCK M08 N08 54 I/O PCIBus PCIR ThisterminalfunctionsasPCILOCK Pullup Note: In lock mode, an external pullup resistorper PCIspec resistor is required to prevent the LOCK signalfromfloating. Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 11 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com PinFunctions(continued) ZGU ZAJ PNP I/O CELL CLAMP EXTERNAL SIGNAL BALL DESCRIPTION BALLNO. PINNO. TYPE TYPE RAIL PARTS NO. M66EN L06 M06 45 I PCIBus PCIR 66-MHzmodeenable 0 = Secondary PCI bus and clock outputs Pullup operate at 33 MHz. If PCLK66_SEL is low resistorper thenthefrequencywillbe25MHz. PCIspec 1 = Secondary PCI bus and clock outputs operate at 66 MHz. If PCLK66_SEL is low thenthefrequencywillbe50MHz. PAR F01 G01 15 I/O PCIBus PCIR – PCIbusparity PERR G02 G03 17 I/O PCIBus PCIR Pullup PCIparityerror resistorper PCIspec PME L12 M12 67 I LV VDD_33_ PullupresistorperPCIspecPCIpower CMOS COMBIO Pullup managementevent.Thisterminalmaybeusedto resistorper detectPMEeventsfromaPCIdeviceonthe PCIspec secondarybus. Note:ThePMEinputbufferhashysteresis. REQ5 A12 C09 102 I PCIBus PCIR PCIrequestinputs.Thesesignalsareusedfor REQ4 C09 A09 105 Ifunused,a arbitrationonthesecondaryPCIbuswhenan REQ3 C08 C08 108 weakpullup externalarbiterisnotused.REQ0isusedasthe REQ2 A08 C07 110 resistorper GNTforthebridgewhenanexternalarbiteris REQ1 A06 C06 116 PCIspec used. REQ0 A04 A04 119 PRST N07 L07 51 O PCIBus PCIR PCIreset.Thisterminalisanoutputtothe – secondaryPCIbus. SERR G03 G02 16 I/O PCIBus PCIR Pullup PCIsystemerror resistorper PCIspec STOP G01 H01 18 I/O PCIBus PCIR Pullup PCIstop resistorper PCIspec TRDY H01 J02 22 I/O PCIBus PCIR Pullup PCItargetready resistorper PCIspec JTAG JTAG_TCK M12 N12 65 I LV VDD_33 JTAGtestclockinput.Thissignalprovidesthe CMOS clockfortheinternalTAPcontroller. Note: This terminal has an internal active Optional pullup resistor. The pullup is active at all pullup times. resistor Note: This terminal should be tied to ground or pulled low if JTAG is not required. JTAG_TDI N12 L10 63 I LV VDD_33 JTAGtestdatainput.Serialtestinstructionsand CMOS dataarereceivedonthisterminal. Optional Note: This terminal has an internal active pullup pullup resistor. The pullup is active at all resistor times. Note: This terminal can be left unconnectedifJTAGisnotrequired. JTAG_TDO M11 N11 61 O LV VDD_33 JTAGtestdataoutput.Thisterminaltheserial CMOS outputfortestinstructionsanddata. – Note: This terminal can be left unconnectedifJTAGisnotrequired. JTAG_TMS L10 L11 64 I LV VDD_33 JTAGtestmodeselect.Thesignalreceivedat CMOS JTAG_TMSisdecodedbytheinternalTAP controllertocontroltestoperations. Optional Note: This terminal has an internal active pullup pullup resistor. The pullup is active at all resistor times. Note: This terminal can be left unconnectedifJTAGisnotrequired. 12 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 PinFunctions(continued) ZGU ZAJ PNP I/O CELL CLAMP EXTERNAL SIGNAL BALL DESCRIPTION BALLNO. PINNO. TYPE TYPE RAIL PARTS NO. JTAG_TRST L09 L09 60 I LV VDD_33 JTAGtestreset.ThisterminalprovidesOptional CMOS forasynchronousinitializationoftheTAP controller. Optional Note: This terminal has an internal active pullup pullup resistor. The pullup is active at all resistor times. Note: This terminal should be tied to ground or pulled low if JTAG is not required. MiscellaneousPins ZGU ZAJ PNP I/O CELL CLAMP EXTERNAL SIGNAL BALL BALL PIN DESCRIPTION TYPE TYPE RAIL PARTS NO. NO. NO. CLKRUN_ A13 C11 96 I LV V Optional Clockrunenable DD_33 EN CMOS pullup/ 0=Clockrunsupportdisabled pulldown resistor 1=Clockrunsupportenabled EXT_ARB_EN C10 A12 97 I LV VDD_33 Optional Externalarbiterenable CMOS pullup/ pulldown 0=Internalarbiterenabled resistor 1=Externalarbiterenabled GPIO0// N09 N09 55 I/O LV V DD_33 General-purpose I/O 0/clock run. This CLKRUN CMOS terminal functions as a GPIO controlled by bit 0 (GPIO0_DIR) in the GPIO control register (see GPIO Control Register) or the clock run terminal. This terminalisusedasclockruninputwhen Optionalpullup thebridgeisplacedinclockrunmode. resistor Note: In clock run mode, an external pullupresistor is requiredtopreventthe CLKRUNsignalfromfloating. Note: This terminal has an internal active pullup resistor. The pullup is only active when reset is asserted or when theGPIOisconfiguredasaninput. GPIO1//PWR_ M09 M09 56 I/O LV V DD_33 General-purpose I/O 1/power override. OVRD CMOS This terminal functions as a GPIO controlled by bit 1 (GPIO1_DIR) in the GPIOcontrolregister(seeGPIOControl Register) or the power override output terminal. GPIO1 becomes PWR_OVRD – whenbits22:20(POWER_OVRD)inthe general control register are set to 001b or011b(seeGeneralControlRegister). Note: This terminal has an internal active pullup resistor. The pullup is only active when reset is asserted or when theGPIOisconfiguredasaninput. GPIO2 N10 N10 57 I/O LV V DD_33 General-purpose I/O 2. This terminal CMOS functions as a GPIO controlled by bit 2 (GPIO2_DIR) in the GPIO control register(seeGPIOControlRegister). – Note: This terminal has an internal active pullup resistor. The pullup is only active when reset is asserted or when theGPIOisconfiguredasaninput. Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 13 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com MiscellaneousPins(continued) ZGU ZAJ PNP I/O CELL CLAMP EXTERNAL SIGNAL BALL BALL PIN DESCRIPTION TYPE TYPE RAIL PARTS NO. NO. NO. GPIO3//SDA N11 L08 58 I/O LV V DD_33 GPIO3 or serial-bus data. This terminal CMOS functions as serial-bus data if a pullup resistorisdetectedonSCLorwhenthe SBDETECT bit is set in the Serial Bus ControlandStatusRegister(seeSerial- Optionalpullup Bus Control and Status Register). If no resistor pullup is detected then this terminal functionsasGPIO3. Note: In serial-bus mode, an external pullupresistor is requiredtopreventthe SDAsignalfromfloating. GPIO4//SCL M10 M10 59 I/O LV V DD_33 GPIO4orserial-busclock.Thisterminal CMOS functions as serial-bus clock if a pullup resistorisdetectedonSCLorwhenthe SBDETECT bit is set in the Serial Bus ControlandStatusRegister(seeSerial- Bus Control and Status Register). If no pullup is detected then this terminal Optionalpullup functionsasGPIO4. resistor Note: In serial-bus mode, an external pullupresistor is requiredtopreventthe SCLsignalfromfloating. Note: This terminal has an internal active pullup resistor. The pullup is only active when reset is asserted or when theGPIOisconfiguredasaninput. GRST N13 M11 66 I LV V DD_33 Global reset input. Asynchronously CMOS _COMBIO resetsalllogicindevice,includingsticky bits and power management state – machines. Note: The GRST input buffer has both hysteresis and an internal active pullup. Thepullupisactiveatalltimes. PCLK66_ B12 A11 98 I LV V DD_33 PCI clock select. This terminal SEL CMOS determines the default PCI clock frequency driven out the CLKOUTx terminals. Optional 0=50MHzPCIClock pulldown 1=66MHzPCIClock resistor Note: This terminal has an internal active pullup resistor. This pullup is activeatalltimes. Note: M66EN terminal also has an affectofPCIclockfrequency. SERIRQ N08 M08 52 I/O PCI PCIR Serial IRQ interface. This terminal Bus Pullupor functions as a serial IRQ interface if a pulldown pullup is detected when PERST is resistor deasserted. If a pulldown is detected, thentheserialIRQinterfaceisdisabled. VREG_ D12 E11 90 I LV V 3.3-Vvoltageregulatorpowerdown.This DD_33 PD33 CMOS Pulldown terminalshouldalwaysbetieddirectlyto _COMBIO resistor groundoranoptionalpulldownresistor canbeused. 14 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 6 Specifications 6.1 Absolute Maximum Ratings overoperatingtemperaturerange(unlessotherwisenoted)(1) MIN MAX UNIT V –0.5 3.6 V DD_33 Supplyvoltagerange V –0.5 1.65 V DD_15 PCI –0.5 PCIR+0.5 V PCIExpress(RX) –0.6 0.6 V V Inputvoltagerange PCIExpressREFCLK(single-ended) –0.5 V +0.5 V I DD_33 PCIExpressREFCLK(differential) –0.5 V +0.5 V DD_15 Miscellaneous3.3-VIO –0.5 V +0.5 V DD_33 PCI –0.5 V +0.5 V DD_33 V Outputvoltagerange PCIExpress(TX) –0.55 V +0. V O DD_15 Miscellaneous3.3-VIO –0.5 V +0.5 V DD_33 Inputclampcurrent,(V <0orV >VDD)(2) ±20 mA I I Outputclampcurrent,(V <0orV >VDD)(3) ±20 mA O O (1) StressesbeyondthoselistedunderAbsoluteMaximumRatingsmaycausepermanentdamagetothedevice.Thesearestressratings only,andfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderRecommendedOperating Conditionsisnotimplied.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability. (2) Appliesforexternalinputandbidirectionalbuffers.V <0orV >V orV >PCIR. I I DD I (3) Appliesforexternalinputandbidirectionalbuffers.V <0orV >V orV >PCIR. O O DD O 6.2 Handling Ratings MIN MAX UNIT T Storagetemperaturerange –65 150 °C stg V (1) HumanbodymodelESDrating(R=1.5K,C=100pF) 2 kV ESD-HBM V (1) ChargeddevicemodelESDrating(200pF) 500 V ESD-CDM (1) Electrostaticdischarge(ESD)tomeasuredevicesensitivityandimmunitytodamagecausedbyassemblylineelectrostaticdischargesin tothedevice. 6.3 Recommended Operating Conditions OPERATION MIN NOM MAX UNIT V DD_15 Supplyvoltage 1.5V 1.35 1.5 1.65 V V DDA_15 V DD_33 V Supplyvoltage 3.3V 3 3.3 3.6 V DDA_33 V DDA_33_AUX 3.3V 3 3.3 3.6 PCIR PCIbusclampingrailvoltage(with1kΩresistor) V 5V 4.75 5 5.25 Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 15 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com 6.4 Thermal Information(1) PARAMETER TESTCONDITIONS MIN TYP MAX UNIT PNP Low-KJEDECtestboard,1s(singlesignallayer),noair 50.8 Junction-to-free-airthermal flow θ °C/W JA resistance High-KJEDECtestboard,2s2p(doublesignallayer, 24.9 doubleburiedpowerplane),noairflow θ Junction-to-casethermalresistance Cucoldplatemeasurementprocess 18.9 °C/W JC Junction-to-boardthermal θ EIA/JESD51-8 14.6 °C/W JB resistance ψ Junction-to-topofpackage EIA/JESD51-2 0.26 °C/W JT ψ Junction-to-board EIA/JESD51-6 7.93 °C/W JB Operatingambienttemperature XIO2001PNP 0 70 T °C A range XIO2001IPNP –40 85 XIO2001PNP 0 105 T Virtualjunctiontemperature °C J XIO2001IPNP –40 105 ZAJ Low-KJEDECtestboard,1s(singlesignallayer),noair 82 Junction-to-free-airthermal flow θ °C/W JA resistance High-KJEDECtestboard,2s2p(doublesignallayer, 58.8 doubleburiedpowerplane),noairflow θ Junction-to-casethermalresistance Cucoldplatemeasurementprocess 19 °C/W JC Junction-to-boardthermal θ EIA/JESD51-8 32 °C/W JB resistance ψ Junction-to-topofpackage EIA/JESD51-2 0.5 °C/W JT ψ Junction-to-board EIA/JESD51-6 30 °C/W JB Operatingambienttemperature XIO2001ZGU 0 70 T °C A range XIO2001IZGU –40 85 XIO2001ZGU 0 105 T Virtualjunctiontemperature °C J XIO2001IZGU –40 105 ZGU Low-KJEDECtestboard,1s(singlesignallayer),noair 85 Junction-to-free-airthermal flow θ °C/W JA resistance High-KJEDECtestboard,2s2p(doublesignallayer, 48.3 doubleburiedpowerplane),noairflow θ Junction-to-casethermalresistance Cucoldplatemeasurementprocess 8.5 °C/W JC Junction-to-boardthermal θ EIA/JESD51-8 25.4 °C/W JB resistance ψ Junction-to-topofpackage EIA/JESD51-2 0.5 °C/W JT ψ Junction-to-board EIA/JESD51-6 24 °C/W JB Operatingambienttemperature XIO2001ZGU 0 70 T °C A range XIO2001IZGU –40 85 XIO2001ZGU 0 105 T Virtualjunctiontemperature °C J XIO2001IZGU –40 105 (1) Formoredetails,refertoTIapplicationnoteICPackageThermalMetrics(SPRA953). 16 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 6.5 Nominal Power Consumption DEVICES POWERSTATE(1) VOLTS AMPERES WATTS 1.5 0.147 0.221 NodownstreamPCIdevices D0idle 3.3 0.062 0.205 TOTALS: 0.209 0.426 1.5 0.148 0.222 OnedownstreamPCIdevice D0idle 3.3 0.077 0.254 TOTALS: 0.225 0.476 1.5 0.157 0.236 OnedownstreamPCIdevice D0active 3.3 0.165 0.545 TOTALS: 0.322 0.780 1.65 0.168 0.277 Onedownstream(maxvoltage) D0active 3.6 0.188 0.677 TOTALS: 0.356 0.954 (1) D0idlepowerstate:DownstreamPCIdeviceisinPCIstateD0.Downstreamdevicedriverisloaded.Downstreamdeviceisnotactively transferringdata. D0activepowerstate:DownstreamPCIdeviceisinPCIstateD0.Downstreamdevicedriverisloaded.Downstreamdeviceisacitvely transferringdata(worstcasescenario). 6.6 PCI Express Differential Transmitter Output Ranges PARAMETER TERMINALS MIN NOM MAX UNIT COMMENTS UI(1) EachUIis400ps±300ppm.UIdoesnotaccountforSSC TXP,TXN 399.88 400 400.12 ps Unitinterval dictatedvariations. VDTifXfe-DrIeFnF-tPiaPlpeak-to-peakoutputvoltage TXP,TXN 0.8 1.2 V VTX-DIFF-PP=2*|VTXP–VTXN| VTX-DIFF-PP-LOW Low-powerdifferentialpeak-to-peakTX TXP,TXN 0.4 1.2 V VTX-DIFF-PP=2*|VTXP–VTXN| voltageswing VTXTX-dDeE--eRAmTpIOh-3a.5sdisBlevelratio TXP,TXN 3 4 dB TfohllioswisintghebirtastaioftoefrtahetraVnTsXi-tDioIFnF-dPPivoidfetdhebysethcoenVdTXa-nDdIFF-PPof thefirstbitafteratransition. TMTiXn-iEmYuEm(2)T(3X)(e4)yewidth TXP,TXN 0.75 UI DoesnotincludeSSCorRefCLKjitter.IncludesRjat10–12. TTX-EYE-MEDIAN-to-MAX-JITTER(2) Measureddifferentiallyatzerocrossingpointsafter Maximumtimebetweenthejittermedian TXP,TXN 0.125 UI applyingthe2.5GT/sclockrecoveryfunction. andmaximumdeviationfromthemedian TTX-RISE-FALL(2) TXP,TXN 0.125 UI Measureddifferentiallyfrom20%to80%ofswing. TXoutputrise/falltime BWTX-PLL(5) TXP,TXN 22 MHz SecondorderPLLjittertransferboundingfunction. MaximumTXPLLbandwidth BWTX-PLL-LO-3DB(5)(6) TXP,TXN 1.5 MHz SecondorderPLLjittertransferboundingfunction. MinimumTXPLLbandwidth RLTX-DIFF TxpackageplusSidifferentialreturn TXP,TXN 10 dB loss RLTX-CM TxpackageplusSicommonmodereturn TXP,TXN 6 dB Measuredover0.05–1.25GHzrange loss ZTX-DIFF_DC TXP,TXN 80 120 Ω Lowimpedancedefinedduringsignaling. DCdifferentialTXimpedance (1) SCCpermitsa0,–5000ppmmodulationoftheclockfrequencyatamodulationratenottoexceed33kHz. (2) Measurementsat2.5GT/srequireascopewithatleast6.2GHzbandwidth.2.5GT/smaybemeasuredwithin200milsofTxdevice's pins,althoughdeconvolutionisrecommended. (3) Transmitterjitterismeasuredbydrivingthetransmitterundertestwithalowjitter"ideal"clockandconnectingtheDUTtoareference board. (4) TransmitterrawjitterdatamustbeconvolvedwithafilteringfunctionthatrepresentstheworstcaseCDRtrackingBW.Afterthe convolutionprocesshasbeenapplied,thecenteroftheresultingeyemustbedeterminedandusedasareferencepointforobtaining eyevoltageandmargins. (5) TheTxPLLBandwidthmustliebetweentheminandmaxrangesgivenintheabovetable.PLLpeakingmustliebelowthevaluelisted above.Note:thePLLB/Wextendsfromzerouptothevalue(s)specifiedintheabovetable. (6) AsinglecombinationofPLLBWandpeakingisspecifiedfor2.5GT/simplemenations. Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 17 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com PCI Express Differential Transmitter Output Ranges (continued) PARAMETER TERMINALS MIN NOM MAX UNIT COMMENTS VTX-CM-AC-P(7) TXP,TXN 20 mV TXACcommonmodevoltage ITX-SHORT TXP,TXN 90 mA Thetotalcurrenttransmittercansupplywhenshortedto Transmittershort-circuitcurrentlimit ground. VTX-DC-CM TXP,TXN 0 3.6 V TheallowedDCcommon-modevoltageatthetransmitter TransmitterDCcommon-modevoltage pinsunderanyconditions. |VTX-CM-DC–VTX-CM-Idle-DC|≤100mV VATbXs-oClMu-tDeC-dAeClTtaIVEo-fIDDLEC-DcEoLTmAmonmode TXP,TXN 0 100 mV VTX-CM-DC=DC(avg)of|VTXP+VTXN|/2[duringL0] voltageduringL0andelectricalidle VTX-CM-Idle-DC=DC(avg)of|VTXP+VTXN|/2[duringelectrical idle] VTX-CM-DC-LINE-DELTA |VTXP-CM-DC–VTXN-CM-DC|≤25mVwhen AbsolutedeltaofDCcommonmode TXP,TXN 0 25 mV VTXP-CM-DC=DC(avg)of|VTXP|[duringL0] voltagebetweenPandN VTXN-CM-DC=DC(avg)of|VTXN|[duringL0] VTX-IDLE-DIFF-AC-p Electricalidledifferentialpeakoutput TXP,TXN 0 20 mV VTX-IDLE-DIFFp=|VTXP-Idle–VTXN-Idle|≤20mV voltage VTX-RCV-DETECT Thetotalamountofvoltagechangethatatransmittercan Theamountofvoltagechangeallowed TXP,TXN 600 mV applytosensewhetheralowimpedancereceiveris duringreceiverdetection present. TTX-IDLE-MIN TXP,TXN 20 ns Minimumtimeatransmittermustbeinelectricalidle. Minimumtimespentinelectricalidle AftersendingtherequirednumberofEIOSs,the TTX-IDLE-SET-TO-IDLE transmittermustmeetallelectricalidlespecifications Maximumtimetotransitiontoavalid TXP,TXN 8 ns withinthistime.Thisismeasuredfromtheendofthelast electricalidleaftersendinganEIOS EIOStothetransmitterinelectricalidle. TTX-IDLE-TO-DIFF-DATA Maximumtimetotransistiontovaliddiffsignalingafter Maximumtimetotransitiontoavaliddiff TXP,TXN 8 ns leavingelectricalidle.Thisisconsideredadebouncetime signalingafterleavingelectricalidle totheTx. AlltransmittersshallbeACcoupled.TheACcouplingis CTX TXP,TXN 75 200 nF requiredeitherwithinthemediaorwithinthetransmitting ACcouplingcapacitor componentitself. (7) Measurementismadeoveratleast10UI. 6.7 PCI Express Differential Receiver Input Ranges PARAMETER TERMINALS MIN NOM MAX UNIT COMMENTS UI(1) EachUIis400ps±300ppm.UIdoesnotaccountfor RXP,RXN 399.88 400.12 ps Unitinterval SSCdictatedvariations. VDRifXfe-DreIFnF-tPiaPl-CinCp(2u)tpeak-to-peakvoltage RXP,RXN 0.175 1.200 V VRX-DIFFp-p=2*|VRXP–VRXN| TMRinX-iEmYuEm(2)r(e3)ceivereyewidth RXP,RXN 0.4 UI TthhaetcmaanxbimeutmoleirnateterdcobnyntehcetmreecdeiiavearnisddtrearnivsemditatesrTjiRttXe-r MAX-JITTER=1–TRX-EYE=0.6UI Jitterisdefinedasthemeasurementvariationofthe crossingpoints(VRX-DIFFp-p=0V)inrelationto TRX-EYE-MEDIAN-to-MAX-JITTER(2)(3) recoveredTXUI.ArecoveredTXUIiscalculatedover Maximumtimebetweenthejittermedian RXP,RXN 0.3 UI 3500consecutiveUIsofsampledata.Jitteris andmaximumdeviationfromthemedian measuredusingalledgesofthe250consecutiveUIs inthecenterofthe3500UIsusedforcalculatingthe TXUI. BWRX-PLL-HI(4) RXP,RXN 22 MHz SecondorderPLLjittertransferboundingfunction. MaximumRxPLLbandwidth BWRX-PLL-LO-3DB(4) RXP,RXN 1.5 MHz SecondorderPLLjittertransferboundingfunction. MinimumRxPLLfor3dBpeaking (1) Notestloadisnecessarilyassociatedwiththisvalue. (2) Specifiedatthemeasurementpointandmeasuredoverany250consecutiveUIs.AtestloadmustbeusedastheRXdevicewhen takingmeasurements.IftheclockstotheRXandTXarenotderivedfromthesamereferenceclock,thentheTXUIrecoveredfrom 3500consecutiveUIsisusedasareferencefortheeyediagram. (3) ATRX-EYE=0.40UIprovidesforatotalsumof0.60UIdeterministicandrandomjitterbudgetforthetransmitterandinterconnect collectedany250consecutiveUIs.TheTRX-EYE-MEDIAN-to-MAX-JITTERspecificationensuresajitterdistributioninwhichthe medianandthemaximumdeviationfromthemedianislessthanhalfofthetotalUIjitterbudgetcollectedoverany250consecutiveTX UIs.Itmustbenotedthatthemedianisnotthesameasthemean.Thejittermediandescribesthepointintimewherethenumberof jitterpointsoneithersideisapproximatelyequalasopposedtotheaveragedtimevalue.IftheclockstotheRXandTXarenotderived fromthesamereferenceclock,thentheTXUIrecoveredfrom3500consecutiveUIsmustbeusedasthereferencefortheeye diagram. (4) AsinglePLLbandwidthandpeakingvalueof1.5to22MHzand3dBaredefined. 18 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 PCI Express Differential Receiver Input Ranges (continued) PARAMETER TERMINALS MIN NOM MAX UNIT COMMENTS VRX-CM-AC-P(2) RXP,RXN 150 mV VRX-CM-AC-P=RMS(|VRXP+VRXN|/2–VRX-CM-DC) ACpeakcommonmodeinputvoltage VRX-CM-DC=DC(avg)of|VRXP+VRXN|/2. RLRX-DIFF(5) RXP,RXN 10 dB Measuredover50MHzto1.25GHzwiththePandN Differentialreturnloss linesbiasedat+300mVand–300mV,respectively. RLRX-CM(5) RXP,RXN 6 dB Measuredover50MHzto1.25GHzwiththePandN Commonmodereturnloss linesbiasedat+300mVand–300mV,respectively. ZRX-DIFF-DC(6) RXP,RXN 80 120 Ω RXdcdifferentialmodeimpedance DCdifferentialinputimpedance ZRX-DC(5)(6) RXP,RXN 40 60 Ω RequiredRXPaswellasRXNdcimpedance(50Ω DCinputimpedance ±20%tolerance). ZRX-HIGH-IMP-DC-POS(7) RxDCCMimpedancewiththeRxterminationsnot DCinputCMinputimpedanceforV>0 RXP,RXN 50 kΩ powered,measuredovertherange0to200mVwith duringresetorpowerdown respecttoground. ZRX-HIGH-IMP-DC-NEG(7) RxDCCMimpedancewiththeRxterminationsnot DCinputCMinputimpedanceforV>0 RXP,RXN 1 kΩ powered,measuredovertherange0to200mVwith duringresetorpowerdown respecttoground. VRX-IDLE-DET-DIFFp-p RXP,RXN 65 175 mV VRX-IDLE-DET-DIFFp-p=2*|VRXP–VRXN|measuredatthe Electricalidledetectthreshold receiverpackageterminals TURnXe-IxDpLeE-cDtEeTd-DeIFleF-cEtNriTcEaRl-TidIMleEenterdetect RXP,RXN 10 ms ADEnT-uDnIFeFxp-ppe)cmteudstebleecrtreiccaolgindilzee(dVnRoX-DloIFnFgp-epr<thVaRnX-TIDRLXE--IDLE- thresholdintegrationtime DET-DIFF-ENTER-TIMEtosignalanunexpectedidle condition. (5) Thereceiverinputimpedanceresultsinadifferentialreturnlossgreaterthanorequalto15dBwiththePlinebiasedto300mVandthe Nlinebiasedto.300mVandacommonmodereturnlossgreaterthanorequalto6dB(nobiasrequired)overafrequencyrangeof50 MHzto1.25GHz.Thisinputimpedancerequirementappliestoallvalidinputlevels.Thereferenceimpedanceforreturnloss measurementsforis50.togroundforboththePandNline(i.e.,asmeasuredbyaVectorNetworkAnalyzerwith50-.probes).The seriescapacitorsCTXisoptionalforthereturnlossmeasurement. (6) Impedanceduringalllinktrainingstatusstatemachine(LTSSM)states.WhentransitioningfromaPCIExpressresettothedetectstate (theinitialstateoftheLTSSM)thereisa5-mstransitiontimebeforereceiverterminationvaluesmustbemetontheunconfiguredlane ofaport. (7) Z andZ aredefinedrespectivelyfornegativeandpostivevoltagesattheinputofthereceiver. RX-HIGH-IMP-DC-NEG RX-HIGH-IMP-DC-POS 6.8 PCI Express Differential Reference Clock Input Ranges(1) PARAMETER TERMINALS MIN NOM MAX UNIT COMMENTS fIN-DIFF REFCLK+ 100 MHz Theinputfrequencyis100MHz+300ppmand–2800 Differentialinputfrequency REFCLK– ppmincludingSSC-dictatedvariations. fIN-SE REFCLK+ Theinputfrequencyis125MHz+300ppmand–300 Single-endedinput 125 MHz ppm. frequency VRX-DIFFp-p REFCLK+ Differentialinputpeak-to- REFCLK– 0.175 1.2 V VRX-DIFFp-p=2*|VREFCLK+–VREFCLK-| peakvoltage REFCLK+ Single-ended,referenceclockmodehigh-levelinput VIH-SE 0.7VDDA_33 VDDA_33 V voltage REFCLK+ Single-ended,referenceclockmodelow-levelinput VIL-SE 0 0.3VDDA_33 V voltage VRX-CM-ACp REFCLK+ VRX-CM-ACp=RMS(|VREFCLK++VREFCLK-|/2VRX-CM-DC) ACpeakcommonmode REFCLK– 140 mV VRX-CM-DC=DC(avg)of inputvoltage |VREFCLK++VREFCLK-|/2 REFCLK+ Differentialandsingle-endedwaveforminputduty Dutycycle 40% 60% REFCLK– cycle ZC-DC REFCLK+ 40 60 Ω REFCLK±dcdifferentialmodeimpedance ClocksourceDCimpedance REFCLK– ZRX-DC REFCLK+ 20 kΩ REFCLK+dcsingle-endedmodeimpedance DCinputimpedance REFCLK– (1) TheXIO2001iscompliantwiththedefinedsystemjittermodelsforaPCI-ExpressreferenceclockandassociatedTX/RXlink.Any usageoftheXIO2001inasystemconfigurationthatdoesnotconformtothedefinedsystemjittermodelsrequiresthesystemdesigner tovalidatethesystemjitterbudgets. Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 19 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com 6.9 PCI Bus Electrical Characteristics overrecommendedoperatingconditions(1) PARAMETER OPERATION TESTCONDITIONS MIN MAX UNIT PCIR=3.3V 0.5×V PCIR+0.5 V High-levelinputvoltage(2) DD_33 V IH PCIR=5V 2.0 PCIR+0.5 PCIR=3.3V –0.5 0.3×V V Low-levelinputvoltage(2) DD_33 V IL PCIR=5V –0.5 0.8 V Inputvoltage 0 PCIR V I V Outputvoltage(3) 0 V V O DD_33 t Inputtransitiontime(t andt ) 1 4 ns t rise fall PCIR=3.3V I =–500μA 0.9×V OH DD_33 V High-leveloutputvoltage V OH PCIR=5V I =–2mA 2.4 OH PCIR=3.3V I =1500μA 0.1×V OH DD_33 V Low-leveloutputvoltage V OL PCIR=5V I =6mA 0.55 OH PCIR=3.3V ±10 IOZ High-impedance,outputcurrent(3) μA PCIR=5V ±70 PCIR=3.3V ±10 I Inputcurrent μA I PCIR=5V ±70 (1) ThistableappliestoCLK,CLKOUT6:0,AD31:0,C/BE[3:0],DEVSEL,FRAME,GNT5:0,INTD:A,IRDY,PAR,PERR,REQ5:0,PRST, SERR,STOP,TRDY,SERIRQ,M66EN,andLOCKterminals. (2) Appliestoexternalinputsandbidirectionalbuffers. (3) Appliestoexternaloutputsandbidirectionalbuffers. 6.10 3.3-V I/O Electrical Characteristics overrecommendedoperatingconditions(1) PARAMETER OPERATION TESTCONDITIONS MIN MAX UNIT V High-levelinputvoltage(2) V 0.7V V V IH DD_33 DD_33 DD_33 V VILLow-levelinputvoltage (2) V 0 0.3V V IL DD_33 DD_33 V Inputvoltage 0 V V I DD_33 V Outputvoltage(3) 0 V V O DD_33 t Inputtransitiontime(t andt ) 0 25 ns t rise fall V Inputhysteresis(4) 0.13V V hys DD_33 V High-leveloutputvoltage V I =–4mA 0.8V V OH DD_33 OH DD_33 V Low-leveloutputvoltage V I =4mA 0.22V V OL DD_33 OL DD_33 I High-impedance,outputcurrent(3) V V =0toV ±20 μA OZ DD_33 I DD_33 I High-impedance,outputcurrentwithinternal V V =0toV ±100 μA OZP DD_33 I DD_33 pulluporpulldownresistor(1) I Inputcurrent(5) V V =0toV ±1 μA I DD_33 I DD_33 (1) AppliestoGRST(pullup),EXT_ARB_EN(pulldown),CLKRUN_EN(pulldown),andmostGPIO(pullup). (2) Appliestoexternalinputsandbidirectionalbuffers. (3) Appliestoexternaloutputsandbidirectionalbuffers. (4) AppliestoPERST,GRST,andPME. (5) Appliestoexternalinputbuffers. 20 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 6.11 PCI Bus Timing Requirements overrecommendedoperatingconditions(1) TEST 33MHz 66MHz PARAMETER UNIT CONDITION MIN MAX MIN MAX C =50pF 11 L CLKtosharedsignalvalidpropagationdelaytime C =30pF 6 L t ns pd C =50pF 2 L CLKtosharedsignalinvalidpropagationdelaytime C =30pF 1 L C =50pF 2 L t tEnabletime,high-impedance-to-activedelaytimefromCLK ns ON C =30pF 1 L C =50pF 28 L t Disabletime,active-to-high-impedancedelaytimefromCLK ns OFF C =30pF 14 L t SetuptimeonsharedsignalsbeforeCLKvalid(risingedge) 7 3 ns su t HoldtimeonsharedsignalsafterCLKvalid(risingedge) 0 0 ns h (1) ThePCIsharedsignalsareAD31:0,C/BE[3:0],FRAME,TRDY,IRDY,STOP,IDSEL,DEVSEL,LOCK,SERIRQ,PAR,PERR,SERR, andCLKRUN. 6.12 Power-Up/-Down Sequencing The bridge contains both 1.5-V and 3.3-V power terminals. The following power-up and power-down sequences describehowpowerisappliedtotheseterminals. In addition, the bridge has three resets: PERST, GRST and an internal power-on reset. These resets are fully described in Bridge Reset Features. The following power-up and power-down sequences describe how PERST isappliedtothebridge. The application of the PCI Express reference clock (REFCLK) is important to the power-up/-down sequence and isincludedinthefollowingpower-upandpower-downdescriptions. 6.12.1 Power-UpSequence 1. AssertGRSTandPERSTtothedevice. 2. Apply1.5-Vand3.3-Vvoltages. 3. DeassertGRST. 4. ApplyastablePCIExpressreferenceclock. 5. TomeetPCIExpressspecificationrequirements,PERSTcannotbedeasserteduntilthefollowingtwodelayrequirementsaresatisfied: – Waitaminimumof100μsafterapplyingastablePCIExpressreferenceclock.The100-μslimitsatisfiestherequirementforstable deviceclocksbythedeassertionofPERST. – Waitaminimumof100msafterapplyingpower.The100-mslimitsatisfiestherequirementforstablepowerbythedeassertionof PERST. Seethepower-upsequencingdiagraminFigure4. Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 21 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com Power-Up/-Down Sequencing (continued) Figure4. Power-UpSequence 22 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 Power-Up/-Down Sequencing (continued) 6.12.2 Power-DownSequence 1. AssertPERSTtothedevice. 2. Removethereferenceclock. 3. RemovePCIRclampvoltage. 4. Remove3.3-Vand1.5-Vvoltages. See the power-down sequencing diagram in Figure 5. If the V terminal is to remain powered after a DD_33_AUX systemshutdown,thenthebridgepower-downsequenceisexactlythesameasshowninFigure5. V and DD_15 V DDA_15 V and DD_33 V DDA_33 PCIR REFCLK PERST Figure5. Power-DownSequence Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 23 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com 7 Parameter Measurement Information LOADCIRCUITPARAMETERS TIMING CLOAD† IOL IOH VLOAD IOL PARAMETER (pF) (mA) (mA) (V) tPZH 0 ten 30/50 12 -12 Test tPZL 3 Point tdis tPHZ 30/50 12 -12 1.5 FrUomndOeruTtpeustt VLOAD tPLZ ‡ tpd 30/50 12 -12 CLOAD †CLOADincludesthetypicalload-circuitdistributedcapacitance. IOH ‡VLOAD- VOL=50Ω,whereVOL=0.6V,IOL=12mA IOL LOADCIRCUIT Timing VDD VDD Input 50%VDD High-Level (seeNoteA) 0V Input 50%VDD 50%VDD 0V tsu th Data 90%VDD VDD tw Input 10%VDD 50%VDD 50%VDD VDD tr tf 0V Low-LInepvuetl 50%VDD 50%VDD 0V VOLTAGEWAVEFORMS VOLTAGEWAVEFORMS SETUPANDHOLDTIMES PULSEDURATION INPUTRISEANDFALLTIMES Output VDD Control 50%VDD 50%VDD (low-level VDD enabling) 0V Input (seeNoteA) 50%VDD 50%VDD tPZL 0V tPLZ tpd tpd VDD InO-Puhtapsuet 50%VDD 50%VVVDOODHL (WseaeveNfootremB1) 5t0P%HZVDD VOL+0.3VV≈O50L%VDD tpd tpd tPZH VOH Out-ofO-Puhtapsuet 50%VDD 50%VVDODH (WseaeveNfootremB2) 50%VDD VOH- 0.3≈V50%VDD VOL 0V VOLTAGEWAVEFORMS VOLTAGEWAVEFORMS PROPAGATIONDELAYTIMES ENABLEANDDISABLETIMES,3-STATEOUTPUTS A. Phase relationships between waveforms were chosen arbitrarily. All input pulses are supplied by pulse generators havingthefollowingcharacteristics:PRR=1MHz,Z =50Ω,t ≤6ns,t ≤6ns. O r f B. Waveform1 is for an outputwith internalconditions such that theoutputis lowexceptwhendisabledby theoutput control.Waveform2isforanoutputwithinternalconditionssuchthattheoutputishighexceptwhendisabledbythe outputcontrol. C. Fort andt ,V andV aremeasuredvalues. PLZ PHZ OL OH Figure6. LoadCircuitAndVoltageWaveforms 24 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 twH 2V twL 2VminPeak-to-Peak 0.8V trise tfall tc Figure7. CLKTimingWaveform CLK tw PRST tsu Figure8. PRSTTimingWaveforms CLK 1.5V tpd tpd PCIOutput 1.5V Valid ton toff PCIInput Valid tsu th Figure9. SharedSignalsTimingWaveforms Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 25 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com 8 Detailed Description 8.1 Overview The Texas Instruments XIO2001 is a PCI Express to PCI local bus translation bridge that provides full PCI ExpressandPCIlocalbusfunctionalityandperformance. Power management (PM) features include active state link PM, PME mechanisms, the beacon and wake protocols, and all conventional PCI D-states. If the active state link PM is enabled, then the link automatically savespowerwhenidleusingtheL0sandL1states.PMactivestateNAK,PMPME,andPME-to-ACKmessages are supported. Standard PCI bus power management features provide several low power modes, which enable thehostsystemtofurtherreducepowerconsumption. The bridge has additional capabilities including, but not limited to, serial IRQ with MSI messages, serial EEPROM, power override, clock run, PCI Express clock request and PCI bus LOCK. Also, five general-purpose inputsandoutputs(GPIOs)areprovidedforfurthersystemcontrolandcustomization. Robust pipeline architecture is implemented to minimize system latency across the bridge. If parity errors are detected,thenpacketpoisoningissupportedforbothupstreamanddownstreamoperations. The PCI local bus is fully compliant with the PCI Local Bus Specification (Revision 2.3) and associated programming model. Also, the bridge supports the standard PCI-to-PCI bridge programming model. The PCI bus interface is 32-bit and can operate at either 25 MHz, 33 MHz, 50 MHz, or 66 MHz. Also, the PCI interface providesfairarbitrationandbufferedclockoutputsforupto6subordinatedevices. 8.2 Functional Block Diagram PCI Express PCI Express Transmitter Receiver Power Mgmt GPIO Clock Configuration and Serial Generator Memory Register EEPROM Reset Serial Controller IRQ PCI Bus Interface 8.3 Feature Description 8.3.1 BridgeResetFeatures There are five bridge reset options that include internally-generated power-on reset, resets generated by asserting input terminals, and software-initiated resets that are controlled by sending a PCI Express hot reset or setting a configuration register bit. Table 1 identifies these reset sources and describes how the bridge responds toeachreset. 26 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 Feature Description (continued) Table1.XIO2001ResetOptions RESET XIO2001FEATURE RESETRESPONSE OPTION Bridge Duringapower-oncycle,thebridgeassertsaninternalreset Whentheinternalpower-onresetisasserted,allcontrol internally- andmonitorstheV terminal.Whenthisterminal registers,statemachines,stickyregisterbits,andpower DD_15_COMB generated reaches90%ofthenominalinputvoltagespecification, managementstatemachinesareinitializedtotheirdefault power-onreset powerisconsideredstable.Afterstablepower,thebridge state. monitorsthePCIExpressreferenceclock(REFCLK)and Inaddition,theXIO2001assertstheinternalPCIbusreset. waits10μsafteractiveclocksaredetected.Then,internal power-onresetisdeasserted. Globalreset WhenGRSTisassertedlow,aninternalpower-onreset WhenGRSTisassertedlow,allcontrolregisters,state input occurs.Thisresetisasynchronousandfunctionsduring machines,stickyregisterbits,andpowermanagement GRST bothnormalpowerstatesandV powerstates. statemachinesareinitializedtotheirdefaultstate.In AUX addition,thebridgeassertsPCIbusreset(PRST).When therisingedgeofGRSToccurs,thebridgesamplesthe stateofallstaticcontrolinputsandlatchestheinformation internally.IfanexternalserialEEPROMisdetected,thena downloadcycleisinitiated.Also,theprocesstoconfigure andinitializethePCIExpresslinkisstarted.Thebridge startslinktrainingwithin80msafterGRSTisdeasserted. PCIExpress ThisXIO2001inputterminalisusedbyanupstreamPCI WhenPERSTisassertedlow,allcontrolregisterbitsthat resetinput ExpressdevicetogenerateaPCIExpressresetandto arenotstickyarereset.Withintheconfigurationregister PERST signalasystempowergoodcondition. maps,thestickybitsareindicatedbythe☆symbol.Also, allstatemachinesthatarenotassociatedwithsticky WhenPERSTisassertedlow,theXIO2001generatesan functionalityarereset. internalPCIExpressresetasdefinedinthePCIExpress specification. WhenPERSTtransitionsfromlowtohigh,asystempower Inaddition,theXIO2001assertstheinternalPCIbusreset. goodconditionisassumedbytheXIO2001. Note:ThesystemmustassertPERSTbeforepoweris WhentherisingedgeofPERSToccurs,theXIO2001 removed,beforeREFCLKisremovedorbeforeREFCLK samplesthestateofallstaticcontrolinputsandlatches becomesunstable. theinformationinternally.IfanexternalserialEEPROMis detected,thenadownloadcycleisinitiated.Also,the processtoconfigureandinitializethePCIExpresslinkis started.TheXIO2001startslinktrainingwithin80msafter PERSTisdeasserted. PCIExpress TheXIO2001respondstoatrainingcontrolhotreset IntheDL_DOWNstate,allremainingconfigurationregister trainingcontrol receivedonthePCIExpressinterface.Afteratraining bitsandstatemachinesarereset.Allremainingbits hotreset controlhotreset,thePCIExpressinterfaceentersthe excludestickybitsandEEPROMloadablebits.All DL_DOWNstate. remainingstatemachinesexcludestickyfunctionalityand EEPROMfunctionality. Withintheconfigurationregistermaps,thestickybitsare indicatedbythe☆symbolandtheEEPROMloadablebits areindicatedbythe†symbol. Inaddition,theXIO2001assertstheinternalPCIbusreset. PCIbusreset Systemsoftwarehastheabilitytoassertanddeassertthe Whenbit6(SRST)inthebridgecontrolregisteratoffset PRST PRSTterminalonthesecondaryPCIbusinterface.This 3Eh(seeBridgeControlRegister)isasserted,thebridge terminalisthePCIbusreset. assertsthePRSTterminal.A0intheSRSTbitdeasserts thePRSTterminal. 8.3.2 PCIExpressInterface The XIO2001 has an x1 PCI Express interface that runs at 2.5 Gb/s and is fully compliant to the PCI Express Base Specification , Revision 2.0. The remainder of this section describes implementation considerations for the XIO2001primaryPCIExpressinterface. 8.3.2.1 2.5-Gb/sTransmitandReceiveLinks The XIO2001 TX and RX terminals attach to the upstream PCI Express device over a 2.5-Gb/s high- speed differentialtransmitandreceivePCIExpress× 1Link.TheconnectiondetailsareprovidedinTable2. Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 27 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com Table2.XIO2001/PCIExpressDevicePinConnectionDetails PINNAME UPSTREAMPCI COMMENTS XIO2001 EXPRESSDEVICE XIO2001'stransmitpositivedifferentialpinconnectstotheupstreamdevice'sreceive TXP RXP positivedifferentialpin. XIO2001'stransmitpositivedifferentialpinconnectstotheupstreamdevice'sreceive TXN RXN negativedifferentialpin. XIO2001'stransmitpositivedifferentialpinconnectstotheupstreamdevice'sreceive RXP TXP positivedifferentialpin. XIO2001'stransmitpositivedifferentialpinconnectstotheupstreamdevice'sreceive RXN TXN negativedifferentialpin. The XIO2001 TXP and TXN terminals comprise a low-voltage, 100- Ω differentially driven signal pair. The RXP and RXN terminals for the XIO2001 receive a low-voltage, 100- Ω differentially driven signal pair. The XIO2001 has integrated 50- Ω termination resistors to V on both the RXP and RXN terminals eliminating the need for SS externalcomponents. Each lane of the differential signal pair must be ac-coupled. The recommended value for the series capacitor is 0.1 μF. To minimize stray capacitance associated with the series capacitor circuit board solder pads, 0402-sized capacitorsarerecommended. When routing a 2.5-Gb/s low-voltage, 100- Ω differentially driven signal pair, the following circuit board design guidelinesmustbeconsidered: 1. The PCI-Express drivers and receivers are designed to operate with adequate bit error rate margins over a 20”maximumlengthsignalpairroutedthroughFR4circuitboardmaterial. 2. Each differential signal pair must be 100- Ω differential impedance with each single-ended lane measuring in therangeof50Ω to55Ω impedancetoground. 3. The differential signal trace lengths associated with a PCI Express high-speed link must be length matched to minimize signal jitter. This length matching requirement applies only to the P and N signals within a differential pair. The transmitter differential pair does not need to be length matched to the receiver differential pair. The absolute maximum trace length difference between the TXP signal and TXN signal must belessthan5mils.ThisalsoappliestotheRXPandRXNsignalpair. 4. If a differential signal pair is broken into segments by vias, series capacitors, or connectors, the length of the positive signal trace must be length matched to the negative signal trace for each segment. Trace length differencesoverallsegmentsareadditiveandmustbelessthan5mils. 5. The location of the series capacitors is critical. For add-in cards, the series capacitors are located between the TXP/TXN terminals and the PCI-Express connector. In addition, the capacitors are placed near the PCI Express connector. This translates to two capacitors on the motherboard for the downstream link and two capacitors on the add-in card for the upstream link. If both the upstream device and the downstream device resideonthesamecircuitboard,thecapacitorsarelocatedneartheTXP/TXNterminalsforeachlink. 6. The number of vias must be minimized. Each signal trace via reduces the maximum trace length by approximately2inches.Forexample:if6viasareneeded,themaximumtracelengthis8inches. 7. When routing a differential signal pair, 45 degree angles are preferred over 90 degree angles. Signal trace lengthmatchingiseasierwith45-degreeanglesandoverallsignaltracelengthisreduced. 8. The differential signal pairs must not be routed over gaps in the power planes or ground planes. This causes impedancemismatches. 9. If vias are used to change from one signal layer to another signal layer, it is important to maintain the same 50- Ω impedance reference to the ground plane. Changing reference planes causes signal trace impedance mismatches. If changing reference planes cannot be prevented, bypass capacitors connecting the two referenceplanesnexttothesignaltraceviaswillhelpreducetheimpedancemismatch. 10. If possible, the differential signal pairs must be routed on the top and bottom layers of a circuit board. Signal propagationspeedsarefasteronexternalsignallayers. 8.3.2.2 TransmitterReferenceResistor The REF0_PCIE and REF1_PCIE terminals connect to an external resistor to set the drive current for the PCI ExpressTXdriver.Therecommendedresistorvalueis14,532 Ωwith1%tolerance. 28 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 A 14,532- Ω resistor is a custom value. To eliminate the need for a custom resistor, two series resistors are recommended: a 14,300- Ω , 1% resistor and a 232- Ω , 1% resistor. Trace lengths must be kept short to minimizenoisecouplingintothereferenceresistorterminals. 8.3.2.3 ReferenceClock The XIO2001 requires an external reference clock for the PCI-Express interface. The section provide information concerning the requirements for this reference clock. The XIO2001 is designed to meet all stated specifications when the reference clock input is within all PCI Express operating parameters. This includes both standard clock oscillatorsourcesorspreadspectrumclockoscillatorsources. The XIO2001 supports two options for the PCI Express reference clock: a 100-MHz common differential reference clock or a 125-MHz asynchronous single-ended reference clock. Both implementations are described below. The first option is a system-wide, 100-MHz differential reference clock. A single clock source with multiple differential clock outputs is connected to all PCI Express devices in the system. The differential connection between the clock source and each PCI Express device is point-topoint. This system implementation is referred toasacommonclockdesign. The XIO2001 is optimized for this type of system clock design. The REFCLK+ and REFCLK– pins provide differential reference clock inputs to the XIO2001. The circuit board routing rules associated with the 100-MHz differential reference clock are the same as the 2.5-Gb/s TX and RX link routing rules itemized in 2.5-Gb/s Transmit and Receive Links. The only difference is that the differential reference clock does not require series capacitors.TherequirementisaDCconnectionfromtheclockdriveroutputtotheXIO2001receiverinput. Terminating the differential clock signal is circuit board design specific. But, the XIO2001 design has no internal 50- Ω -to-ground termination resistors. Both REFCLK inputs, at approximately 20 k Ω to ground, are high- impedanceinputs. The second option is a 125-MHz asynchronous single-ended reference clock. For this case, the devices at each end of the PCI Express link have different clock sources. The XIO2001 has a 125-MHz single-ended reference clock option for asynchronous clocking designs. When the REFCLK125_SEL input terminal is tied to V , this DD_33 clockingmodeisenabled. The single-ended reference clock is attached to the REFCLK+ terminal. The REFCLK+ input, at approximately 20 k Ω , is a high-impedance input. Any clock termination design must account for a high- impedance input. The REFCLK– pinisattachedtoa0.1-μ Fcapacitor.Thecapacitor’ssecondpinisconnectedtoV . SSA 8.3.2.4 Reset The XIO2001 PCI Express reset (PERST) terminal connects to the upstream PCI Express device’s PERST output.The PERSTinputcellhashysteresisandisoperationalduringboththemainpowerstateandV power AUX state.Noexternalcomponentsarerequired. Please reference the section to fully understand the PERST electrical requirements and timing requirements associated with power-up and power-down sequencing. Also, the data manual identifies all configuration and memory-mappedregisterbitsthatareresetbyPERST. 8.3.2.5 Beacon ThebridgesupportsthePCIExpressin-bandbeaconfeature.BeaconisdrivenontheupstreamPCIExpresslink by the bridge to request the reapplication of main power when in the L2 link state. To enable the beacon feature, bit 10 (BEACON_ENABLE) in the general control register at offset D4h is asserted. See General Control Register,GeneralControlRegister,fordetails. If the bridge is in the L2 link state and beacon is enabled, when a secondary PCI bus device asserts PME, then the bridge outputs the beacon signal on the upstream PCI Express link. The beacon signal frequency is approximately 500 kHz ± 50% with a differential peak-to-peak amplitude of 500 mV and no de-emphasis. Once the beacon is activated, the bridge continues to send the beacon signal until main power is restored as indicated byPERSTgoinginactive.Atthistime,thebeaconsignalisdeactivated. Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 29 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com 8.3.2.6 Wake PCI Express WAKE is an open-drain output from the XIO2001 that is driven low to re-activate the PCI Express link hierarchy’s main power rails and reference clocks. This PCI Express side-band signal is connected to the WAKE input on the upstream PCIe device. WAKE is operational during both the main power state and V AUX powerstate. Since WAKE is an open-drain output, a system side pullup resistor is required to prevent the signal from floating. Thedrivecapabilityofthisopen-drainoutputis4mA.Therefore,thevalueoftheselectedpullupresistormustbe largeenoughtoassurealogiclowsignallevelatthereceiver.Arobustsystemdesignwillselectapullupresistor value that de-rates the output driver current capability by a minimum of 50%. At 3.3 V with a de-rated drive current equal to 2 mA, the minimum resistor value is 1.65 k Ω . Larger resistor values are recommended to reducethecurrentdrainontheV supply. AUX 8.3.2.7 InitialFlowControlCredits The bridge flow control credits are initialized using the rules defined in the PCI Express Base Specification. Table3identifiestheinitialflowcontrolcreditadvertisementforthebridge. Table3.InitialFlowControlCreditAdvertisements CREDITTYPE INITIALADVERTISEMENT Postedrequestheaders(PH) 8 Postedrequestdata(PD) 128 Non-postedheader(NPH) 4 Non-posteddata(NPD) 4 Completionheader(CPLH) 0(infinite) Completiondata(CPLD) 0(infinite) 8.3.2.8 PCIExpressMessageTransactions PCI Express messages are both initiated and received by the bridge. Table 4 outlines message support within thebridge. Table4.MessagesSupportedbytheBridge MESSAGE SUPPORTED BRIDGEACTION Assert_INTx Yes Transmittedupstream Deassert_INTx Yes Transmittedupstream PM_Active_State_Nak Yes Receivedandprocessed PM_PME Yes Transmittedupstream PME_Turn_Off Yes Receivedandprocessed PME_TO_Ack Yes Transmittedupstream ERR_COR Yes Transmittedupstream ERR_NONFATAL Yes Transmittedupstream ERR_FATAL Yes Transmittedupstream Set_Slot_Power_Limit Yes Receivedandprocessed Unlock No Discarded Hotplugmessages No Discarded Advancedswitchingmessages No Discarded Vendordefinedtype0 No Unsupportedrequest Vendordefinedtype1 No Discarded AllsupportedmessagetransactionsareprocessedperthePCIExpressBaseSpecification. 8.3.3 PCIPortArbitration The internal PCI port arbitration logic supports up to six external PCI bus devices plus the bridge. This bridge supportsaclassicPCIarbiter. 30 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 8.3.3.1 ClassicPCIArbiter The classic PCI arbiter is configured through the classic PCI configuration space at offset DCh. Table 5 identifies anddescribestheregistersassociatedwithclassicPCIarbitrationmode. Table5.ClassicPCIArbiterRegisters PCIOFFSET REGISTERNAME DESCRIPTION Arbitercontrol Containsatwo-tierpriorityschemeforthebridgeandsixPCIbusdevices.The ClassicPCIconfiguration (seeArbiterControl bridgedefaultstothehighprioritytier.ThesixPCIbusdevicesdefaulttothelow registerDCh Register) prioritytier.Abusparkingcontrolbit(bit7,PARK)isprovided. SixmaskbitsprovideindividualcontroltoblockeachPCIBusREQinput.Bit7 (ARB_TIMEOUT)inthearbiterrequestmaskregisterenablesgeneratingtimeout Arbiterrequestmask ClassicPCIconfiguration statusifaPCIdevicedoesnotrespondwithin16PCIbusclocks.Bit6 (seeArbiterRequest registerDDh (AUTO_MASK)inthearbiterrequestmaskregisterautomaticallymasksaPCIbus MaskRegister) REQifthedevicedoesnotrespondafterGNTisissued.TheAUTO_MASKbitis clearedtodisableanyautomaticallygeneratedmask. Arbitertime-outstatus ClassicPCIconfiguration Whenbit7(ARB_TIMEOUT)inthearbiterrequestmaskregisterisasserted, (seeArbiterTime-Out registerDEh timeoutstatusforeachPCIbusdeviceisreportedinthisregister. StatusRegister) 8.3.4 ConfigurationRegisterTranslation PCI Express configuration register transactions received by the bridge are decoded based on the transaction’s destinationID.Theseconfigurationtransactionscanbebrokenintothreesubcategories:type0transactions,type 1 transactions that target the secondary bus, and type 1 transactions that target a downstream bus other than thesecondarybus. PCI Express type 0 configuration register transactions always target the configuration space and are never passedontothesecondaryinterface. Type 1 configuration register transactions that target a device on the secondary bus are converted to type 0 configuration register transactions on the PCI bus. Figure 10 shows the address phase of a type 0 configuration transactiononthePCIbusasdefinedbythePCIspecification. Figure10. Type0ConfigurationTransactionAddressPhaseEncoding In addition, the bridge converts the destination ID device number to one of the AD[31:16] lines as the IDSEL signal.TheimplementedIDSELsignalmappingisshowninTable6. Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 31 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com Table6.Type0ConfigurationTransactionIDSEL Mapping DEVICE AD[31:16] NUMBER 00000 0000000000000001 00001 0000000000000010 00010 0000000000000100 00011 0000000000001000 00100 0000000000010000 00101 0000000000100000 00110 0000000001000000 00111 0000000010000000 01000 0000000100000000 01001 0000001000000000 01010 0000010000000000 01011 0000100000000000 01100 0001000000000000 01101 0010000000000000 01110 0100000000000000 01111 1000000000000000 1xxxx 0000000000000000 Type 1 configuration registers transactions that target a downstream bus other then the secondary bus are output on the PCI bus as type 1 PCI configuration transactions. Figure 11 shows the address phase of a type 1 configurationtransactiononthePCIbusasdefinedbythePCIspecification. Figure11. Type1ConfigurationTransactionAddressPhaseEncoding 32 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 8.3.5 PCIInterruptConversiontoPCIExpressMessages ThebridgeconvertsinterruptsfromthePCIbussidebandinterruptsignalstoPCIExpressinterruptmessages. Table7,Figure12,andFigure13illustratetheformatforboththeassertanddeassertINTxmessages. Table7.InterruptMappingIn TheCodeField INTERRUPT CODEFIELD INTA 00 INTB 01 INTC 10 INTD 11 Figure12. PCIExpressASSERT_INTXMessage Figure13. PCIExpressDEASSERT_INTXMessage 8.3.6 PMEConversiontoPCIExpressMessages When the PCI bus PME input transitions low, the bridge generates and sends a PCI Express PME message upstream. The requester ID portion of the PME message uses the stored value in the secondary bus number register as the bus number, 0 as the device number, and 0 as the function number. The Tag field for each PME messageis00h.APMEmessageissentperiodicallyuntilthePMEsignaltransitionshigh. Figure14illustratestheformatforaPCIExpressPMEmessage. Figure14. PCIExpressPMEMessage Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 33 ProductFolderLinks:XIO2001

XIO2001 SCPS212I–MAY2009–REVISEDJANUARY2016 www.ti.com 8.3.7 PCIExpresstoPCIBusLockConversion The bus-locking protocol defined in the PCI Express Base Specification and PCI Local Bus Specification is providedonthebridgeasanadditionalcompatibilityfeature.ThePCIbus LOCKsignalisadedicatedoutputthat isenabledbysettingbit12inthegeneralcontrolregisteratoffsetD4h.SeeGeneralControlRegister,fordetails. NOTE The use of LOCK is only supported by PCI-Express to PCI Bridges in the downstream direction(awayfromtherootcomplex). PCI Express locked-memory read request transactions are treated the same as PCI Express memory read transactions except that the bridge returns a completion for a locked-memory read. Also, the bridge uses the PCI LOCKprotocolwheninitiatingthememoryreadtransactiononthePCIbus. When a PCI Express locked-memory read request transaction is received and the bridge is not already locked, the bridge arbitrates for use of the LOCK terminal by asserting REQ. If the bridge receives GNT and the LOCK terminal is high, then the bridge drives the LOCK terminal low after the address phase of the first locked-memory read transaction to take ownership of LOCK. The bridge continues to assert LOCK except during the address phaseoflockedtransactions.Ifthebridgereceives GNT andtheLOCKterminalislow,thenthebridgedeasserts its REQandwaitsuntil LOCKishighandthebusisidlebeforere-arbitratingfortheuseof LOCK. CLK FRAME LOCK AD Address Data IRDY TRDY DEVSEL Figure15. StartingaLockedSequence Once the bridge has ownership of LOCK, the bridge initiates the lock read as a memory read transaction on the PCI bus. When the target of the locked-memory read returns data, the bridge is considered locked and all transactionsnotassociatedwiththelockedsequenceareblockedbythebridge. 34 SubmitDocumentationFeedback Copyright©2009–2016,TexasInstrumentsIncorporated ProductFolderLinks:XIO2001

XIO2001 www.ti.com SCPS212I–MAY2009–REVISEDJANUARY2016 Figure16. ContinuingaLockedSequence Because PCI Express does not have a unique locked-memory write request packet, all PCI Express memory write requests that are received while the bridge is locked are considered part of the locked sequence and are transmittedtoPCIaslocked-memorywritetransactions. The bridge terminates the locked sequence when an unlock message is received from PCI Express and all previouslockedtransactionshavebeencompleted. CLK FRAME LOCK IRDY Figure17. TerminatingaLockedSequence Intheerroneouscasethatanormaldownstreammemoryreadrequestisreceivedduringalockedsequence,the bridge responds with an unsupported request completion status. Note that this condition must never occur, because the PCI Express Specification requires the root complex to block normal memory read requests at the source.Alllockedsequencesthatendsuccessfullyorwithanerrorconditionmustbeimmediatelyfollowedbyan unlockmessage.Thisunlockmessageisrequiredtoreturnthebridgetoaknownunlockedstate. 8.3.8 Two-WireSerial-BusInterface The bridge provides a two-wire serial-bus interface to load subsystem identification information and specific register defaults from an external EEPROM. The serial-bus interface signals (SDA and SCL) are shared with two of the GPIO terminals (3 and 4). If the serial bus interface is enabled, then the GPIO3 and GPIO4 terminals are disabled.Iftheserialbusinterfaceisdisabled,thentheGPIOterminalsoperateasdescribedinGeneral-Purpose I/OInterface. 8.3.8.1 Serial-BusInterfaceImplementation Toenabletheserial-businterface,apullupresistormustbeimplementedontheSCLsignal.Attherisingedgeof PERST or GRST, whichever occurs later in time, the SCL terminal is checked for a pullup resistor. If one is detected, then bit 3 (SBDETECT) in the serial-bus control and status register (see Serial-Bus Control and Status Register)isset.Softwaremaydisabletheserial-businterfaceatanytimebywritinga0btotheSBDETECTbit.If no external EEPROM is required, then the serial-bus interface is permanently disabled by attaching a pulldown resistortotheSCLsignal. Copyright©2009–2016,TexasInstrumentsIncorporated SubmitDocumentationFeedback 35 ProductFolderLinks:XIO2001