ICGOO在线商城 > 集成电路(IC) > PMIC - 稳压器 - 线性 > TPS75533KTTT

- 型号: TPS75533KTTT

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

TPS75533KTTT产品简介:

ICGOO电子元器件商城为您提供TPS75533KTTT由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 TPS75533KTTT价格参考。Texas InstrumentsTPS75533KTTT封装/规格:PMIC - 稳压器 - 线性, Linear Voltage Regulator IC Positive Fixed 1 Output 3.3V 5A DDPAK/TO-263-5。您可以下载TPS75533KTTT参考资料、Datasheet数据手册功能说明书,资料中有TPS75533KTTT 详细功能的应用电路图电压和使用方法及教程。

Texas Instruments(德州仪器)的TPS75533KTTT是一款低功耗、低压差线性稳压器,属于PMIC(电源管理集成电路)系列。它具有3.3V固定输出电压和150mA的最大输出电流,适用于需要稳定电源的应用场景。以下是该型号的一些典型应用场景: 1. 便携式电子设备 TPS75533KTTT因其低功耗和小封装尺寸,特别适合用于电池供电的便携式设备,如智能手机、平板电脑、可穿戴设备(如智能手表、健身追踪器)等。这些设备通常对电源效率要求较高,而TPS75533KTTT的低静态电流(典型值为20µA)有助于延长电池寿命。 2. 物联网(IoT)设备 在物联网设备中,TPS75533KTTT可以为传感器、微控制器和其他低功耗组件提供稳定的电源。由于其低压差特性(典型值为300mV),它可以在较低的输入电压下工作,适应不同类型的电池或电源适配器,确保设备在各种环境下都能正常运行。 3. 工业自动化 在工业自动化领域,TPS75533KTTT可用于为传感器、执行器和通信模块提供稳定的电源。它的高精度输出电压(±1%)和良好的瞬态响应性能,能够确保系统在复杂电磁环境下的稳定性。此外,该器件的工作温度范围较宽(-40°C至+85°C),适合工业环境中常见的高温和低温条件。 4. 医疗设备 对于一些小型医疗设备,如血糖仪、脉搏血氧仪等,TPS75533KTTT可以为其提供可靠且稳定的电源。这些设备通常对电源的精度和可靠性有严格要求,而TPS75533KTTT的低噪声和高精度输出电压特性使其成为理想选择。 5. 无线通信模块 在无线通信模块中,TPS75533KTTT可以为射频(RF)前端、基带处理器和其他关键组件提供稳定的电源。其低压差特性和低噪声输出有助于提高通信质量,减少干扰,确保信号传输的稳定性。 总之,TPS75533KTTT凭借其低功耗、低压差、高精度和小尺寸的特点,广泛适用于多种需要稳定电源供应的应用场景,尤其是在对电源效率和空间有限的场合。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC REG LDO 3.3V 5A DDPAK低压差稳压器 3.3-Volt 5A LDO |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 电源管理 IC,低压差稳压器,Texas Instruments TPS75533KTTT- |

| 数据手册 | |

| 产品型号 | TPS75533KTTT |

| 产品目录页面 | |

| 产品种类 | 低压差稳压器 |

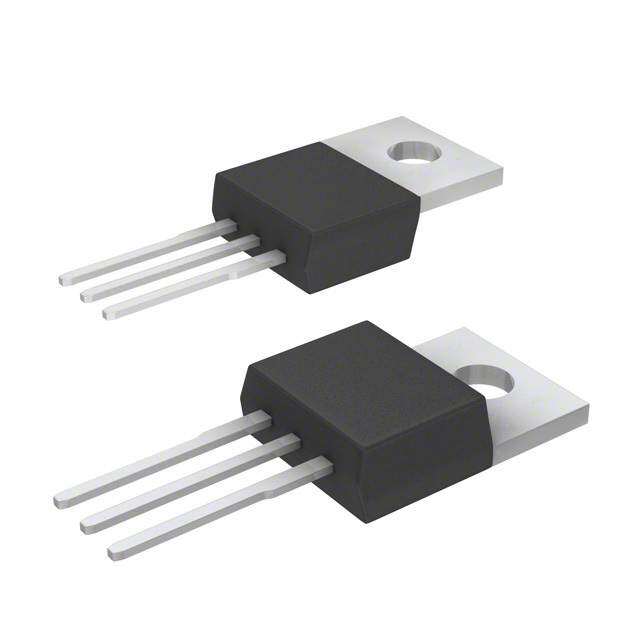

| 供应商器件封装 | DDPAK/TO-263-5 |

| 其它名称 | 296-15914-6 |

| 包装 | Digi-Reel® |

| 单位重量 | 1.456 g |

| 商标 | Texas Instruments |

| 回动电压—最大值 | 500 mV at 5 A |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | TO-263-6,D²Pak(5 引线+接片),TO-263BA |

| 封装/箱体 | TO-263-5 |

| 工作温度 | -40°C ~ 125°C |

| 工厂包装数量 | 50 |

| 最大工作温度 | + 125 C |

| 最大输入电压 | 5.5 V |

| 最小工作温度 | - 40 C |

| 最小输入电压 | + 2.8 V |

| 标准包装 | 1 |

| 电压-跌落(典型值) | 0.25V @ 5A |

| 电压-输入 | 最高 5.5V |

| 电压-输出 | 3.3V |

| 电压调节准确度 | 3 % |

| 电流-输出 | 5A |

| 电流-限制(最小值) | 5.5A |

| 稳压器拓扑 | 正,固定式 |

| 稳压器数 | 1 |

| 系列 | TPS75533 |

| 线路调整率 | 0.04 % / V |

| 负载调节 | 0.35 % / V |

| 输入偏压电流—最大 | 0.125 mA |

| 输出电压 | 3.3 V |

| 输出电流 | 5 A |

| 输出端数量 | 1 Output |

| 输出类型 | Fixed |

| 配用 | /product-detail/zh/TPS75525EVM/296-13591-ND/486549 |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 (cid:1) 5-A Low-Dropout Voltage Regulator TO–220 (KC) PACKAGE (cid:1) (TOP VIEW) Available in 1.5-V, 1.8-V, 2.5-V, and 3.3-V Fixed-Output and Adjustable Versions EN 1 (cid:1) IN 2 Open Drain Power-Good (PG) Status GND 3 Output (Fixed Options Only) OUTPUT 4 (cid:1) FB/PG 5 Tab is GND Dropout Voltage Typically 250 mV at 5 A (TPS75533) TO–263 (KTT) PACKAGE (cid:1) Low 125 µA Typical Quiescent Current (TOP VIEW) (cid:1) Fast Transient Response EN 1 (cid:1) 3% Tolerance Over Specified Conditions for IN 2 Fixed-Output Versions GND 3 (cid:1) Available in 5-Pin TO–220 and TO–263 OUTPUT 4 Surface-Mount Packages FB/PG 5 Tab is GND (cid:1) Thermal Shutdown Protection description The TPS755xx family of 5-A low dropout (LDO) regulators contains four fixed voltage option regulators with integrated power-good (PG) and an adjustable voltage option regulator. These devices are capable of supplying 5 A of output current with a dropout of 250 mV (TPS75533). Therefore, the device is capable of performing a 3.3-V to 2.5-V conversion. Quiescent current is 125 µA at full load and drops down to less than 1 µA when the device is disabled. The TPS755xx is designed to have fast transient response for large load current changes. TPS75533 DROPOUT VOLTAGE vs TPS75515 LOAD TRANSIENT RESPONSE JUNCTION TEMPERATURE 400 V 150 m IO = 5 A – VO = 1.5 V 350 VO = 3.3 V ge 100 Co = 100 µF a – mV 300 ut Volt 50 ge utp a 250 O 0 olt n ut V 200 ge i –50 o n A – DropO 150 – ChaVO–100 ddti(cid:1)1.2µ5sA urrent – VD 100 ∆ –150 5 ut C p ut 50 0 O – 0 I O –40 –25 –10 5 20 35 50 65 80 95 110 125 0 20 40 60 80 100 120 140 160 180 200 TJ – Junction Temperature – °C t – Time – µs Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PRODUCTION DATA information is current as of publication date. Copyright 2001, Texas Instruments Incorporated Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 description (continued) Because the PMOS device behaves as a low-value resistor, the dropout voltage is very low (typically 250 mV at an output current of 5 A for the TPS75533) and is directly proportional to the output current. Additionally, since the PMOS pass element is a voltage-driven device, the quiescent current is very low and independent of output loading (typically 125 µA over the full range of output current). These two key specifications yield a significant improvement in operating life for battery-powered systems. The device is enabled when EN is connected to a low-level voltage. This LDO family also features a sleep mode; applying a TTL high signal to EN (enable) shuts down the regulator, reducing the quiescent current to less than 1 µA at T = 25°C. The power-good terminal (PG) is an active low, open drain output, which can be used to J implement a power-on reset or a low-battery indicator. The TPS755xx is offered in 1.5-V, 1.8-V, 2.5-V, and 3.3-V fixed-voltage versions and in an adjustable version (programmable over the range of 1.22 V to 5 V). Output voltage tolerance is specified as a maximum of 3% over line, load, and temperature ranges. The TPS755xx family is available in a 5-pin TO–220 (KC) and TO–263 (KTT) packages. AVAILABLE OPTIONS OUTPUT VOLTAGE TJ (TYP) TO–220 (KC) TO–263(KTT) 3.3 V TPS75533KC TPS75533KTT 2.5 V TPS75525KC TPS75525KTT –40°C to 125°C 1.8 V TPS75518KC TPS75518KTT 1.5 V TPS75515KC TPS75515KTT Adjustable 1.22 V to 5 V TPS75501KC TPS75501KTT NOTE: The TPS75501 is programmable using an external resistor divider (see application information). The KTT package is available taped and reeled. Add an R suffix to the device type (e.g., TPS75501KTTR) to indicate tape and reel. 2 5 VI IN PG PG 4 OUT VO 1 µF 1 EN Co† + 47 µF GND 3 †See application information section for capacitor selection details. Figure 1. Typical Application Configuration (For Fixed Output Options) 2 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 functional block diagram—adjustable version VIN VOUT UVLO Current Sense SHUTDOWN ILIM R1 GND _ + FB EN UVLO R2 Thermal Shutdown External to the Device Vref = 1.22 V Bandgap VIN Reference functional block diagram—fixed version VIN VOUT UVLO Current Sense SHUTDOWN ILIM R1 _ + GND UVLO EN R2 Thermal Shutdown Vref = 1.22 V VIN Bandgap PG Reference Falling Edge Delay Terminal Functions (TPS755xx) TERMINAL II//OO DDEESSCCRRIIPPTTIIOONN NAME NO. EN 1 I Enable input FB/PG 5 I Feedback input voltage for adjustable device/PG output for fixed options GND 3 Regulator ground IN 2 I Input voltage OUTPUT 4 O Regulated output voltage POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 3

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 TPS755xx PG timing diagram VIN1 VUVLO VUVLO t VOUT VIT+(see Note A) Threshold Voltage VIT– (see Note A) t PG Output t NOTE A: VIT –Trip voltage is typically 9% lower than the output voltage (91%VO). VIT– to VIT+ is the hysteresis voltage. detailed description The TPS755xx family includes four fixed-output voltage regulators (1.5 V, 1.8 V, 2.5 V, and 3.3 V), and an adjustable regulator, the TPS75501 (adjustable from 1.22 V to 5 V). The bandgap voltage is typically 1.22 V. pin functions enable (EN) The EN terminal is an input which enables or shuts down the device. If EN is a logic high, the device will be in shutdown mode. When EN goes to logic low, the device will be enabled. power-good (PG) The PG terminal for the fixed voltage option devices is an open drain, active low output that indicates the status of VO (output of the LDO). When VO reaches approximately 91% of the regulated voltage, PG will go to a low impedance state. It will go to a high-impedance state when V falls below approximately 89% (i.e. over load O condition) of the regulated voltage. The open drain output of the PG terminal requires a pullup resistor. feedback (FB) FB is an input terminal used for the adjustable-output option and must be connected to the output terminal either directly, in order to generate the minimum output voltage of 1.22 V, or through an external feedback resistor divider for other output voltages. The FB connection should be as short as possible. It is essential to route it in such a way to minimize/avoid noise pickup. Adding RC networks between FB terminal and V to filter noise is O not recommended because it may cause the regulator to oscillate. 4 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 detailed description (continued) input voltage (IN) The V terminal is an input to the regulator. IN output voltage (OUTPUT) The V terminal is an output to the regulator. OUTPUT (cid:1) absolute maximum ratings over operating junction temperature range (unless otherwise noted) Input voltage range‡, V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to 6 V I Voltage range at EN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to 6 V Maximum PG voltage (fixed options only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 V Peak output current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Internally limited Continuous total power dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . See Dissipation Rating Tables Output voltage, V (OUTPUT, FB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.5 V O Operating junction temperature range, T . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –40°C to 150°C J Storage temperature range, T . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –65°C to 150°C stg ESD rating, HBM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 kV ESD rating, CDM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500 V †Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. ‡All voltage values are with respect to network terminal ground. DISSIPATION RATING TABLE PACKAGE RθJC (°C/W) RθJA (°C/W)§ TO–220 2 58.7¶ TO–263 2 38.7# §For both packages, the RθJA values were computed using JEDEC high K board (2S2P) with 1 ounce internal copper plane and ground plane. There was no air flow across the packages. ¶RθJA was computed assuming a vertical, free standing TO-220 package with pins soldered to the board. There is no heatsink attached to the package. #RθJA was computed assuming a horizontally mounted TO-263 package with pins soldered to the board. There is no copper pad underneath the package. recommended operating conditions MIN MAX UNIT Input voltage, VI|| 2.8 5.5 V Output voltage range, VO 1.22 5 V Output current, IO 0 5 A Operating virtual junction temperature, TJ –40 125 °C || To calculate the minimum input voltage for your maximum output current, use the following equation: VI(min) = VO(max) + VDO(max load). POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 5

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 electrical characteristics over recommended operating junction temperature range (T = –40°C to J 125°C), VI = VO(typ) + 1 V, IO = 1 mA, EN = 0 V, CO = 100 µF (unless otherwise noted) PARAMETER TEST CONDITIONS MIN TYP MAX UNIT 1.22 V ≤ VO ≤ 5.5 V, TJ = 25°C VO 1.22 V ≤ VO ≤ 5.5 V 0.97 VO 1.03 VO AAddjjuussttaabbllee vvoollttaaggee VV 1.22 V ≤ VO ≤ 5.5 V, TJ = 0 to 125°C (see Note 1) 0.98 VO 1.02 VO TJ = 25°C, 2.8 V < VI < 5.5 V 1.5 11.55 VV OOuuttppuutt 2.8 V ≤ VI ≤ 5.5 V 1.455 1.545 OOuttputt vollttage ((see NNotte 22)) VV TJ = 25°C, 2.8 V < VI < 5.5 V 1.8 11.88 VV OOuuttppuutt 2.8 V ≤ VI ≤ 5.5 V 1.746 1.854 TJ = 25°C, 3.5 V < VI < 5.5 V 2.5 22.55 VV OOuuttppuutt VV 3.5 V ≤ VI ≤ 5.5 V 2.425 2.575 TJ = 25°C, 4.3 V < VI < 5.5 V 3.3 33.33 VV OOuuttppuutt VV 4.3 V ≤ VI ≤ 5.5 V 3.201 3.399 TJ = 25°C 125 QQuuiieesscceenntt ccuurrrreenntt ((GGNNDD ccuurrrreenntt)) ((sseeee NNootteess 22 aanndd 33)) µAA 200 VO + 1 V ≤ VI ≤ 5.5 V, TJ = 25°C 0.04 OOuuttppuutt vvoollttaaggee lliinnee rreegguullaattiioonn ((∆∆VVO//VVO)) ((sseeee NNoottee 33)) VO + 1 V ≤ VI < 5.5 V 0.1 %%//VV Load regulation (see Note 2) 0.35 %/V Output noise voltage TPS75515 BW = 300 Hz to 50 kHz, TJ = 25°C, VI = 2.8 V 35 µVrms Output current limit VO = 0 V 5.5 10 14 A Thermal shutdown junction temperature 150 °C EN = VI, TJ = 25°C 0.1 µA SSttaannddbbyy ccuurrrreenntt EN = VI 10 µA FB input current TPS75501 FB = 1.5 V –1 1 µA f = 100 Hz, TJ = 25°C, Power supply ripple rejection TPS75515 60 dB VI = 2.8 V, IO = 5 A Minimum input voltage for valid PG IO(PG) = 300 µA, V(PG) ≤ 0.8 V 0 V PG trip threshold voltage Fixed options only VO decreasing 89 93 %VO PG hysteresis voltage Fixed options only Measured at VO 0.5 %VO PG output low voltage Fixed options only VI = 2.8 V, IO(PG) = 1 mA 0.15 0.4 V PG leakage current Fixed options only V(PG) = 5 V 1 µA NOTES: 1. The adjustable option operates with a 2% tolerance over TJ = 0 to 125 °C. 2. IO = 1≤ mA to 5 A 3. If VO 2.5 V then VImin = 2.8 V, VImax = 5.5 V: (cid:2) (cid:4) V V (cid:6)2.8V Lineregulation(mV) (cid:1) (cid:2)%(cid:3)V(cid:4) (cid:5) O Imax (cid:5)1000 100 If VO > 2.5 V then VImin = VO + 1 V, VImax = 5.5 V: (cid:2) (cid:2) (cid:4)(cid:4) V V (cid:6) V (cid:7)1V O Imax O Lineregulation(mV) (cid:1) (cid:2)%(cid:3)V(cid:4) (cid:5) (cid:5)1000 100 6 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 electrical characteristics over recommended operating junction temperature range (T = –40°C to J 125°C), VI = VO(typ) + 1 V, IO = 1 mA, EN = 0 V, CO = 100 µF (unless otherwise noted) (continued) PARAMETER TEST CONDITIONS MIN TYP MAX UNIT EN = VI –1 1 µA IInnppuutt ccuurrrreenntt ((EENN)) EN = 0 V –1 0 1 µA High level EN input voltage 2 V Low level EN input voltage 0.7 V IO = 5 A, VI = 3.2 V, TJ = 25°C 250 DDrrooppoouutt vvoollttaaggee, ((33.33 VV oouuttppuutt)) ((sseeee NNoottee 44)) mmVV VVOO IO = 5 A, VI = 3.2 V 500 Discharge transistor current VO = 1.5 V, TJ = 25°C 10 25 mA UVLO TJ = 25°C, VI rising 2.2 2.75 V VVI UVLO hysteresis TJ = 25°C, VI falling 100 mV NOTE 4: IN voltage equals VO(typ) – 100 mV; TPS75515, TPS75518, and TPS75525 dropout voltage limited by input voltage range limitations (i.e., TPS75533 input voltage is set to 3.2 V for the purpose of this test). TYPICAL CHARACTERISTICS Table of Graphs FIGURE vs Output current 2, 3 VVO OOuuttppuutt vvoollttaaggee vs Junction temperature 4, 5 Ground current vs Junction temperature 6 Power supply ripple rejection vs Frequency 7 Output spectral noise density vs Frequency 8 zo Output impedance vs Frequency 9 vs Input voltage 10 VVDO DDrrooppoouutt vvoollttaaggee vs Junction temperature 11 VI Minimum required input voltage vs Output voltage 12 Line transient response 13, 15 Load transient response 14, 16 VO Output voltage and enable voltage vs Time (start-up) 17 Equivalent series resistance vs Output current 19, 20 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 7

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 TYPICAL CHARACTERISTICS TPS75533 TPS75515 OUTPUT VOLTAGE OUTPUT VOLTAGE vs vs OUTPUT CURRENT OUTPUT CURRENT 3.345 1.545 VI = 4.3 V VI = 2.8 V TJ = 25°C TJ = 25°C 3.330 1.530 V V – 3.315 – 1.515 e e g g a a olt olt V 3.3 V 1.5 ut ut p p ut ut O O – 3.285 – 1.485 O O V V 3.270 1.470 3.255 1.455 0 1 2 3 4 5 0 1 2 3 4 5 IO – Output Current – A IO – Output Current – A Figure 2 Figure 3 TPS75533 TPS75515 OUTPUT VOLTAGE OUTPUT VOLTAGE vs vs JUNCTION TEMPERATURE JUNCTION TEMPERATURE 3.345 1.545 VI = 4.3 V VI = 2.8 V 3.33 1.530 V V – 3.315 – 1.515 e e g g a a olt olt V 3.3 V 1.5 ut ut p p ut ut O O – 3.285 – 1.485 O O V V 3.270 1.470 3.255 1.455 –40 –25 10 5 20 35 50 65 80 95 110125 –40–25 –10 5 20 35 50 65 80 95 110 125 TJ – Junction Temperature – °C TJ – Junction Temperature – °C Figure 4 Figure 5 8 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 TYPICAL CHARACTERISTICS TPS755xx TPS75733 GROUND CURRENT POWER SUPPLY RIPPLE REJECTION vs vs JUNCTION TEMPERATURE FREQUENCY 150 90 VI = 5 V B VI = 4.3 V IO = 5 A n – d 80 CTJo == 2150°0C µF o 70 ecti IO = 1 mA A 125 Rej 60 µnt – pple 50 e Ri Curr ply 40 nd Sup 30 Grou 100 wer 20 IO = 5 A o P – 10 R R S 0 P 75 –40 –25 –10 5 20 35 50 65 80 95 110 125 10 100 1k 10k 100k 1M 10M TJ – Junction Temperature – °C f – Frequency – Hz Figure 6 Figure 7 TPS75533 TPS75533 OUTPUT SPECTRAL NOISE DENSITY OUTPUT IMPEDANCE vs vs FREQUENCY FREQUENCY 2.5 100 VI = 4.3 V µV/Hznsity – 2 IO = 5 A TCVJOo = == 2 1350.°30C VµF Ωnce – 10 TVCJIo = == 4 21.530° 0VC µF e De 1.5 peda 1 IO = 1 mA s m ctral Noi 1 IO = 1 mA Output I 0.1 pe – S o ut 0.5 z p 0.01 IO = 5 A ut O 0 0.001 1100 100 1k 10k 100k 10 100 1k 10k 100k 1M 10M f – Frequency – Hz f – Frequency – Hz Figure 8 Figure 9 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 9

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 TYPICAL CHARACTERISTICS TPS75501 TPS75533 DROPOUT VOLTAGE DROPOUT VOLTAGE vs vs INPUT VOLTAGE JUNCTION TEMPERATURE 450 400 IO = 5 A IO = 5 A 400 350 VO = 3.3 V mV 350 TJ = 125°C mV 300 e – 300 ge – ut Voltag 250 TTJJ = = – 2450°°CC out Volta 220500 po 200 op o r – Dr 150 – DO 150 O D VD V 100 100 50 50 0 0 2.5 3 3.5 4 4.5 5 –40 –25 –10 5 20 35 50 65 80 95 110 125 VI – Input Voltage – V TJ – Junction Temperature – °C Figure 10 Figure 11 MINIMUM REQUIRED INPUT VOLTAGE vs TPS75515 OUTPUT VOLTAGE LINE TRANSIENT RESPONSE 4 VO = 1.5 V e – V IO = 5 A TJ = 125°C nge inge – mV 50 ICOo = = 5 1 0A0 µF nput Voltag TJ = –T40J° =C 25°C ∆V– ChaOutput Volta –500 d I O e 3 –100 r ui q V m Re 2.8 ge – Minimu ut Volta 3.8 – VI – Inp 2.8 VI 2 1.5 1.75 2 2.25 2.5 2.75 3 3.25 3.5 0 50 100 150 200 250 300 350 400 450 500 VO – Output Voltage – V t – Time – µs Figure 12 Figure 13 10 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 TYPICAL CHARACTERISTICS TPS75515 TPS75533 LOAD TRANSIENT RESPONSE LINE TRANSIENT RESPONSE Output Voltage – mV 115050000 CVOo == 110.50 VµF Output Voltage – mV 1–5050000 VICOOo = == 5 13 0A.30 VµF ∆– Change in VO–––11550000 ddti(cid:1)1.2µ5sA 5 put Current – A ∆– Change in VO–100 5.3 ut Voltage – V ut p 0 – O 4.3 – In I O VI 0 20 40 60 80 100 120 140 160 180 200 0 50 100 150 200 250 300 350 400 450 500 t – Time – µs t – Time – µs Figure 14 Figure 15 TPS75533 OUTPUT VOLTAGE AND ENABLE VOLTAGE TPS75533 vs LOAD TRANSIENT RESPONSE TIME (START-UP) e – mV CVOo == 31 0.30 VµF ge – V 3.3 VIOI == 41.03 mVA ut Voltag 200 put Volta TJ = 25°C utp 100 Out n O – O e i 0 V 0 g A ∆– ChanVO–100 ddti(cid:1)1.2µ5sA 5 ut Current – oltage – V 4.03 p V ut e 0 O bl – a I O En 0 20 40 60 80 100 120 140 160 180 200 0 0.2 0.4 0.6 0.8 1 t – Time – µs t – Time (Start-Up) – ms Figure 16 Figure 17 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 11

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 TYPICAL CHARACTERISTICS To Load VI IN OUT + Co RL EN GND ESR Figure 18. Test Circuit for Typical Regions of Stability (Figures 19 and 20) (Fixed Output Options) TYPICAL REGION OF STABILITY TYPICAL REGION OF STABILITY EQUIVALENT SERIES RESISTANCE† EQUIVALENT SERIES RESISTANCE† vs vs OUTPUT CURRENT OUTPUT CURRENT 10 10 Ωce – CTJo = = 2 658°C0 µF Ωe – CTJo == 2457° CµF n c a n esist sista R 1 e 1 es Region of Stability s R Region of Stability eri rie S e ent nt S val ale 0.2 qui 0.1 uiv E q SR – R – E Region of Instability E S E 0.015 Region of Instability 0.01 0.01 0 1 2 3 4 5 0 1 2 3 4 5 IO – Output Current – A IO – Output Current – A Figure 19 Figure 20 †Equivalent series resistance (ESR) refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistance to Co. 12 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 THERMAL INFORMATION The amount of heat that an LDO linear regulator generates is directly proportional to the amount of power it dissipates during operation. All integrated circuits have a maximum allowable junction temperature (T max) J above which normal operation is not assured. A system designer must design the operating environment so that the operating junction temperature (T ) does not exceed the maximum junction temperature (T max). The J J two main environmental variables that a designer can use to improve thermal performance are air flow and external heatsinks. The purpose of this information is to aid the designer in determining the proper operating environment for a linear regulator that is operating at a specific power level. In general, the maximum expected power (P ) consumed by a linear regulator is computed as: D(max) (cid:2) (cid:4) P max(cid:1) V (cid:6)V (cid:5)I (cid:7) V xI (1) D I(avg) O(avg) O(avg) I(avg) (Q) Where: V is the average input voltage. I(avg) V is the average output voltage. O(avg) I is the average output current. O(avg) I is the quiescent current. (Q) For most TI LDO regulators, the quiescent current is insignificant compared to the average output current; therefore, the term V x I can be neglected. The operating junction temperature is computed by adding I(avg) (Q) the ambient temperature (T ) and the increase in temperature due to the regulator’s power dissipation. The A temperature rise is computed by multiplying the maximum expected power dissipation by the sum of the thermal resistances between the junction and the case (RθJC), the case to heatsink (RθCS), and the heatsink to ambient (RθSA). Thermal resistances are measures of how effectively an object dissipates heat. Typically, the larger the device, the more surface area available for power dissipation and the lower the object’s thermal resistance. Figure 21 illustrates these thermal resistances for (a) a TO–220 package attached to a heatsink, and (b) a TO–263 package mounted on a JEDEC High-K board. C B A TJ A RθJC A B B TC RθCS C RθSA C TO–263 Package TA (b) TO–220 Package (a) Figure 21. Thermal Resistances POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 13

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 THERMAL INFORMATION Equation 2 summarizes the computation: (cid:2) (cid:4) T (cid:1) T (cid:7)P maxx R (cid:7) R (cid:7) R (2) J A D θJC θCS θSA The RθJC is specific to each regulator as determined by its package, lead frame, and die size provided in the regulator’s datasheet. The RθSA is a function of the type and size of heatsink. For example, black body radiator type heatsinks, like the one attached to the TO–220 package in Figure 21(a), can have RθCS values ranging from 5°C/W for very large heatsinks to 50°C/W for very small heatsinks. The RθCS is a function of how the package is attached to the heatsink. For example, if a thermal compound is used to attach a heatsink to a TO–220 package, RθCS of 1°C/W is reasonable. Even if no external black body radiator type heatsink is attached to the package, the board on which the regulator is mounted will provide some heatsinking through the pin solder connections. Some packages, like the TO–263 and TI’s TSSOP PowerPAD packages, use a copper plane underneath the package or the circuit board’s ground plane for additional heatsinking to improve their thermal performance. Computer aided thermal modeling can be used to compute very accurate approximations of an integrated circuit’s thermal performance in different operating environments (e.g., different types of circuit boards, different types and sizes of heatsinks, and different air flows, etc.). Using these models, the three thermal resistances can be combined into one thermal resistance between junction and ambient (RθJA). This RθJA is valid only for the specific operating environment used in the computer model. Equation 2 simplifies into equation 3: TJ (cid:1) TA(cid:7)PDmaxx RθJA (3) Rearranging equation 3 gives equation 4: T –T R (cid:1) J A (4) θJA P max D Using equation 3 and the computer model generated curves shown in Figures 22 and 25, a designer can quickly compute the required heatsink thermal resistance/board area for a given ambient temperature, power dissipation, and operating environment. PowerPAD is a trademark of Texas Instruments. 14 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 THERMAL INFORMATION TO–220 power dissipation The TO–220 package provides an effective means of managing power dissipation in through-hole applications. The TO–220 package dimensions are provided in the Mechanical Data section at the end of the data sheet. A heatsink can be used with the TO–220 package to effectively lower the junction-to-ambient thermal resistance. To illustrate, the TPS75525 in a TO–220 package was chosen. For this example, the average input voltage is 3.3 V, the output voltage is 2.5 V, the average output current is 3 A, the ambient temperature 55°C, the air flow is 150 LFM, and the operating environment is the same as documented below. Neglecting the quiescent current, the maximum average power is: P max (cid:1) (3.3–2.5)Vx3A (cid:1) 2.4W (5) D Substituting T max for T into equation 4 gives equation 6: J J RθJAmax (cid:1) (125–55)°C(cid:3)2.4W (cid:1) 29°C(cid:3)W (6) From Figure 22, RθJA vs Heatsink Thermal Resistance, a heatsink with RθSA = 22°C/W is required to dissipate 2.4 W. The model operating environment used in the computer model to construct Figure 22 consisted of a standard JEDEC High-K board (2S2P) with a 1 oz. internal copper plane and ground plane. Since the package pins were soldered to the board, 450 mm2 of the board was modeled as a heatsink. Figure 23 shows the side view of the operating environment used in the computer model. THERMAL RESISTANCE vs HEATSINK THERMAL RESISTANCE 65 Natural Convection W 55 C/ ° – Air Flow = 150 LFM e 45 nc Air Flow = 250 LFM a st Air Flow = 500 LFM esi 35 R al m er 25 h T – A J 15 θ R No Heatsink 5 25 20 15 10 5 0 RθSA – Heatsink Thermal Resistance – °C/W Figure 22 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 15

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 THERMAL INFORMATION TO–220 power dissipation (continued) 0.21 mm 0.21 mm 1 oz. Copper 1 oz. Copper Power Plane Ground Plane Figure 23 From the data in Figure 22 and rearranging equation 4, the maximum power dissipation for a different heatsink RθSA and a specific ambient temperature can be computed (see Figure 24). POWER DISSIPATION vs HEATSINK THERMAL RESISTANCE 10 TA = 55°C W Air Flow = 500 LFM – mit Air Flow = 250 LFM Li n o ati Air Flow = 150 LFM p si s Di r e w o P – D P Natural Convection No Heatsink 1 20 10 0 RθSA – Heatsink Thermal Resistance – °C/W Figure 24 16 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 THERMAL INFORMATION TO–263 power dissipation The TO–263 package provides an effective means of managing power dissipation in surface mount applications. The TO–263 package dimensions are provided in the Mechanical Data section at the end of the data sheet. The addition of a copper plane directly underneath the TO–263 package enhances the thermal performance of the package. To illustrate, the TPS75525 in a TO–263 package was chosen. For this example, the average input voltage is 3.3 V, the output voltage is 2.5 V, the average output current is 3 A, the ambient temperature 55°C, the air flow is 150 LFM, and the operating environment is the same as documented below. Neglecting the quiescent current, the maximum average power is: P max (cid:1) (3.3–2.5)Vx3A (cid:1) 2.4W (7) D Substituting T max for T into equation 4 gives equation 8: J J RθJAmax (cid:1) (125–55)°C(cid:3)2.4W (cid:1) 29°C(cid:3)W (8) From Figure 25, RθJA vs Copper Heatsink Area, the ground plane needs to be 2 cm2 for the part to dissipate 2.4 W. The model operating environment used in the computer model to construct Figure 25 consisted of a standard JEDEC High-K board (2S2P) with a 1 oz. internal copper plane and ground plane. The package is soldered to a 2 oz. copper pad. The pad is tied through thermal vias to the 1 oz. ground plane. Figure 26 shows the side view of the operating environment used in the computer model. THERMAL RESISTANCE vs COPPER HEATSINK AREA 40 No Air Flow W C/ 35 ° – e 150 LFM c n a st 30 si e R 250 LFM al m r 25 e h T – A J Rθ 20 15 0 0.01 0.1 1 10 100 Copper Heatsink Area – cm2 Figure 25 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 17

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 THERMAL INFORMATION TO–263 power dissipation (continued) 2 oz. Copper Solder Pad with 25 Thermal Vias 1 oz. Copper Power Plane 1 oz. Copper Ground Plane Thermal Vias, 0.3 mm Diameter, 1.5 mm Pitch Figure 26 From the data in Figure 25 and rearranging equation 4, the maximum power dissipation for a different ground plane area and a specific ambient temperature can be computed (see Figure 27). MAXIMUM POWER DISSIPATION vs COPPER HEATSINK AREA 5 TA = 55°C W – n atio 4 250 LFM p si s Di r 150 LFM e w 3 o P m u m xi No Air Flow a M 2 – D P 1 0 0.01 0.1 1 10 100 Copper Heatsink Area – cm2 Figure 27 18 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 APPLICATION INFORMATION programming the TPS75501 adjustable LDO regulator The output voltage of the TPS75501 adjustable regulator is programmed using an external resistor divider as shown in Figure 28. The output voltage is calculated using: (cid:2) (cid:4) V (cid:1)V (cid:5) 1(cid:7)R1 (9) O ref R2 Where: V = 1.224 V typ (the internal reference voltage) ref Resistors R1 and R2 should be chosen for approximately 40-µA divider current. Lower value resistors can be used but offer no inherent advantage and waste more power. Higher values should be avoided as leakage currents at FB increase the output voltage error. The recommended design procedure is to choose R2 = 30.1kΩ to set the divider current at 40 µA and then calculate R1 using: (cid:2) (cid:4) V R1(cid:1) O (cid:6)1 (cid:5)R2 (10) V ref TPS75501 OUTPUT VOLTAGE PROGRAMMING GUIDE VI IN 1 µF OUTPUT ≥2 V VOLTAGE R1 R2 UNIT EN OUT VO 2.5 V 31.6 30.1 kΩ ≤0.7 V R1 Co 3.3 V 51 30.1 kΩ FB 3.6 V 58.3 30.1 kΩ GND R2 Figure 28. TPS75501 Adjustable LDO Regulator Programming regulator protection The TPS755xx PMOS-pass transistor has a built-in back diode that conducts reverse currents when the input voltage drops below the output voltage (e.g., during power down). Current is conducted from the output to the input and is not internally limited. When extended reverse voltage is anticipated, external limiting may be appropriate. The TPS755xx also features internal current limiting and thermal protection. During normal operation, the TPS755xx limits output current to approximately 10 A. When current limiting engages, the output voltage scales back linearly until the overcurrent condition ends. While current limiting is designed to prevent gross device failure, care should be taken not to exceed the power dissipation ratings of the package. If the temperature of the device exceeds 150°C(typ), thermal-protection circuitry shuts it down. Once the device has cooled below 130°C(typ), regulator operation resumes. POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 19

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 APPLICATION INFORMATION input capacitor For a typical application, a ceramic input bypass capacitor (0.22 µF–1 µF) is recommended to ensure device stability. This capacitor should be as close as possible to the input pin. Due to the impedance of the input supply, large transient currents will cause the input voltage to droop. If this droop causes the input voltage to drop below the UVLO threshold, the device will turn off. Therefore, it is recommended that a larger capacitor be placed in parallel with the ceramic bypass capacitor at the regulator’s input. The size of this capacitor depends on the output current, response time of the main power supply, and the main power supply’s distance to the regulator. At a minimum, the capacitor should be sized to ensure that the input voltage does not drop below the minimum UVLO threshold voltage during normal operating conditions. output capacitor As with most LDO regulators, the TPS755xx requires an output capacitor connected between OUT and GND to stabilize the internal control loop. The minimum recommended capacitance value is 47 µF with an ESR (equivalent series resistance) of at least 200 mΩ. As shown in Figure 29, most capacitor and ESR combinations with a product of 47e–6 x 0.2 = 9.4e–6 or larger will be stable, provided the capacitor value is at least 47 µF. Solid tantalum electrolytic and aluminum electrolytic capacitors are all suitable, provided they meet the requirements described in this section. Larger capacitors provide a wider range of stability and better load transient response. This information along with the ESR graphs, Figures 19, 20, and 29, is included to assist in selection of suitable capacitance for the user’s application. When necessary to achieve low height requirements along with high output current and/or high load capacitance, several higher ESR capacitors can be used in parallel to meet these guidelines. OUTPUT CAPACITANCE vs EQUIVALENT SERIES RESISTANCE 1000 Region of Stability F µ – e c n a cit ESR min x Co = Constant pa 100 a C ut p ut 47 O Region of Instability Y = ESRmin x Co 10 0.01 0.1 0.2 ESR – Equivalent Series Resistance – Ω Figure 29 20 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 MECHANICAL DATA KC (R-PSFM-T5) PLASTIC FLANGE-MOUNT 0.420 (10,67) 0.113 (2,87) 0.185 (4,70) 0.156 (3,96) DIA 0.380 (9,65) 0.103 (2,62) 0.175 (4,46) 0.146 (3,71) 0.055 (1,40) 0.045 (1,14) 0.147 (3,73) 0.137 (3,48) 0.340 (8,64) 0.330 (8,38) 1 5 1.010 (25,64) 0.125 (3,18) 0.990 (25,14) (see Note C) 0.040 (1,02) 0.122 (3,10) 0.067 (1,70) 0.030 (0,76) 0.102 (2,59) 0.010 (0,25) M 0.268 (6,81) 0.025 (0,64) 0.012 (0,30) 4040208/D 01/00 NOTES: A. All linear dimensions are in inches (millimeters). B. This drawing is subject to change without notice. C. Lead dimensions are not controlled within this area. D. All lead dimensions apply before solder dip. E. The center lead is in electrical contact with the mounting tab. POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 21

TPS75515, TPS75518, TPS75525, TPS75533 WITH POWER GOOD AND TPS75501 FAST-TRANSIENT RESPONSE 5-A LOW-DROPOUT VOLTAGE REGULATORS SLVS293D – NOVEMBER 2000 – REVISED MAY 2002 MECHANICAL DATA KTT (R-PSFM-G5) PLASTIC FLANGE-MOUNT 0.405 (10,29) 0.058 (1,47) 0.185 (4,70) 0.395 (10,03) 0.052 (1,32) 0.175 (4,45) 0.050 (1,27) NOM 0.107 (2,72) 0.610 (15,49) 0.340 (8,64) 0.103 (2,62) 0.590 (14,99) 0.330 (8,38) 0.010 (0,25) 0.001 (0,03) 1 5 Seating Plane 0.035 (0,89) 0.067 (1,70) 0.004 (0,10) 0.029 (0,74) 0.268 (6,81) 0.010 (0,25) M 0.021 (0,53) 0.110 (2,79) 0.015 (0,38) 0.090 (2,29) 0°–(cid:2)(cid:3)° 4200577/A 09/99 NOTES: A. All linear dimensions are in inches (millimeters). B. This drawing is subject to change without notice. C. Dimensions do not include mold protrusions, not to exceed 0.006 (0,15). 22 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

IMPORTANT NOTICE Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed. TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards. TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI. Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Mailing Address: Texas Instruments Post Office Box 655303 Dallas, Texas 75265 Copyright 2003, Texas Instruments Incorporated

Datasheet下载

Datasheet下载