- 型号: HCF4099M013TR

- 制造商: STMicroelectronics

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

HCF4099M013TR产品简介:

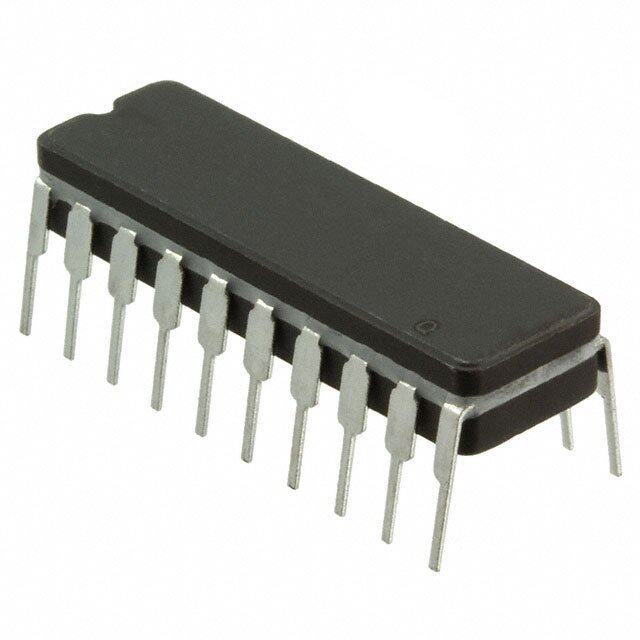

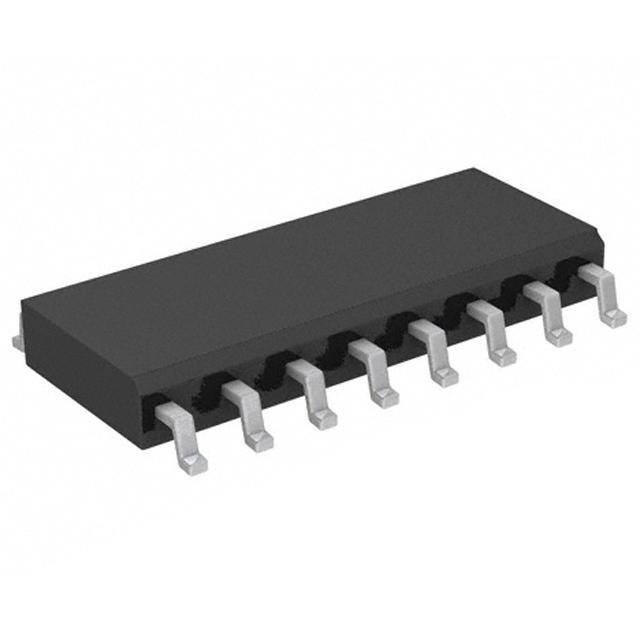

ICGOO电子元器件商城为您提供HCF4099M013TR由STMicroelectronics设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 HCF4099M013TR价格参考。STMicroelectronicsHCF4099M013TR封装/规格:逻辑 - 锁销, D-Type, Addressable 1 Channel 1:8 IC Standard 16-SO。您可以下载HCF4099M013TR参考资料、Datasheet数据手册功能说明书,资料中有HCF4099M013TR 详细功能的应用电路图电压和使用方法及教程。

HCF4099M013TR 是由 STMicroelectronics(意法半导体)生产的一款逻辑电路,属于锁存器/触发器类别。其应用场景主要包括以下几个方面: 1. 数据存储与信号处理: HCF4099M013TR 是一种 CMOS 工艺的数字逻辑器件,通常用于数据存储和信号处理。它可以通过时钟信号控制输入数据的锁存,适用于需要同步数据传输或暂存的场景,例如数据缓冲、寄存器文件或状态机设计。 2. 工业控制系统: 在工业自动化领域,该芯片可用于实现信号的同步与隔离。例如,在 PLC(可编程逻辑控制器)或传感器接口中,它可以用来锁存输入信号,确保信号的稳定性和准确性。 3. 通信设备: 在通信系统中,HCF4099M013TR 可以用作数据同步器或移位寄存器的一部分,帮助实现串行到并行或并行到串行的数据转换,适用于 UART(通用异步收发传输器)或其他通信协议的实现。 4. 消费电子: 在家用电器或消费电子产品中,该芯片可以用于按键输入的去抖动处理或 LED 显示驱动的信号控制。通过锁存功能,它可以有效减少外部干扰对系统的影响。 5. 汽车电子: 由于其低功耗特性和宽工作电压范围,HCF4099M013TR 也可应用于汽车电子系统中,例如车灯控制、仪表盘显示或传感器信号处理等场景。 6. 测试与测量设备: 在测试仪器中,该芯片可以用来锁存测量结果或控制信号,确保数据采集的精确性和稳定性。 总之,HCF4099M013TR 的主要应用场景集中在需要数据锁存、信号同步或简单逻辑控制的领域,广泛适用于工业、通信、消费电子及汽车等行业。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC LATCH 8BIT ADDRESSABLE 16SOIC |

| 产品分类 | |

| 品牌 | STMicroelectronics |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | HCF4099M013TR |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 4000B |

| 产品目录页面 | |

| 供应商器件封装 | 16-SO |

| 其它名称 | 497-1143-1 |

| 其它有关文件 | http://www.st.com/web/catalog/sense_power/FM140/SC1798/PF63066?referrer=70071840 |

| 包装 | 剪切带 (CT) |

| 安装类型 | 表面贴装 |

| 封装/外壳 | 16-SOIC(0.154",3.90mm 宽) |

| 工作温度 | -55°C ~ 125°C |

| 延迟时间-传播 | 50ns |

| 标准包装 | 1 |

| 独立电路 | 1 |

| 电压-电源 | 3 V ~ 20 V |

| 电流-输出高,低 | 6.8mA,6.8mA |

| 电路 | 1:8 |

| 输出类型 | 标准 |

| 逻辑类型 | D 型,可寻址 |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

HCF4099B 8 BIT ADDRESSABLE LATCH n SERIAL DATA INPUT - ACTIVE PARALLEL OUTPUT n STORAGE REGISTER CAPABILITY - MASTER CLEAR n CAN FUNCTION AS DEMULTIPLEXER n QUIESCENT CURRENT SPECIFIED UP TO 20V DIP SOP n STANDARDIZED SYMMETRICAL OUTPUT CHARACTERISTICS n INPUT LEAKAGE CURRENT ORDER CODES I = 100nA (MAX) AT V = 18V T = 25°C I DD A PACKAGE TUBE T & R n 100% TESTED FOR QUIESCENT CURRENT DIP HCF4099BEY n MEETS ALL REQUIREMENTS OF JEDEC SOP HCF4099BM1 HCF4099M013TR JESD13B "STANDARD SPECIFICATIONS FOR DESCRIPTION OF B SERIES CMOS DEVICES" WRITE DISABLE is high, data entry is inhibited; DESCRIPTION however, all 8 outputs can be continuously read HCF4099B is a monolithic integrated circuit independent of WRITE DISABLE and address fabricated in Metal Oxide Semiconductor inputs. A master RESET input is available, which technology available in DIP and SOP packages. resets all bits to a logic "0" level when RESET and HCF4099B, an 8-bit addressable latch, is a WRITE DISABLE are at a high level. When serial-input, parallel output storage register that RESET is at a high level, and WRITE DISABLE is can perform a variety of functions. Data is input to at a low level, the latch acts as a 1-of-8 a particular bit in the latch when that bit is demultiplexer ; the bit that is addressed has an addressed (by means of input A0, A1, A2) and active output which follows the data input, while all when WRITE DISABLE is at a low level. When unaddressed bits are held to a logic "0" level. PIN CONNECTION October 2002 1/14

HCF4099B IINPUT EQUIVALENT CIRCUIT PIN DESCRIPTION PIN No SYMBOL NAME AND FUNCTION 5, 6, 7 A0 to A2 Address Inputs 9, 10, 11, 12, Q0 to Q7 Latch Outputs 13, 14, 15, 1 3 DATA Data Inputs 2 RESET Reset Input WRITE 4 Write Disable Input DISABLE 8 VSS Negative Supply Voltage 16 VDD Positive Supply Voltage FUNCTIONAL DIAGRAM TRUTH TABLE SELECT INPUTS LATCH ADDRESSED C B A L L L Q0 L L H Q1 L H L Q2 L H H Q3 H L L Q4 H L H Q5 H H L Q6 H H H Q7 INPUTS OUTPUTS OF EACH OTHER ADDRESSED FUNCTION OUTPUT WRITE DISABLE RESET LATCH L L D Qi0 ADDRESSABLE LATCH L H Qi0 Qi0 MEMORY H L D L DEMULTIPLEXER H H L L CLEAR ALL BITS TO "0" D: The level at the data input ; Q The level before the indicated steady state input conditions were established, (i=0, 1,...7) i0 2/14

HCF4099B LOGIC DIAGRAM TIMING CHART 3/14

HCF4099B ABSOLUTE MAXIMUM RATINGS Symbol Parameter Value Unit VDD Supply Voltage -0.5 to +22 V VI DC Input Voltage -0.5 to VDD + 0.5 V II DC Input Current – 10 mA P Power Dissipation per Package 200 mW D Power Dissipation per Output Transistor 100 mW Top Operating Temperature -55 to +125 °C Tstg Storage Temperature -65 to +150 °C Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All voltage values are referred to V pin voltage. SS RECOMMENDED OPERATING CONDITIONS Symbol Parameter Value Unit VDD Supply Voltage 3 to 20 V VI Input Voltage 0 to VDD V Top Operating Temperature -55 to 125 °C 4/14

HCF4099B DC SPECIFICATIONS Test Conditions Value Symbol Parameter V V ‰ I ‰ V TA = 25°C -40 to 85°C -55 to 125°C Unit I O O DD (V) (V) (m A) (V) Min. Typ. Max. Min. Max. Min. Max. I Quiescent Current 0/5 5 0.04 5 150 150 L 0/10 10 0.04 10 300 300 m A 0/15 15 0.04 20 600 600 0/20 20 0.08 100 3000 3000 V High Level Output 0/5 <1 5 4.95 4.95 4.95 OH Voltage 0/10 <1 10 9.95 9.95 9.95 V 0/15 <1 15 14.95 14.95 14.95 V Low Level Output 5/0 <1 5 0.05 0.05 0.05 OL Voltage 10/0 <1 10 0.05 0.05 0.05 V 15/0 <1 15 0.05 0.05 0.05 V High Level Input 0.5/4.5 <1 5 3.5 3.5 3.5 IH Voltage 1/9 <1 10 7 7 7 V 1.5/18.5 <1 15 11 11 11 V Low Level Input 0.5/4.5 <1 5 1.5 1.5 1.5 IL Voltage 9/1 <1 10 3 3 3 V 1.5/18.5 <1 15 4 4 4 I Output Drive 0/5 2.5 5 -1.36 -3.2 -1.1 -1.1 OH Current 0/5 4.6 5 -0.44 -1 -0.36 -0.36 mA 0/10 9.5 10 -1.1 -2.6 -0.9 -0.9 0/15 13.5 15 -3.0 -6.8 -2.4 -2.4 I Output Sink 0/5 0.4 5 0.44 1 0.36 0.36 OL Current 0/10 0.5 10 1.1 2.6 0.9 0.9 mA 0/15 1.5 15 3.0 6.8 2.4 2.4 I Input Leakage I 0/18 any input 18 – 10-5 – 0.1 – 1 – 1 m A Current CI Input Capacitance any input 5 7.5 pF The Noise Margin for both "1" and "0" level is: 1V min. with V =5V, 2V min. with V =10V, 2.5V min. with V =15V DD DD DD 5/14

HCF4099B DYNAMIC ELECTRICAL CHARACTERISTICS (T = 25°C, C = 50pF, R = 200KW , t = t = 20 ns) amb L L r f Test Condition Value (*) Unit Symbol Parameter VDD (V) See Timing Chart Min. Typ. Max. t t Propagation Delay Time 5 200 400 PLH PHL (Data to Output) 10 (1) 75 150 ns 15 50 100 t t Propagation Delay Time 5 200 400 PLH PHL (Write Disable to Output) 10 (2) 80 160 ns 15 60 120 t t Propagation Delay Time 5 225 450 PLH PHL (Address to Output) 10 (9) 100 200 ns 15 75 150 t Propagation Delay Time 5 175 350 PHL (Reset to Output) 10 (3) 80 160 ns 15 65 130 t t Transition Time 5 100 200 THL TLH (any output) 10 50 100 ns 15 40 80 t Pulse WIdth (Data) 5 200 100 W 10 (4) 100 50 ns 15 80 40 t Pulse WIdth (Address) 5 400 200 W 10 (8) 200 100 ns 15 125 65 t Pulse WIdth (Reset) 5 150 75 W 10 (5) 75 40 ns 15 50 25 t Setup Time 5 100 50 setup (Data to Write Disable) 10 (6) 50 25 ns 15 35 20 t Hold Time 5 150 75 hold (Data to Write Disable) 10 (7) 75 40 ns 15 50 25 (*) Typical temperature coefficient for all V value is 0.3 %/°C. DD 6/14

HCF4099B TEST CIRCUIT C = 50pF or equivalent (includes jig and probe capacitance) L R = 200KW L R = Z of pulse generator (typically 50W ) T OUT WAVEFORM 1 : PROPAGATION DELAY TIME (f=1MHz; 50% duty cycle) 7/14

HCF4099B WAVEFORM 2 : PROPAGATION DELAY TIME (f=1MHz; 50% duty cycle) WAVEFORM 3 : MINIMUM PULSE WIDTH, SETUP AND HOLD TIME (f=1MHz; 50% duty cycle) 8/14

HCF4099B WAVEFORM 4 : MINIMUM PULSE WIDTH (f=1MHz; 50% duty cycle) WAVEFORM 5 : SETUP AND HOLD TIME (f=1MHz; 50% duty cycle) 9/14

HCF4099B WAVEFORM 6 : INPUT WAVEFORMS (f=1MHz; 50% duty cycle) TIPICAL APPLICATIONS 10/14

HCF4099B TIPICAL APPLICATIONS 11/14

HCF4099B Plastic DIP-16 (0.25) MECHANICAL DATA mm. inch DIM. MIN. TYP MAX. MIN. TYP. MAX. a1 0.51 0.020 B 0.77 1.65 0.030 0.065 b 0.5 0.020 b1 0.25 0.010 D 20 0.787 E 8.5 0.335 e 2.54 0.100 e3 17.78 0.700 F 7.1 0.280 I 5.1 0.201 L 3.3 0.130 Z 1.27 0.050 P001C 12/14

HCF4099B SO-16 MECHANICAL DATA mm. inch DIM. MIN. TYP MAX. MIN. TYP. MAX. A 1.75 0.068 a1 0.1 0.2 0.003 0.007 a2 1.65 0.064 b 0.35 0.46 0.013 0.018 b1 0.19 0.25 0.007 0.010 C 0.5 0.019 c1 45˚ (typ.) D 9.8 10 0.385 0.393 E 5.8 6.2 0.228 0.244 e 1.27 0.050 e3 8.89 0.350 F 3.8 4.0 0.149 0.157 G 4.6 5.3 0.181 0.208 L 0.5 1.27 0.019 0.050 M 0.62 0.024 S 8˚ (max.) PO13H 13/14

HCF4099B Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics. © The ST logo is a registered trademark of STMicroelectronics © 2002 STMicroelectronics - Printed in Italy - All Rights Reserved STMicroelectronics GROUP OF COMPANIES Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom - United States. © http://www.st.com 14/14

Datasheet下载

Datasheet下载