- 型号: ESD7104MUTAG

- 制造商: ON Semiconductor

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ESD7104MUTAG产品简介:

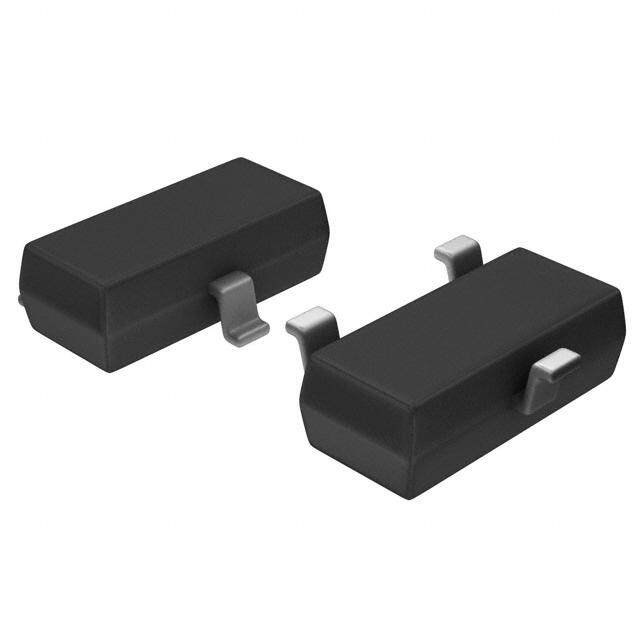

ICGOO电子元器件商城为您提供ESD7104MUTAG由ON Semiconductor设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 ESD7104MUTAG价格参考¥1.84-¥1.84。ON SemiconductorESD7104MUTAG封装/规格:TVS - 二极管, 。您可以下载ESD7104MUTAG参考资料、Datasheet数据手册功能说明书,资料中有ESD7104MUTAG 详细功能的应用电路图电压和使用方法及教程。

ESD7104MUTAG 是安森美半导体(ON Semiconductor)生产的一款瞬态电压抑制(TVS)二极管,主要用于保护电子设备免受静电放电(ESD)、浪涌电压和其它瞬态干扰的损害。 主要应用场景包括: 1. 便携式电子产品:如智能手机、平板电脑、笔记本电脑等,用于保护USB接口、HDMI接口、音频接口等高速数据线路,防止静电损坏敏感IC。 2. 通信设备:在以太网接口、RS-485、CAN总线等通信端口中提供线路保护,确保信号完整性并提高系统可靠性。 3. 工业控制系统:用于PLC、传感器、人机界面等设备中,抵御工业环境中常见的电磁干扰和静电冲击。 4. 汽车电子系统:应用于车载信息娱乐系统、摄像头模块、控制单元等,满足汽车行业对高可靠性和抗干扰能力的要求。 5. 消费类家电:如智能电视、机顶盒、智能家居控制器等,保护按键、显示屏接口及外部连接端口。 该器件采用小型化封装(如TSOP),具有低钳位电压、响应速度快、低漏电流等特点,适合用于空间受限且对性能要求较高的应用场合。

| 参数 | 数值 |

| 产品目录 | |

| 描述 | TVS DIODE 5VWM 10VC 10UDFNTVS二极管阵列 BI-DIRECTIONAL 4 LINE TVS |

| 产品分类 | |

| 品牌 | ON Semiconductor |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | 二极管与整流器,TVS二极管,TVS二极管阵列,ON Semiconductor ESD7104MUTAG- |

| 数据手册 | |

| 产品型号 | ESD7104MUTAG |

| PCN组件/产地 | |

| 不同频率时的电容 | 0.3pF @ 1MHz |

| 产品种类 | TVS二极管阵列 |

| 供应商器件封装 | 10-UDFN(2.5x1) |

| 其它名称 | ESD7104MUTAG-ND |

| 击穿电压 | 5.5 V |

| 功率-峰值脉冲 | - |

| 包装 | 带卷 (TR) |

| 单向通道 | 4 |

| 双向通道 | - |

| 商标 | ON Semiconductor |

| 外壳高度 | 0.4 mm |

| 安装类型 | 表面贴装 |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | 10-UFDFN |

| 封装/箱体 | UDFN-10 |

| 尺寸 | 1 mm W x 2.5 mm L x 0.55 m H |

| 工作温度 | -55°C ~ 125°C |

| 工作电压 | 5 V |

| 工厂包装数量 | 3000 |

| 应用 | 通用 |

| 最大工作温度 | + 125 C |

| 最小工作温度 | - 55 C |

| 极性 | Unidirectional |

| 标准包装 | 3,000 |

| 电压-击穿(最小值) | 5.5V |

| 电压-反向关态(典型值) | 5V |

| 电压-箝位(最大值)@Ipp | 10V |

| 电容 | 0.3 pF |

| 电流-峰值脉冲(10/1000µs) | 1A (8/20µs) |

| 电源线路保护 | 无 |

| 端接类型 | SMD/SMT |

| 类型 | 齐纳 |

| 系列 | ESD7104 |

| 通道 | 4 Channels |

| 钳位电压 | 10 V |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

ESD7104 ESD Protection Diode Low Capacitance ESD Protection Diode for High Speed Data Line The ESD7104 surge protection is designed to protect high speed data lines from ESD. Ultra−low capacitance and low ESD clamping www.onsemi.com voltage make this device an ideal solution for protecting voltage sensitive high speed data lines. The flow−through style package MARKING allows for easy PCB layout and matched trace lengths necessary to DIAGRAM maintain consistent impedance between high speed differential lines UDFN10 7M M(cid:2) such as USB 3.0 and HDMI. CASE 517BB (cid:2) Features • 7M = Specific Device Code (tbd) Low Capacitance (0.3 pF Typical, I/O to GND) M = Date Code • Low ESD Clamping Voltage (cid:2) = Pb−Free Package • Protection for the Following IEC Standards: (Note: Microdot may be in either location) IEC 61000−4−2 (Level 4) • UL Flammability Rating of 94 V−0 WDFNW10 • XXX M SZESD7104MTWTAG − Wettable Flank Package for optimal CASE 515AH Automated Optical Inspection (AOI) • SZ Prefix for Automotive and Other Applications Requiring Unique XX = Specific Device Code Site and Control Change Requirements; AEC−Q101 Qualified and M = Date Code PPAP Capable • These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS PIN CONFIGURATION Compliant AND SCHEMATIC Typical Applications N/C N/C GND N/C N/C • USB 3.0 • 10 9 8 7 6 eSATA 3.0 • Thunderbolt (Light Peak) • 1 2 3 4 5 HDMI 1.3/1.4 • Display Port I/O I/O GND I/O I/O I/O I/O I/O I/O MAXIMUM RATINGS (TJ = 25°C unless otherwise noted) Pin 1 Pin 2 Pin 4 Pin 5 Rating Symbol Value Unit Operating Junction Temperature Range TJ −55 to +125 °C Storage Temperature Range Tstg −55 to +150 °C Lead Solder Temperature − TL 260 °C Maximum (10 Seconds) GND Pin 3 IEC 61000−4−2 Contact (ESD) ESD ±15 kV IEC 61000−4−2 Air (ESD) ESD ±15 kV Stresses exceeding those listed in the Maximum Ratings table may damage the = device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. See Application Note AND8308/D for further description of survivability specs. This document contains information on some products that are still under development. ORDERING INFORMATION ON Semiconductor reserves the right to change or discontinue these products without See detailed ordering, marking and shipping information in the notice. package dimensions section on page 9 of this data sheet. © Semiconductor Components Industries, LLC, 2016 1 Publication Order Number: June, 2019 − Rev. 5 ESD7104/D

ESD7104 ELECTRICAL CHARACTERISTICS (TA = 25°C unless otherwise specified) Parameter Symbol Conditions Min Typ Max Unit Reverse Working Voltage VRWM I/O Pin to GND 5.0 V Breakdown Voltage VBR IT = 1 mA, I/O Pin to GND 5.5 V Reverse Leakage Current IR VRWM = 5 V, I/O Pin to GND 1.0 (cid:2)A Clamping Voltage (Note 1) VC IPP = 1 A, I/O Pin to GND (8 x 20 (cid:2)s pulse) 10 V Clamping Voltage (Note 2) VC IEC61000−4−2, ±8 KV Contact See Figures 1 and 2 V Clamping Voltage (Note 3) VC IPP = ±8 A 14.1 V IPP = ±16 A 19.5 Junction Capacitance CJ VR = 0 V, f = 1 MHz between I/O Pins 0.2 0.3 pF Junction Capacitance CJ VR = 0 V, f = 1 MHz between I/O Pins and GND 0.3 0.35 pF Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 1. Surge current waveform per Figure 5. 2. For test procedure see Figures 3 and 4 and application note AND8307/D. 3. ANSI/ESD STM5.5.1 − 2008 Electrostatic Discharge Sensitivity Testing using Transmission Line Pulse (TLP) Model. TLP conditions: Z0 = 50 (cid:3), tp = 100 ns, tr = 4 ns, averaging window; t1 = 30 ns to t2 = 60 ns. 80 10 70 0 60 −10 50 −20 V) V) E ( 40 E ( −30 G G A A T 30 T −40 L L O O V 20 V −50 10 −60 0 −70 −10 −80 −20 0 20 40 60 80 100 120 140 −20 0 20 40 60 80 100 120 140 TIME (ns) TIME (ns) Figure 1. IEC61000−4−2 +8 KV Contact Figure 2. IEC61000−4−2 −8 KV Contact Clamping Voltage Clamping Voltage www.onsemi.com 2

ESD7104 IEC61000−4−2 Waveform IEC 61000−4−2 Spec. Ipeak First Peak Test Volt- Current Current at Current at 100% Level age (kV) (A) 30 ns (A) 60 ns (A) 90% 1 2 7.5 4 2 2 4 15 8 4 I @ 30 ns 3 6 22.5 12 6 4 8 30 16 8 I @ 60 ns 10% tP = 0.7 ns to 1 ns Figure 3. IEC61000−4−2 Spec Device Under ESD Gun Oscilloscope Test 50 (cid:2) 50 (cid:2) Cable Figure 4. Diagram of ESD Clamping Voltage Test Setup The following is taken from Application Note systems such as cell phones or laptop computers it is not AND8308/D − Interpretation of Datasheet Parameters clearly defined in the spec how to specify a clamping voltage for ESD Devices. at the device level. ON Semiconductor has developed a way to examine the entire voltage waveform across the ESD ESD Voltage Clamping protection diode over the time domain of an ESD pulse in the For sensitive circuit elements it is important to limit the form of an oscilloscope screenshot, which can be found on voltage that an IC will be exposed to during an ESD event the datasheets for all ESD protection diodes. For more to as low a voltage as possible. The ESD clamping voltage information on how ON Semiconductor creates these is the voltage drop across the ESD protection diode during screenshots and how to interpret them please refer to an ESD event per the IEC61000−4−2 waveform. Since the AND8307/D. IEC61000−4−2 was written as a pass/fail spec for larger 100 tr PEAK VALUE IRSM @ 8 (cid:2)s T 90 N E 80 PULSE WIDTH (tP) IS DEFINED R AS THAT POINT WHERE THE R U 70 PEAK CURRENT DECAY = 8 (cid:2)s C E 60 ULS 50 HALF VALUE IRSM/2 @ 20 (cid:2)s P K 40 A E P 30 F tP O 20 % 10 0 0 20 40 60 80 t, TIME ((cid:2)s) Figure 5. 8 x 20 (cid:2)s Pulse Waveform www.onsemi.com 3

ESD7104 22 −22 20 −20 18 −18 16 −16 A) 14 A) −14 NT ( 12 NT ( −12 E E R 10 R −10 R R U 8 U −8 C C 6 −6 4 −4 2 −2 0 0 0 2 4 6 8 10 12 14 16 18 20 22 24 0 −2 −4 −6 −8 −10 −12 −14 −16 −18 −20 −22 −24 VOLTAGE (V) VOLTAGE (V) Figure 6. Positive TLP I−V Curve Figure 7. Negative TLP I−V Curve Transmission Line Pulse (TLP) Measurement L S Attenuator 50 (cid:3) Coax Transmission Line Pulse (TLP) provides current versus Cable ÷ voltage (I−V) curves in which each data point is obtained from a 100 ns long rectangular pulse from a charged 50 (cid:3) Coax transmission line. A simplified schematic of a typical TLP Cable 10 M(cid:3) IM VM system is shown in Figure 8. TLP I−V curves of ESD protection devices accurately demonstrate the product’s DUT ESD capability because the 10s of amps current levels and VC under 100 ns time scale match those of an ESD event. This Oscilloscope is illustrated in Figure 9 where an 8 kV IEC 61000−4−2 current waveform is compared with TLP current pulses at Figure 8. Simplified Schematic of a Typical TLP 8 A and 16 A. A TLP I−V curve shows the voltage at which System the device turns on as well as how well the device clamps voltage over a range of current levels. Figure 9. Comparison Between 8 kV IEC 61000−4−2 and 8 A and 16 A TLP Waveforms www.onsemi.com 4

ESD7104 Without ESD With ESD7104 Figure 10. USB3.0 Eye Diagram with and without ESD7104. 5.0 Gb/s, 400 mV PP Without ESD With ESD7104 Figure 11. HDMI1.4 Eye Diagram with and without ESD7104. 3.4 Gb/s, 400 mV PP Without ESD With ESD7104 Figure 12. ESATA3.0 Eye Diagram with and without ESD7104. 6 Gb/s, 400 mV PP www.onsemi.com 5

ESD7104 4 ESD7104 IO−GND B) 2 d S ( S 0 O L N −2 O TI R −4 E S 1 IN −6 2 S −8 −10 1.E+06 1.E+07 1.E+08 1.E+09 1.E+10 FREQUENCY (Hz) Figure 13. ESD7104 Insertion Loss www.onsemi.com 6

ESD7104 USB 3.0 Type A Connector StdA_SSTX+ Vbus StdA_SSTX− ESD7104 D− ESD7L5.0 GND_DRAIN D+ StdA_SSRX+ GND StdA_SSRX− Figure 14. USB3.0 Standard A Connector Layout Diagram USB 3.0 Micro B Connector ESD7104 Vbus D− D+ ID GND ESD7104 MicB_SSTX− MicB_SSTX+ GND_DRAIN MicB_SSRX− MicB_SSRX+ Figure 15. USB3.0 Micro B Connector Layout Diagram www.onsemi.com 7

ESD7104 HDMI Type A Connector ESD7104 D2+ GND D2− D1+ GND D1− ESD7104 D0+ GND D0− CLK+ GND CLK− CEC N/C (or HEC_DAT – HDMI1.4) SCL SDA GND 5V HPD (and HEC_DAT – HDMI1.4) NUP4114 Figure 16. HDMI Layout Diagram eSATA Connector GND A+ ESD7104 A− GND B− B+ GND Figure 17. eSATA Layout Diagram www.onsemi.com 8

ESD7104 DEVICE ORDERING INFORMATION Device Marking Package Shipping† ESD7104MUTAG 7M UDFN10 3000 / Tape & Reel (Pb−Free) SZESD7104MUTAG 7M UDFN10 3000 / Tape & Reel (Pb−Free) SZESD7104MTWTAG TBD WDFNW10 3000 / Tape & Reel (In Development) (Pb−Free) †For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. www.onsemi.com 9

ESD7104 PACKAGE DIMENSIONS UDFN10 2.5 x 1, 0.5P CASE 517BB ISSUE O L L NOTES: 1. DIMENSIONING AND TOLERANCING PER D A B ASME Y14.5M, 1994. 2. CONTROLLING DIMENSION: MILLIMETERS. L1 3. DIMENSION b APPLIES TO PLATED PIN ONE DETAIL A TERMINAL AND IS MEASURED BETWEEN REFERENCE ÍÍÍ 0.15 AND 0.30mm FROM TERMINAL. E OPTIONAL 2X 0.10 C ÍÍÍ CONSTRUCTIONS MILLIMETERS DIM MIN MAX A 0.45 0.55 2X 0.10 C A1 0.00 0.05 TOP VIEW EXPOSED Cu MOLD CMPD A3 0.13 REF ÇÇÇ b 0.15 0.25 b2 0.35 0.45 DETAIL B A3 A ÇÉÇÉÇÉ A3 D 2.50 BSC 0.10 C E 1.00 BSC ÉÉÉ e 0.50 BSC L 0.30 0.40 A1 L1 --- 0.05 10X 0.08 C A1 DETAIL B OPTIONAL SIDE VIEW C SPELAATNIENG CONSTRUCTION RECOMMENDED SOLDERING FOOTPRINT* 2X b2 10X L DETAIL A 1 5 10X 2X0.45 0.50 10 6 1.30 e 8Xb 0.10 C A B PACKAGE OUTLINE BOTTOM VIEW 0.05 C NOTE 3 0.50 8X0.25 PITCH DIMENSIONS: MILLIMETERS *For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D. www.onsemi.com 10

ESD7104 PACKAGE DIMENSIONS WDFNW10 2.5x1.0, 0.5P CASE 515AH ISSUE O ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent−Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. “Typical” parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner. PUBLICATION ORDERING INFORMATION LITERATURE FULFILLMENT: N. American Technical Support: 800−282−9855 Toll Free ON Semiconductor Website: www.onsemi.com Literature Distribution Center for ON Semiconductor USA/Canada 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Europe, Middle East and Africa Technical Support: Order Literature: http://www.onsemi.com/orderlit Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada Phone: 421 33 790 2910 Fax: 303−675−2176 or 800−344−3867 Toll Free USA/Canada For additional information, please contact your local Email: orderlit@onsemi.com Sales Representative ◊ www.onsemi.com ESD7104/D 11

Mouser Electronics Authorized Distributor Click to View Pricing, Inventory, Delivery & Lifecycle Information: O N Semiconductor: ESD7104MUTAG

Datasheet下载

Datasheet下载