ICGOO在线商城 > 射频/IF 和 RFID > RF 发射器 > CC1150RSTR

- 型号: CC1150RSTR

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

CC1150RSTR产品简介:

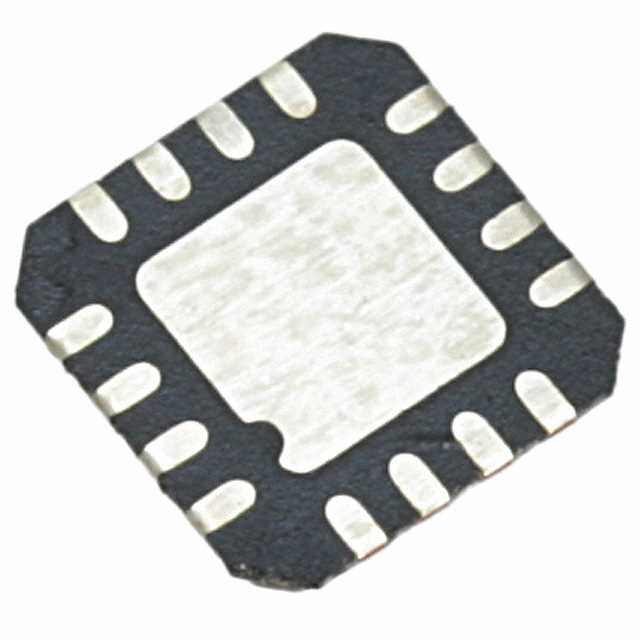

ICGOO电子元器件商城为您提供CC1150RSTR由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 CC1150RSTR价格参考。Texas InstrumentsCC1150RSTR封装/规格:RF 发射器, RF Transmitter 2-FSK, ASK, GFSK, MSK, OOK 300MHz ~ 348MHz, 400MHz ~ 464MHz, 800MHz ~ 928MHz -30dBm ~ 10dBm 500kBaud PCB, Surface Mount Antenna 16-QFN。您可以下载CC1150RSTR参考资料、Datasheet数据手册功能说明书,资料中有CC1150RSTR 详细功能的应用电路图电压和使用方法及教程。

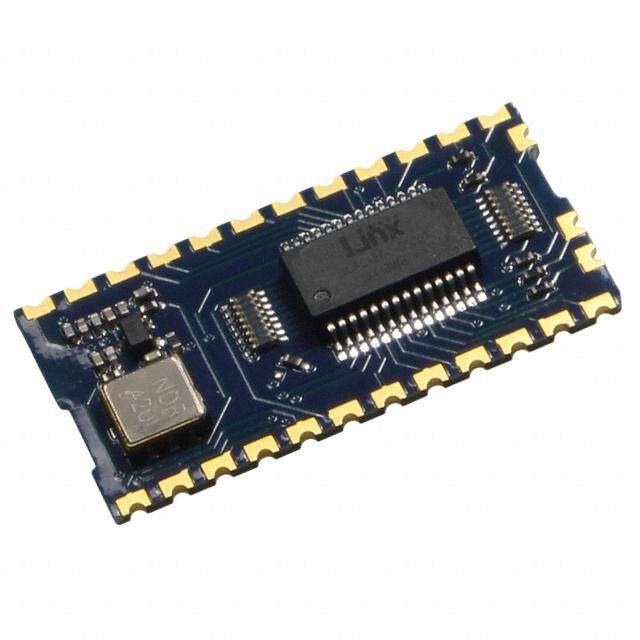

Texas Instruments(德州仪器)的CC1150RSTR是一款高性能、低功耗的RF发射器芯片,属于Sub-1 GHz无线通信解决方案。该芯片广泛应用于需要远距离、低功耗无线传输的场景。 典型应用场景包括: 1. 工业无线传感器网络:用于远程监控温度、湿度、压力等参数,适用于工厂自动化和环境监测系统。 2. 自动抄表系统(AMI):在水表、气表、电表等智能计量设备中,实现稳定可靠的无线数据上传。 3. 家庭与楼宇自动化:如无线照明控制、安防系统(门窗传感器、报警器)、智能门锁等,支持长距离穿透墙体通信。 4. 无线遥控装置:应用于车库门控制器、远程开关、遥控钥匙等消费类电子产品。 5. 农业与环境监测:部署于农田或偏远区域的无线传感节点,实现土壤湿度、气象数据的远程采集。 CC1150RSTR支持多种调制方式(如FSK、GFSK、OOK),工作频段灵活(300–348 MHz、378–486 MHz、720–820 MHz),可适应不同地区法规要求。其小尺寸QFN封装(RSTR)便于集成到紧凑型设备中,并与TI的MCU(如MSP430、CC系列)无缝配合,构建完整的低功耗无线系统。 综上,CC1150RSTR适用于对通信距离、稳定性及功耗有较高要求的中低速无线传输应用,尤其适合工业与物联网领域的远程控制与数据采集系统。

| 参数 | 数值 |

| 产品目录 | |

| 描述 | IC RF TX SNGL-CHIP LP 16-QFN射频发射器 UHF TRANSMITTER TAPE AND REEL |

| 产品分类 | |

| 品牌 | Texas Instruments |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | RF集成电路,射频发射器,Texas Instruments CC1150RSTR- |

| 数据手册 | |

| 产品型号 | CC1150RSTR |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=26085 |

| 产品目录页面 | |

| 产品种类 | 射频发射器 |

| 其它名称 | 296-19584-1 |

| 制造商产品页 | http://www.ti.com/general/docs/suppproductinfo.tsp?distId=10&orderablePartNumber=CC1150RSTR |

| 功率-输出 | -30dBm ~ 10dBm |

| 包装 | 剪切带 (CT) |

| 商标 | Texas Instruments |

| 天线连接器 | PCB,表面贴装 |

| 存储容量 | - |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | 16-QFN |

| 封装/箱体 | VQFNP-16 |

| 工作温度 | -40°C ~ 85°C |

| 工作电源电压 | 1.8 V, 2.5 V, 3.3 V |

| 工作频率 | 915 MHz |

| 工厂包装数量 | 2500 |

| 应用 | AMR,ISM,RKE,SRD |

| 数据接口 | PCB,表面贴装 |

| 数据速率(最大值) | 500 kBaud |

| 最大工作温度 | + 85 C |

| 最小工作温度 | - 40 C |

| 标准包装 | 1 |

| 特性 | - |

| 电压-电源 | 1.8 V ~ 3.6 V |

| 电流-传输 | 28.1mA @ 10 dBm |

| 类型 | Transmitter |

| 系列 | CC1150 |

| 调制或协议 | 2-FSK,ASK,GFSK,MSK,OOK |

| 配用 | /product-detail/zh/CC1150EMK-433/296-30813-ND/1690517/product-detail/zh/CC1150EMK-868/296-30814-ND/1690518 |

| 频率 | 300MHz ~ 348MHz, 400MHz ~ 464MHz, 800MHz ~ 928MHz |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Product Sample & Technical Tools & Support & Folder Buy Documents Software Community CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 CC1150 Low Power Sub-1 GHz RF Transmitter 1 Device Overview 1.1 Features 1 • SmallSize • 64-byteTXDataFIFO – QLP4-mm ×4-mmPackage,16Pins • SuitedforSystemsCompliantwithEN300220 • TrueSingleChipUHFRFTransmitter andFCCCFRPart15 • FrequencyBands • ManyPowerfulDigitalFeaturesAllowaHigh- performanceRFsystemtobemadeUsingan – 300to348MHz InexpensiveMicrocontroller – 400to464MHz • EfficientSPIinterface:AllRegistersCanbe – 800to928MHz ProgrammedWithOne"Burst"Transfer • ProgrammableDataRateUpto500kBaud • IntegratedAnalogTemperatureSensor • LowCurrentConsumption • Lead-free “Green”Package • ProgrammableOutputPowerUpto+10dBmfor • FlexibleSupportforPacketOrientedSystems AllSupportedFrequencies – On-chipSupportforSync-WordInsertion, • ProgrammableBasebandModulator FlexiblePacketLengthandAutomaticCRC • IdealForMulti-channelOperation Handling • VeryFewExternalComponents • OOKandFlexibleASKShapingSupported – CompletelyOn-chipFrequencySynthesizer • 2-FSK,GFSKandMSKSupported – NoExternalFiltersNeeded • OptionalAutomaticWhiteningofData • ConfigurablePacketHandlingHardware • SupportforAsynchronousTransparentTransmit • SuitableforFrequencyHoppingSystemsDuetoa ModeforBackwardsCompatibilitywithExisting FastSettlingFrequencySynthesizer RadioCommunicationProtocols • OptionalForwardErrorCorrectionwithInterleaving 1.2 Applications • Ultra-lowPowerUHFWirelessTransmitters • LowPowerTelemetry • Operatinginthe315-,433-,868-,and915-MHz • HomeandBuildingAutomation ISM/SRDbands • WirelessAlarmandSecuritySystems • AMR–AutomaticMeterReading • IndustrialMonitoringandControl • ConsumerElectronics • WirelessSensorNetworks • RKE– RemoteKeylessEntry 1.3 Description The CC1150 is a true single-chip UHF transmitter designed for very low power wireless applications. The circuit is mainly intended for the ISM (Industrial, Scientific and Medical) and SRD (Short Range Device) frequency bands at 315-, 433-, 868-, and 915-MHz, but can easily be programmed for operation at other frequenciesinthe300to348MHz,400to464MHzand800to928MHzbands. The RF transmitter is integrated with a highly configurable baseband modulator. The modulator supports various modulation formats and has a configurable data rate up to 500 kBaud. The CC1150 device providesextensivehardwaresupportforpackethandling,databufferingandbursttransmissions. The main operating parameters and the 64-byte transmit FIFO of CC1150 can be controlled via an SPI interface. In a typical system, the CC1150 device will be used together with a microcontroller and a few additionalpassivecomponents. CC1150 is part of the SmartRF™ technology platform based on 0.18-μm CMOS technology from Texas Instruments. 1 AnIMPORTANTNOTICEattheendofthisdatasheetaddressesavailability,warranty,changes,useinsafety-criticalapplications, intellectualpropertymattersandotherimportantdisclaimers.PRODUCTIONDATA.

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com Table1-1.DeviceInformation(1) PARTNUMBER PACKAGE BODYSIZE CC1150 VQFNP(16) 4.00mm×4.00mm (1) Formoreinformation,seeSection8,MechanicalPackagingandOrderableInformation. 1.4 Functional Block Diagram RADIOCONTROL RRFF__NP PA SFYRNETQH ODULATOR FEC/TERLEAVER PACKETHANDLER TXFIFO DIGITALNTERFACETOMCU SSSCCOISLn(KGDO1) BIAS XOSC M N I GDO0(ATEST) I RBIAS XOSC_Q1 XOSC_Q2 2 DeviceOverview Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 Table of Contents 1 DeviceOverview......................................... 1 5.7 DataRateProgramming............................ 18 .............................................. ................. 1.1 Features 1 5.8 PacketHandlingHardwareSupport 19 ........................................... ................................. 1.2 Applications 1 5.9 ModulationFormats 23 ............................................ .......... 1.3 Description 1 5.10 ForwardErrorCorrectionwithInterleaving 24 ............................ ........................................ 1.4 FunctionalBlockDiagram 2 5.11 RadioControl 26 2 Revision History......................................... 4 5.12 Data FIFO........................................... 29 3 TerminalConfigurationandFunctions.............. 5 5.13 FrequencyProgramming ........................... 31 ......................................... ................................................. 3.1 PinAttributes 5 5.14 VCO 31 4 Specifications ............................................ 6 5.15 VoltageRegulators.................................. 32 .......................... ......................... 4.1 AbsoluteMaximumRatings 6 5.16 OutputPowerProgramming 32 .......................................... .... 4.2 ESDRatings 6 5.17 GeneralPurposeandTestOutputControlPins 33 ................ .. 4.3 RecommendedOperatingConditions 6 5.18 AsynchronousandSynchronousSerialOperation 35 .............................. ............. 4.4 General Characteristics 6 5.19 SystemConsiderationsandGuidelines 36 ................................. .............................................. 4.5 CurrentConsumption 7 5.20 Memory 38 4.6 RF Transmit.......................................... 7 6 Applications,Implementation,andLayout........ 51 ..................................... .............................. 4.7 CrystalOscillator 8 6.1 ApplicationInformation 51 .............. ............................... 4.8 FrequencySynthesizerCharacteristics 8 6.2 DesignRequirements 53 ......................... ..................... 4.9 AnalogTemperatureSensor 9 6.3 PCBLayoutRecommendations 55 4.10 DCCharacteristics ................................... 9 7 DeviceandDocumentationSupport............... 58 .................................... ...................................... 4.11 Power-OnReset 10 7.1 DeviceSupport 58 4.12 ThermalResistanceCharacteristicsforVQFNP 7.2 DocumentationSupport............................. 58 ............................................. Package 10 .......................................... 7.3 Trademarks 59 5 DetailedDescription................................... 11 ..................... 7.4 ElectrostaticDischargeCaution 59 ............................................ 5.1 Overview 11 ............................... 7.5 ExportControlNotice 59 ........................... 5.2 FunctionalBlockDiagram 11 ............................................. 7.6 Glossary 59 ............................. 5.3 ConfigurationOverview 11 8 MechanicalPackagingandOrderable 5.4 ConfigurationSoftware.............................. 12 Information.............................................. 59 5.5 4-wireSerialConfigurationandDataInterface ..... 13 8.1 PackagingInformation .............................. 59 ..... 5.6 MicrocontrollerInterfaceandPinConfiguration 17 Copyright©2006–2015,TexasInstrumentsIncorporated TableofContents 3 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com 2 Revision History This data manual revision history highlights the changes made to the SWRS037A device-specific data manualtomakeitanSWRS037Brevision. ChangesfromJanuary1,2006toFebruary19,2015 Page • UpdatedRSTpackagetoRGV. .................................................................................................. 58 4 RevisionHistory Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 3 Terminal Configuration and Functions TheCC1150pinoutisshowninFigure3-1andTable3-1 D R SI DGUA RBIAS AVDD 16 15 14 13 SCLK1 12AVDD SO(GDO1)2 11RF_N DVDD3 10RF_P DCOUPL4 9 CSn GND 5 6 7 8 Exposeddie X A X G OSC VDD OSC DO0 attachpad _Q _Q (A 1 2 TE S T ) Figure3-1.PinoutTopView 3.1 Pin Attributes Table3-1.PinAttributes(1) PINNO. PINNAME TYPE DESCRIPTION 1 SCLK DigitalInput Serialconfigurationinterface,clockinput. Serialconfigurationinterface,dataoutput. 2 SO(GDO1) DigitalOutput OptionalgeneraloutputpinwhenCSnishigh. 1.8-Vto3.6-VdigitalpowersupplyfordigitalI/Osandforthedigital 3 DVDD Power(Digital) corevoltageregulator. 4 DCOUPL(2) Power(Digital) 1.6-Vto2.0-Vdigitalpowersupplyoutputfordecoupling. 5 XOSC_Q1 AnalogI/O Crystaloscillatorpin1,orexternalclockinput. 6 AVDD Power(Analog) 1.8-Vto3.6-Vanalogpowersupplyconnection. 7 XOSC_Q2 AnalogI/O Crystaloscillatorpin2. Digitaloutputpinforgeneraluse: • Testsignals GDO0 • FIFOstatussignals 8 DigitalI/O (ATEST) • Clockoutput,down-dividedfromXOSC • SerialinputTXdata AlsousedasanalogtestI/Oforprototype/productiontesting. 9 CSn DigitalInput Serialconfigurationinterface,chipselect. 10 RF_P RFI/O PositiveRFoutputsignalfromPA. 11 RF_N RFI/O NegativeRFoutputsignalfromPA. 12 AVDD Power(Analog) 1.8-Vto3.6-Vanalogpowersupplyconnection. 13 AVDD Power(Analog) 1.8-Vto3.6-Vanalogpowersupplyconnection. 14 RBIAS AnalogI/O Externalbiasresistorforreferencecurrent. 15 DGUARD Power(Digital) Powersupplyconnectionfordigitalnoiseisolation. 16 SI DigitalInput Serialconfigurationinterface,datainput. (1) Theexposeddieattachpadmustbeconnectedtoasolidgroundplaneasthisisthemaingroundconnectionforthechip. (2) ThispinisintendedforusewiththeCC1150only.Itcannotbeusedtoprovidesupplyvoltagetootherdevices. Copyright©2006–2015,TexasInstrumentsIncorporated TerminalConfigurationandFunctions 5 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com 4 Specifications 4.1 Absolute Maximum Ratings(1)(2) overoperatingfree-airtemperaturerange(unlessotherwisenoted) MIN MAX UNIT CONDITION Allsupplypinsmusthavethesame Supplyvoltage –0.3 3.6 V voltage Voltageonanydigitalpin –0.3 VDD+0.3,max3.6 V VoltageonthepinsRF_P,RF_Nand –0.3 2.0 V DCOUPL Voltageramp-up 120 kV/µs InputRFlevel +10 dBm Storagetemperaturerange,T –50 150 °C stg (1) Stressesbeyondthoselistedunderabsolutemaximumratingsmaycausepermanentdamagetothedevice.Thesearestressratings only,andfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderrecommendedoperating conditionsisnotimplied.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability. (2) AllvoltagevaluesarewithrespecttoV ,unlessotherwisenoted. SS 4.2 ESD Ratings VALUE UNIT Human-bodymodel(HBM),perANSI/ESDA/JEDECJS-001(1)(2) <500 V Electrostaticdischarge V (ESD) Charged-devicemodel(CDM) 250 (1) JEDECdocumentJEP155statesthat500-VHBMallowssafemanufacturingwithastandardESDcontrolprocess.Manufacturingwith lessthan500-VHBMispossiblewiththenecessaryprecautions. (2) AccordingtoJEDECSTD22,methodA114,HumanBodyModel 4.3 Recommended Operating Conditions overoperatingfree-airtemperaturerange(unlessotherwisenoted) MIN MAX UNIT CONDITION Operatingtemperature –40 85 °C Allsupplypinsmusthavethesame Operatingsupplyvoltage 1.8 3.6 V voltage 4.4 General Characteristics overrecommendedoperatingconditions(unlessotherwisenoted) PARAMETER MIN TYP MAX UNIT CONDITION 300 348 MHz Frequencyrange 400 464 MHz 800 928 MHz 1.2 500 kBaud 2-FSK 1.2 250 kBaud GFSK,OOKandASK (Shaped)MSK(alsoknownas Datarate differentialoffsetQPSK) 26 500 kBaud OptionalManchesterencoding(the datarateinkbpswillbehalfthe baudrate) 6 Specifications Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 4.5 Current Consumption T =25°C,VDD=3.0Vifnothingelsestated.AllmeasurementresultsareobtainedusingtheCC1150EMreferencedesign c (see[1]and[2]). PARAMETER TYP UNIT CONDITION 200 nA Voltageregulatortodigitalpartoff,registervalueslost(SLEEPstate) Voltageregulatortodigitalparton,allothermodulesinpowerdown 222 µA (XOFFstate) Onlyvoltageregulatortodigitalpartandcrystaloscillatorrunning Currentconsumption 1.1 mA (IDLEstate) Onlythefrequencysynthesizerrunning(FSTXONstate).This currentconsumptionalsorepresentativefortheotherintermediate 7.7 mA stateswhengoingfromIDLEuntilreachingTX,andfrequency calibrationstates 25.6 mA Transmitmode,+10dBmoutputpower(0xC4) Currentconsumption,315MHz 14.1 mA Transmitmode,0dBmoutputpower(0x60) SeemoreinSection5.16andDN012[3]. 26.1 mA Transmitmode,+10dBmoutputpower(0xC2) Currentconsumption,433MHz 14.6 Transmitmode,0dBmoutputpower(0x60) SeemoreinSection5.16andDN012[3]. 29.3 mA Transmitmode,+10dBmoutputpower(0xC3) Currentconsumption,868MHz 15.5 Transmitmode,0dBmoutputpower(0x60) SeemoreinSection5.16andDN012[3]. 29.3 mA Transmitmode,+10dBmoutputpower(0xC0) Currentconsumption,915MHz 15.2 mA Transmitmode,0dBmoutputpower(0x50) SeemoreinSection5.16andDN012[3]. 4.6 RF Transmit T =25°C,VDD=3.0V,ifnothingelsestated.AllmeasurementresultsareobtainedusingtheCC1150EMreferencedesign c (see[1]and[2]). PARAMETER TYP MAX UNIT CONDITION 315MHz 122+j31 Ω DifferentialimpedanceasseenfromtheRF- Differentialload 433MHz 116+j41 Ω port(RF_PandRF_N)towardstheantenna. impedance FollowtheCC1150EMreferencedesign 86.5+ 868/915MHz Ω (see[1]and[2]). j43 Outputpowerisprogrammable,andfull rangeisavailableacrossallfrequency bands.Outputpowermayberestrictedby regulatorylimits.Seealso DN006[5]. Deliveredtoa50-Ωsingle-endedloadvia Outputpower,highestsetting +10 dBm CC1150EMreferencedesign(see[1]and [2])RFmatchingnetwork.Maximumoutput powercanbeincreased1to2dBbyusing wire-woundinductorsinsteadofmultilayer inductorsinthebalunandfiltercircuitforthe 868/915MHzband,seemoreinDN017[6]. Outputpowerisprogrammable,andfull rangeisavailableacrossallfrequency bands. Outputpower,lowestsetting –30 dBm Deliveredtoa50Ωsingle-endedloadvia CC1150EMreferencedesign(see[1]and [2])RFmatchingnetwork. Copyright©2006–2015,TexasInstrumentsIncorporated Specifications 7 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com RF Transmit (continued) T =25°C,VDD=3.0V,ifnothingelsestated.AllmeasurementresultsareobtainedusingtheCC1150EMreferencedesign c (see[1]and[2]). PARAMETER TYP MAX UNIT CONDITION 25MHzto1GHz –36 dBm Spurious 47to74MHz, emissionsand 87.5to118MHz, harmonics(1), 174to230MHz, –54 dBm 433/868MHz 470to862MHz Otherwiseabove1GHz –30 dBm <200µV/mat3mbelow dBm –49.2 Spuriousemissions, 960MHz EIRP 315/915MHz <500µV/mat3mabove dBm –41.2 960MHz EIRP Wheoutputpowerismaximum 2nd,3rdand4thharmonic –20 dBc Harmonics315MHz 6mV/mat3m(–19.6dBmEIRP) 5thharmonic –41.2 dBm 2ndharmonic –20 dBc With+10dBmoutputpower Harmonics915MHz 3rd,4th,and5thharmonic –41.2 dBm Serialoperation.Timefromsamplingthe TXlatency 8 Bits dataonthetransmitterdatainputpinuntilit isobservedontheRFoutputports. (1) Notethatclose-inspursvarywithcentrefrequencyandlimitsthefrequenciesandoutputpowerlevelwhichtheCC1150canoperateat withoutviolatingregulatoryrestrictions.SeealsoSection6.2.5forinformationregardingadditionalfiltering. 4.7 Crystal Oscillator T =25°C,VDD=3.0Vifnothingelseisstated.AllmeasurementresultsobtainedusingtheCC1150EMreferencedesign c (see[1]and[2]). PARAMETER MIN TYP MAX UNIT CONDITION Crystalfrequency 26 26 27 MHz Thisisthetotaltoleranceincludinga)initial tolerance,b)agingandc)temperature dependence. Tolerance ±40 ppm Theacceptablecrystaltolerancedependson RFfrequencyandchannelspacing/ bandwidth Loadcapacitance 10 13 20 pF Simulatedoveroperatingconditions ESR 100 Ω MeasuredontheCC1150EMreference Start-uptime 150 µs design(see[1]and[2]).Thisparameteristo alargedegreecrystaldependent. 4.8 Frequency Synthesizer Characteristics T =25°C,VDD=3.0Vifnothingelseisstated.AllmeasurementresultsobtainedusingtheCC1150EMreferencedesign c (see[1]and[2]). PARAMETER MIN TYP MAX UNIT CONDITION Programmedfrequency 397 F /216 412 Hz 26MHzto27MHzcrystals.Theresolution resolution XOSC (inHz)isequalforallfrequencybands. Givenbycrystalused.Requiredaccuracy (includingtemperatureandaging)depends Synthesizerfrequencytolerance ±40 ppm onfrequencybandandchannelbandwidth/ spacing. @50kHzoffsetfromcarrier, RFcarrierphasenoise –82 dBc/Hz carrierat868MHz @100kHzoffsetfromcarrier, RFcarrierphasenoise –86 dBc/Hz carrierat868MHz 8 Specifications Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 Frequency Synthesizer Characteristics (continued) T =25°C,VDD=3.0Vifnothingelseisstated.AllmeasurementresultsobtainedusingtheCC1150EMreferencedesign c (see[1]and[2]). PARAMETER MIN TYP MAX UNIT CONDITION @200kHzoffsetfromcarrier, RFcarrierphasenoise –90 dBc/Hz carrierat868MHz @500kHzoffsetfromcarrier, RFcarrierphasenoise –98 dBc/Hz carrierat868MHz @1MHzoffsetfromcarrier, RFcarrierphasenoise –106 dBc/Hz carrierat868MHz @2MHzoffsetfromcarrier, RFcarrierphasenoise –113 dBc/Hz carrierat868MHz @5MHzoffsetfromcarrier, RFcarrierphasenoise –119 dBc/Hz carrierat868MHz @10MHzoffsetfromcarrier, RFcarrierphasenoise –127 dBc/Hz carrierat868MHz TimefromleavingtheIDLEstateuntil arrivingintheFSTXONorTXstate,when PLLturn-on/hoptime 85.1 88.4 88.4 µs notperformingcalibration. Crystaloscillatorrunning. Calibrationcanbeinitiatedmanuallyor XOSC 18739 automaticallybeforeenteringorafterleaving cycles PLLcalibrationtime TX. Min/typ/maxtimeisfor27/26/26MHzcrystal 694 721 721 µs frequency. 4.9 Analog Temperature Sensor(1) T =25°C,VDD=3.0Vifnothingelseisstated. c PARAMETER MIN TYP MAX UNIT CONDITION Outputvoltageat–40°C 0.651 V Outputvoltageat0°C 0.747 V Outputvoltageat+40°C 0.847 V Outputvoltageat+80°C 0.945 V Temperaturecoefficient 2.45 mV/°C Fittedfrom–20°Cto+80°C From–20°Cto+80°C whenusing Absoluteerrorincalculatedtemperature –2(2) 2(2) °C 2.45mV/°C,after1-point calibrationatroom temperature Currentconsumptionincreasewhen 0.3 mA enabled (1) Itisnecessarytowrite0xBFtothePTESTregistertousetheanalogtemperaturesensorintheIDLEstate. (2) Indicatedminimumandmaximumerrorwith1-pointcalibrationisbasedonsimulatedvaluesfortypicalprocessparameters 4.10 DC Characteristics T =25°Cifnothingelsestated. c DIGITALINPUTS/OUTPUTS MIN MAX UNIT CONDITION Logic"0"inputvoltage 0 0.7 V Logic"1"inputvoltage VDD–0.7 VDD V Logic"0"outputvoltage 0 0.5 V Forupto4mAoutputcurrent Logic"1"outputvoltage VDD–0.3 VDD V Forupto4mAoutputcurrent Logic"0"inputcurrent N/A –1 µA Inputequals0V Logic"1"inputcurrent N/A 1 µA InputequalsVDD Copyright©2006–2015,TexasInstrumentsIncorporated Specifications 9 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com 4.11 Power-On Reset ForproperPower-On-Resetfunctionality,thepowersupplymustcomplywiththerequirementsinthistable.Otherwise,the chipshouldbeassumedtohaveunknownstateuntiltransmittinganSRESstrobeovertheSPIinterface.SeeSection5.11.1 foradescriptionoftherecommendedstart-upsequenceafterturningpoweron. PARAMETER MIN TYP MAX UNIT CONDITION Powerupramp-uptime 5 ms From0Vuntilreaching1.8V Minimumtimebetweenpoweronand Power-offtime 1 ms poweroff 4.12 Thermal Resistance Characteristics for VQFNP Package NAME DESCRIPTION °C/W(1) (2) R Junction-to-case(top) 54.0 θJC(top) R Junction-to-board 25.1 θJB R Junction-to-freeair 48.3 θJA Psi Junction-to-packagetop 1.6 JT Psi Junction-to-board 25.2 JB R Junction-to-case(bottom) 6.3 θJC(bottom) (1) °C/W=degreesCelsiusperwatt. (2) ThesevaluesarebasedonaJEDEC-defined2S2Psystem(withtheexceptionoftheThetaJC[R ]value,whichisbasedona θJC JEDEC-defined1S0Psystem)andwillchangebasedonenvironmentaswellasapplication.Formoreinformation,seethese EIA/JEDECstandards: • JESD51-2,IntegratedCircuitsThermalTestMethodEnvironmentalConditions-NaturalConvection(StillAir) • JESD51-3,LowEffectiveThermalConductivityTestBoardforLeadedSurfaceMountPackages • JESD51-7,HighEffectiveThermalConductivityTestBoardforLeadedSurfaceMountPackages • JESD51-9,TestBoardsforAreaArraySurfaceMountPackageThermalMeasurements Powerdissipationof2Wandanambienttemperatureof70ºCisassumed. 10 Specifications Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 5 Detailed Description 5.1 Overview The CC1150 transmitter is based on direct synthesis of the RF frequency. The frequency synthesizer includesacompletelyon-chipLCVCO. A crystal is to be connected to XOSC_Q1 and XOSC_Q2. The crystal oscillator generates the reference frequency for the synthesizer, as well as clocks for the digital part. A 4-wire SPI serial interface is used for configuration and data buffer access. The digital baseband includes support for channel configuration, packethandlinganddatabuffering. 5.2 Functional Block Diagram RADIOCONTROL RRFF__NP PA SFYRNETQH ODULATOR FEC/TERLEAVER PACKETHANDLER TXFIFO DIGITALNTERFACETOMCU SSSCCOISLn(KGDO1) BIAS XOSC M N I GDO0(ATEST) I RBIAS XOSC_Q1 XOSC_Q2 Figure5-1.CC1150SimplifiedBlockDiagram 5.3 Configuration Overview CC1150 can be configured to achieve optimum performance for many different applications. Configuration isdoneusingtheSPIinterface.Thefollowingkeyparameterscanbeprogrammed: • Power-downandpower-upmode • Crystaloscillatorpowerupandpowerdown • Transmitmode • RFchannelselection • Datarate • Modulationformat • RFoutputpower • Databufferingwith64-bytetransmitFIFO • Packetradiohardwaresupport • ForwardErrorCorrectionwithinterleaving • DataWhitening DetailsofeachconfigurationregistercanbefoundinSection5.20. Figure 5-2 shows a simplified state diagram that explains the main CC1150 states, together with typical usage and current consumption. For detailed information on controlling the CC1150 state machine, and a completestatediagram,seeSection5.11. Copyright©2006–2015,TexasInstrumentsIncorporated DetailedDescription 11 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com Lowestpowermode. Registervaluesarelost. Sleep Current consumptiontyp SIDLE SPWD 200nA. Defaultstatewhentheradioisnot receivingortransmitting.Typ. CSn=0 currentconsumption: 1.1mA. IDLE SXOFF Usedforcalibratingfrequency SCAL synthesizerupfront(entering CSn=0 Allregistervaluesare transmitmodecanthenbe Manualfreq. Crystal retained.Typ.current donequicker).Transitional synth.calibration oscillatoroff SRXorSTXorSFSTXON consumption;0.22mA. state.Typ. current consumption:7.7mA. Frequency Frequencysynthesizeristurnedon,canoptionallybe synthesizerstartup, calibrated,andthensettlestothecorrectfrequency. SFSTXON optionalcalibration, Frequencysynthesizerison, Transitionalstate.Typ.currentconsumption:7.7mA. settling readytostarttransmitting. Transmissionstartsvery Frequency quicklyafterreceivingtheSTX synthesizeron commandstrobe.Typ. current consumption:7.7mA. STX STX TXOFF_MODE=01 Typ.currentconsumption868MHz: 14mAat-10dBmoutput, 15mAat0dBmoutput, Transmitmode 24mAat+7dBmoutput, 29mAat+10dBmoutput. TXOFF_MODE=00 InFIFO-basedmodes, transmissionisturnedoffand thisstateenterediftheTX TX FIFO Optionaltransitionalstate.Typ. Optionalfreq. FIFObecomesemptyinthe underflow currentconsumption: 7.7mA. synth. calibration middleofapacket.Typ. currentconsumption:1.1mA. SFTX IDLE Figure5-2.SimplifiedStateDiagramwithTypicalUsageandCurrentConsumption 5.4 Configuration Software CC1150 can be configured using the SmartRF Studio [11] software. The SmartRF Studio software is highly recommended for obtaining optimum register settings, and for evaluating performance and functionality.AscreenshotoftheSmartRFStudiouserinterfaceforCC1150isshowninFigure5-3. After chip reset, all the registers have default values as shown in the tables in Section 5.20. The optimum register setting might differ from the default value. After a reset all registers that shall be different from the defaultvaluethereforeneedstobeprogrammedthroughtheSPIinterface. 12 DetailedDescription Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 Figure5-3.SmartRFStudioUserInterface 5.5 4-wire Serial Configuration and Data Interface CC1150 is configured via a simple 4-wire SPI-compatible interface (SI, SO, SCLK and CSn) where CC1150 is the slave. This interface is also used to read and write buffered data. All address and data transferontheSPIinterfaceisdonemostsignificantbitfirst. All transactions on the SPI interface start with a header byte containing a read/write bit, a burst access bit anda6-bitaddress. During address and data transfer, the CSn pin (Chip Select, active low) must be kept low. If CSn goes high during the access, the transfer will be cancelled. The timing for the address and data transfer on the SPIinterfaceisshowninFigure5-4withreferencetoTable5-1. When CSn is pulled low, the MCU must wait until the CC1150 SO pin goes low before starting to transfer the header byte. This indicates that the voltage regulator has stabilized and the crystal is running. Unless thechipisintheSLEEPorXOFFstates,theSOpinwillalwaysgolowimmediatelyaftertakingCSnlow. Copyright©2006–2015,TexasInstrumentsIncorporated DetailedDescription 13 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com t t t t t t sp ch cl sd hd ns SCLK: CSn: Writetoregister: SI X 0 A6 A5 A4 A3 A2 A1 A0 X DW7 DW6 DW5 DW4 DW3 DW2 DW1 DW0 X SO Hi-Z S7 S6 S5 S4 S3 S2 S1 S0 S7 S6 S5 S4 S3 S2 S1 S0 S7 Hi-Z Readfromregister: SI X 1 A6 A5 A4 A3 A2 A1 A0 X SO Hi-Z S7 S6 S5 S4 S3 S2 S1 S0 DR7 DR6 DR5 DR4 DR3 DR2 DR1 DR0 Hi-Z Figure5-4.ConfigurationRegistersWriteandReadOperations Table5-1.SPIInterfaceTimingRequirements PARAMETER DESCRIPTION MIN MAX UNIT SCLKfrequency 100nsdelayinsertedbetweenaddressbyteanddatabyte(singleaccess),or — 10 betweenaddressanddata,andbetweeneachdatabyte(burstaccess). f SCLKfrequency,singleaccess MHz SCLK 9 Nodelaybetweenaddressanddatabyte SCLKfrequency,burstaccess 6.5 Nodelaybetweenaddressanddatabyte,orbetweendatabytes t CSnlowtopositiveedgeonSCLK,inpower-downmode 150 — µs sp,pd t CSnlowtopositiveedgeonSCLK,inactivemode 20 — ns sp t Clockhigh 50 — ns ch t Clocklow 50 — ns cl t Clockrisetime — 5 ns rise t Clockfalltime — 5 ns fall Setupdata(negativeSCLKedge)topositiveedgeon Singleaccess 55 — ns SCLK t sd (t appliesbetweenaddressanddatabytes,and Burstaccess sd 76 — ns betweendatabytes) t HolddataafterpositiveedgeonSCLK 20 — ns hd t NegativeedgeonSCLKtoCSnhigh 20 — ns ns NOTE The minimum t figure in Table 5-1 can be used in cases where the user does not read sp,pd the CHIP_RDYn signal. CSn low to positive edge on SCLK when the chip is woken from power-downdependsonthestart-uptimeofthecrystalbeingused.The150μsinTable5-1 isthecrystaloscillatorstart-uptimemeasuredusingcrystalAT-41CD2fromNDK. 5.5.1 Chip Status Byte When the header byte, data byte or command strobe is sent on the SPI interface, the chip status byte is sent by the CC1150 on the SO pin. The status byte contains key status signals, useful for the MCU. The first bit, s7, is the CHIP_RDYn signal; this signal must go low before the first positive edge of SCLK. The CHIP_RDYnsignalindicatesthatthecrystalisrunningandtheregulateddigitalsupplyvoltageisstable. Bit 6, 5 and 4 comprises the STATE value. This value reflects the state of the chip. The XOSC and power to the digital core is on in the IDLE state, but all other modules are in power down. The frequency and channel configuration should only be updated when the chip is in this state. The TX state will be active whenthechipistransmitting. 14 DetailedDescription Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 The last four bits (3:0) in the status byte con-tains FIFO_BYTES_AVAILABLE. This field contains the number of bytes free for writing into the TX FIFO. When FIFO_BYTES_AVAILABLE=15, 15 or more bytes arefree.Table5-2givesastatusbytesummary. Table5-2.StatusByteSummary BITS NAME DESCRIPTION Stayshighuntilpowerandcrystalhavestabilized.Shouldalwaysbelowwhenusingthe 7 CHIP_RDYn SPIinterface. Indicatesthecurrentmainstatemachinemode. Thebinarynumberisthevalue,theresultisthestate,andthedefinitionisthecurrent mainstatemachinemode. 000=Idle:IDLEstate(1) 001=Notused:Notused 6:04 STATE[2:0] 010=TX:Transmitmode 011=FSTXON:FastTXready 100=CALIBRATE:Frequencysynthesizercalibrationisrunning 101=SETTLING:PLLissettling 110=Notused:Notused 111=TXFIFO_UNDERFLOW:TXFIFOhasunderflowed.AcknowledgewithSFTX 3:00 FIFO_BYTES_AVAILABLE[3:0] ThenumberoffreebytesintheTXFIFO. (1) AlsoreportedforsometransitionalstatesinsteadofSETTLINGorCALIBRATE,duetoasmallerror. 5.5.2 Register Access The configuration registers on the CC1150 are located on SPI addresses from 0x00 to 0x2E. Table 5-12 listsallconfigurationregisters.ThedetaileddescriptionofeachregisterisfoundinSection5.20. Allconfigurationregisterscanbebothwrittenandread.Theread/writebitcontrolsiftheregistershouldbe writtenorread.Whenwritingtoregisters,thestatusbyteissentontheSOpineachtimeaheaderbyteor data byte is transmitted on the SI pin. When reading from registers, the status byte is sent on the SO pin eachtimeaheaderbyteistransmittedontheSIpin. Registers with consecutive addresses can be accessed in an efficient way by setting the burst bit in the address header. The address sets the start address in an internal address counter. This counter is incremented by one each new byte (every 8 clock pulses). The burst access is either a read or a write accessandmustbeterminatedbysettingCSnhigh. For register addresses in the range 0x30 through 0x3D, the burst bit is used to select between status registers (burst bit is 1) and command strobes (burst bit is 0). See more in Section 5.5.3. Because of this, burst access is not available for status registers, so they must be read one at a time. The status registers canonlyberead. 5.5.3 SPI Read When reading register fields over the SPI interface while the register fields are updated by the radio hardware (for example, MARCSTATE or TXBYTES), there is a small, but finite, probability that a single read from the register is being corrupt. As an example, the probability of any single read from TXBYTES being corrupt, assuming the maximum data rate is used, is approximately 80 ppm. Refer to the CC1150 ErrataNotes[8]formoredetails. 5.5.4 Command Strobes Command Strobes may be viewed as single byte instructions to CC1150. By addressing a Command Strobe register, internal sequences will be started. These commands are used to disable the crystal oscillator, enable transmit mode, flush the TX FIFO, and so on. The nine command strobes are listed in Table5-11. Copyright©2006–2015,TexasInstrumentsIncorporated DetailedDescription 15 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com NOTE An SIDLE strobe will clear all pending command strobes until IDLE state is reached. This meansthatifforexampleanSIDLEstrobeisissuedwhiletheradioisinTXstate,anyother commandstrobesissuedbeforetheradioreachesIDLEstatewillbeignored. Thecommandstroberegistersareaccessedinthesamewayasforaregisterwriteoperation,butnodata is transferred. That is, only the R/W bit (set to 0), burst access (set to 0) and the six address bits (in the range0x30through0x3D)arewritten. Whenwritingcommandstrobes,thestatusbyteissentontheSOpin. A command strobe may be followed by any other SPI access without pulling CSn high. However, if an SRES command strobe is being issued, on will have to wait for the SO pin to go low before the next command strobe can be issued as shown in Figure 5-5.The command strobes are executed immediately, withtheexceptionoftheSPWDandtheSXOFFstrobesthatareexecutedwhenCSngoeshigh. CSn SO SI SRES Sxxx Sxxx Figure5-5.SRESCommandStrobe 5.5.5 FIFO Access The 64-byte TX FIFO is accessed through the 0x3F addresses. When the read/write bit is zero, the TX FIFOisaccessed.TheTXFIFOiswrite-only. The burst bit is used to determine if FIFO access is single byte or a burst access. The single byte access method expects address with burst bit set to zero and one data byte. After the data byte a new address is expected; hence, CSn can remain low. The burst access method expects one address byte and then consecutivedatabytesuntilterminatingtheaccessbysettingCSnhigh. ThefollowingheaderbytesaccesstheFIFO: • 0x3F:SinglebyteaccesstoTXFIFO • 0x7F:BurstaccesstoTXFIFO When writing to the TX FIFO, the status byte (see Section 5.5.1) is output for each new data byte on SO, as shown in Figure 5-5. This status byte can be used to detect TX FIFO underflow while writing data to theTXFIFO. NOTE The status byte contains the number of bytes free before writing the byte in progress to the TXFIFO. When the last byte that fits in the TX FIFO is transmitted to the SI pin, the status byte received concurrentlyontheSOpinwillindicatethatonebyteisfreeintheTXFIFO. The TX FIFO may be flushed by issuing a SFTX command strobe. The SFTX command strobe can only beissuesintheIDLEorTX_UNDERFLOWstates.TheFIFOisclearedwhengoingtotheSLEEPstate. Figure5-6givesabriefoverviewofdifferentregisteraccesstypespossible. 16 DetailedDescription Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 CSn: Commandstrobe(s): ADDR ADDR ADDR ... strobe strobe strobe Readorwriteregister(s): ADDRreg DATA ADDRreg DATA ADDRreg DATA ... Readorwriteconsecutiveregisters(burst): ADDRregn DATAn DATAn+1 DATAn+2 ... Readorwriten+1bytesfrom/toRFFIFO: ADDR DATA DATA DATA ... DATA DATA FIFO byte0 byte1 byte2 byten-1 byten Combinations: ADDR DATA ADDR ADDR DATA ADDR ADDR DATA DATA ... reg strobe reg strobe FIFO byte0 byte1 Figure5-6.RegisterAccessTypes 5.5.6 PATABLE Access The 0x3E address is used to access the PATABLE, which is used for selecting PA power control settings. The SPI expects up to eight data bytes after receiving the address. By programming the PATABLE, controlled PA power ramp-up and ramp-down can be achieved, as well as ASK modulation shaping for reducedbandwidth. NOTE TheASKmodulationshapingislimitedtooutputpowersbelow–1dBm.SeeSmartRFStudio [11]forrecommendedshapingsequence. SeealsoSection5.16fordetailsonoutput-powerprogramming. ThePATABLEisan8-bytetablethatdefinesthePAcontrolsettingstouseforeachoftheeightPApower values (selected by the 3-bit value FREND0.PA_POWER). The table is written and read from the lowest setting (0) to the highest (7), one byte at a time. An index counter is used to control the access to the table. This counter is incremented each time a byte is read or written to the table, and set to the lowest indexwhenCSnishigh.Whenthehighestvalueisreachedthecounterrestartsatzero. The access to the PATABLE is either single byte or burst access depending on the burst bit. When using burst access the index counter will count up; when reaching 7 the counter will restart at 0. The read/write bitcontrolswhethertheaccessisawriteaccess(R/W=0)orareadaccess(R/W=1). If one byte is written to the PATABLE and this value is to be read out then CSn must be set high before thereadaccessinordertosettheindexcounterbacktozero. NOTE The content of the PATABLE is lost when entering the SLEEP state. For more information, seeDN501[8]. 5.6 Microcontroller Interface and Pin Configuration In a typical system, CC1150 will interface to a microcontroller. This microcontroller must be able to do the following: • ProgramCC1150intodifferentmodes • Writebuffereddata • Readbackstatusinformationviathe4-wireSPI-busconfigurationinterface(SI,SO,SCLKandCSn) 5.6.1 Configuration Interface The microcontroller uses four I/O pins for the SPI configuration interface (SI, SO, SCLK and CSn). The SPIisdescribedinSection5.5. Copyright©2006–2015,TexasInstrumentsIncorporated DetailedDescription 17 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com 5.6.2 General Control and Status Pins The CC1150 has one dedicated configurable pin (GDO0) and one shared pin (GDO1/SO) that can output internal status information useful for control software. These pins can be used to generate interrupts on the MCU. See Section 5.17 for more details of the signals that can be programmed. The shared pin is the SO pin in the SPI interface. The default setting for GDO1/SO is 3-state output. By selecting any other of the programming options the GDO1/SO pin will become a generic pin. When CSn is low, the pin will alwaysfunctionasanormalSOpin. In the synchronous and asynchronous serial modes, the GDO0 pin is used as a serial TX data input pin whileintransmitmode. The GDO0 pin can also be used for an on-chip analog temperature sensor. By measuring the voltage on theGDO0pinwithanexternalADC,thetemperaturecanbecalculated.Specificationsforthetemperature sensor are found in Section 4.9. With default PTEST register setting (0x7F), the temperature sensor output is only available when the frequency synthesizer is enabled (for example, the MANCAL, FSTXON and TX states). It is necessary to write 0xBF to the PTEST register to use the analog temperature sensor intheIDLEstate.BeforeleavingtheIDLEstate,thePTESTregistershouldberestoredtoitsdefaultvalue (0x7F). 5.6.3 Optional Radio Control Feature The CC1150 has an optional way of controlling the radio by reusing SI, SCLK, and CSn from the SPI interface. This feature allows for a simple three-pin control of the major states of the radio: SLEEP, IDLE, andTX. ThisoptionalfunctionalityisenabledwiththeMCSM0.PIN_CTRL_ENconfigurationbit. Statechangesarecommandedasfollows: • IfCSnishigh,theSIandSCLKaresettothedesiredstateaccordingtoTable5-3. • If CSn goes low, the state of SI and SCLK is latched and a command strobe is generated internally accordingtothepinconfiguration. It is only possible to change state with the latter functionality. That means that for instance TX will not be restarted if SI and SCLK are set to TX and CSn toggles. When CSn is low the SI and SCLK has normal SPIfunctionality. All pin control command strobes are executed immediately except the SPWD strobe. The SPWD strobe is delayeduntilCSngoeshigh. Table5-3.OptionalPinControlCoding CSn SCLK SI FUNCTION 1 X X ChipunaffectedbySCLK/SI ↓ 0 0 GeneratesSPWDstrobe ↓ 0 1 GeneratesSTXstrobe ↓ 1 0 GeneratesSIDLEstrobe ↓ 1 1 Definedonthetransceiverversion(CC1101) SPImode(wakesupintoIDLEifin 0 SPImode SPImode SLEEP/XOFF) 5.7 Data Rate Programming The data rate used when transmitting is programmed by the MDMCFG3.DRATE_M and the MDMCFG4.DRATE_E configuration registers. The data rate is given by the formula below. As Equation 1 shows,theprogrammeddataratedependsonthecrystalfrequency. (256+DRATE_M)´2DRATE_E R = ´f DATA 228 XOSC (1) 18 DetailedDescription Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 ThefollowingapproachshowninEquation2 canbeusedtofindsuitablevaluesforagivendatarate. é æR ´220 öù DRATE_E=êlog ç DATA ÷ú ê 2ç f ÷ú ë è XOSC øû R ´228 DRATE_M= DATA -256 f ´2DRATE_E XOSC (2) If DRATE_M is rounded to the nearest integer and becomes 256, increment DRATE_E and use DRATE_M=0. The data rate can be set from 0.8 kBaud to 500 kBaud with the minimum data rate step size changes accordingtoTable5-4. Table5-4.DataRateStepSize MINDATARATE TYPICALDATARATE MAXDATARATE DATARATESTEPSIZE [kBaud] [kBaud] [kBaud] [kBaud] 0.8 1.2/2.4 3.17 0.0062 3.17 4.8 6.35 0.0124 6.35 9.6 12.7 0.0248 12.7 19.6 25.4 0.0496 25.4 38.4 50.8 0.0992 50.8 76.8 101.6 0.1984 101.6 153.6 203.1 0.3967 203.1 250 406.3 0.7935 406.3 500 500 1.5869 5.8 Packet Handling Hardware Support TheCC1150hasbuilt-inhardwaresupportforpacketorientedradioprotocols. In transmit mode, the packet handler can be configured to add the following elements to the packet stored intheTXFIFO: • Aprogrammablenumberofpreamblebytes. • A two byte Synchronization Word. Can be duplicated to give a 4-byte sync word (recommended). It is notpossibletoonlyinsertpreambleoronlyinsertasyncword. • OptionallywhiteningthedatawithaPN9sequence. • OptionallyInterleaveandForwardErrorCodethedata. • Optionallycomputeandadda2-byteCRCchecksumoverthedatafield. In a system where CC1150 is used as the transmitter and CC1101 as the receiver the recommended setting is 4-byte preamble and 4-byte sync word except for 500 kBaud data rate where the recommended preamblelengthis8bytes. NOTE RegisterfieldsthatcontrolthepackethandlingfeaturesshouldonlybealteredwhenCC1150 isintheIDLEstate. 5.8.1 Data Whitening From a radio perspective, the ideal over the air data are random and DC free. This results in the smoothest power distribution over the occupied bandwidth. This also gives the regulation loops in the receiveruniformoperationconditions(nodatadependencies). Copyright©2006–2015,TexasInstrumentsIncorporated DetailedDescription 19 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com Real world data often contain long sequences of zeros and ones. Performance can then be improved by whiteningthedatabeforetransmitting,andde-whiteninginthereceiver.WithCC1150,incombinationwith a CC1101 at the receiver end, this can be done automatically by setting PKTCTRL0WHITE_DATA=1. All data, except the preamble and the sync word, are then XOR-ed with a 9-bit pseudo-random (PN9) sequence before being transmitted as shown in Figure 5-7. The PN9 sequence is initialized to all ones. At the receiver end, the data are XOR-ed with the same pseudo-random sequence. This way, the whitening isreversed,andtheoriginaldataappearinthereceiver. Setting PKTCTRL0.WHITE_DATA=1 is recommended for all uses, except when over-the-air compatibility withothersystemsisneeded. 8 7 6 5 4 3 2 1 0 TX_DATA 7 6 5 4 3 2 1 0 The firstTX_DATAbyte is shifted in before doing the XOR-operation providing the firstTX_OUT[7:0] byte.The secondTX_DATAbyte is then shifted in before doing the XOR-operation providing the secondTX_OUT[7:0] byte. TX_OUT[7:0] Figure5-7.DataWhiteninginTXMode 5.8.2 Packet Format Theformatofthedatapacketcanbeconfiguredandconsistsofthefollowingitems: • Preamble • Synchronizationword • Optionallengthbyte • OptionalAddressbyte • Payload • Optional2byteCRC Optional data whitening Optionally FEC encoded/decoded Legend: Optional CRC-16 calculation Inserted automatically inTX, processed and removed in RX. P(1r0e1a0m..b.l1e0 b1i0ts) Sync word Length field Address field Data field CRC-16 OpUarnnpodptci/roeoonsrc asweel shudsis tebeedunr -tiu npnsgroeo)trv ridedametdao vf(iaeepdld aisnr t p RfrrXoocm.e FssEeCd inTX, 16/32 8 8 8 x n bits 8 x n bits 16 bits bits bits bits Figure5-8.PacketFormat 20 DetailedDescription Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 The preamble pattern is an alternating sequence of ones and zeros (01010101…). The number of preamble bytes is programmed with the MDMCFG1.NUM_PREAMBLE value. When enabling TX, the modulatorwillstarttransmittingthepreamble.Whentheprogrammednumberofpreamblebyteshasbeen transmitted, the modulator will send the sync word and then data from the TX FIFO if data is available. If the TX FIFO is empty, the modulator will continue to send preamble bytes until the first byte is written to theTXFIFO.Themodulatorwillthensendthesyncwordandthenthedatabytes. The synchronization word is a two-byte value set in the SYNC1 and SYNC0 registers. The sync word provides byte synchronization of the incoming packet. A one-byte synch word can be emulated by setting the SYNC1 value to the preamble pattern. It is also possible to emulate a 32 bit sync word by using MDMCFG2.SYNC_MODEsetto3or7.Thesyncwordwillthenberepeatedtwice. C1150 supports both fixed packet length protocols and variable packet length protocols. Variable or fixed packet length mode can be used for packets up to 255 bytes. For longer packets, infinite packet length modemustbeused. Fixed packet length mode is selected by setting PKTCTRL0.LENGTH_CONFIG=0. The desired packet length is set by the PKTLEN register. In variable packet length mode PKTCTRL0.LENGTH_CONFIG=1, the packet length is configured by the first byte after the sync word. The packet length is defined as the payloaddata,excludingthelengthbyteandtheoptionalautomaticCRC. With PKTCTRL0.LENGTH_CONFIG=2, the packet length is set to infinite and transmission will continue until turned off manually. The infinite mode can be turned off while a packet is being transmitted. As described in Section 5.8.2.1, this can be used to support packet formats with different length configuration than natively supported by CC1150. One should make sure that TX mode is not turned off during the transmissionofthefirsthalfofanybyte.Refertothe CC1150ErrataNotes[8]formoredetails. NOTE The minimum packet length supported (excluding the optional length byte and CRC) is one byteofpayloaddata. 5.8.2.1 ArbitraryLengthFieldConfiguration The packet automation control register, PKTCTRL0, can be reprogrammed during TX. This opens the possibility to transmit packets that are longer than 256 bytes and still be able to use the packet handling hardware support. At the start of the packet, the infinite mode (PKTCTRL0.LENGTH_CONFIG=2) must be active. The PKTLEN register is set to mod(length, 256). When less than 256 bytes remains of the packet, the MCU disables infinite packet length and activates fixed length packets. When the internal byte counter reaches the PKTLEN value, the transmission ends (the radio enters the state determined by TXOFF_MODE).AutomaticCRCappendingcanbeused(bysettingPKTCTRL0.CRC_EN=1). When, for example, a 600-byte packet is to be transmitted, the MCU should do the following (see also Figure5-9): • SetPKTCTRL0.LENGTH_CONFIG=2. • Pre-programthePKTLENregistertomod(600,256)=88. • Transmit at least 345 bytes, for example by filling the 64-byte TX FIFO six times (384 bytes transmitted). • SetPKTCTRL0.LENGTH_CONFIG=0. • Thetransmissionendswhenthepacketcounterreaches88.Atotalof600bytesaretransmitted. Copyright©2006–2015,TexasInstrumentsIncorporated DetailedDescription 21 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com Internal byte counter in packet handler counts from 0 to 255 and then starts at 0 again 0,1,..........,88,....................255,0,........,88,..................,255,0,........,88,..................,255,0,....................... Infinite packet length enabled Fixed packet length 600 bytes transmitted enabled when less than 256 bytes remains of packet Length field transmitted.Tx PKTLEN value set to mod(600,256) = 88 Figure5-9.ArbitraryLengthFieldConfiguration 5.8.3 Packet Handling in Transmit Mode The payload that is to be transmitted must be written into the TX FIFO. The first byte written must be the length byte when variable packet length is enabled. The length byte has a value equal to the payload of thepacket(includingtheoptionaladdressbyte).Iffixedpacketlengthisenabled,thenthefirstbytewritten to the TX FIFO is interpreted as the destination address, if this feature is enabled in the device that receivesthepacket. The modulator will first send the programmed number of preamble bytes. If data is available in the TX FIFO, the modulator will send the two-byte (optionally 4-byte) sync word and then the payload in the TX FIFO. If CRC is enabled, the checksum is calculated over all the data pulled from the TX FIFO and the result is sent as two extra bytes at the end of the payload data. If the TX FIFO runs empty before the complete packet has been transmitted, the radio will enter TXFIFO_UNDERFLOW state. The only way to exit this state is by issuing an SFTX strobe. Writing to the TX FIFO after it has underflowed will not restart TXmode. If whitening is enabled, the length byte, payload data and the two CRC bytes will be whitened. This is done before the optional FEC/Interleaver stage. Whitening is enabled by setting PKTCTRL0.WHITE_DATA=1. If FEC/Interleaving is enabled, the length byte, payload data and the two CRC bytes will be scrambled by the interleaver, and FEC encoded before being modulated. FEC is enabled by setting MDMCFG1.FEC_EN=1. 5.8.4 Packet Handling in Firmware When implementing a packet oriented radio protocol in firmware, the MCU needs to know when a packet has been transmitted. Additionally, for packets longer than 64 bytes, the TX FIFO needs to be refilled while in TX. This means that the MCU needs to know the number of bytes that can be written to the TX FIFO.Therearetwopossiblesolutionstogetthenecessarystatusinformation: a. InterruptDrivenSolution – TheGDOpinscanbeusedinTXtogiveaninterruptwhenasyncwordhasbeentransmittedor whenacompletepackethasbeentransmittedbysettingIOCFGx.GDOx_CFG=0x06.Inaddition, therearetwoconfigurationsfortheIOCFGx.GDOx_CFGregisterthatcanbeusedasaninterrupt sourcetoprovideinformationonhowmanybytesthatisintheTXFIFO.The IOCFGx.GDOx_CFG=0x02andtheIOCFGx.GDOx_CFG=0x03configurationsareassociatedwith theTXFIFO.SeeTable5-10 formoreinformation. b. SPIPolling – ThePKTSTATUSregistercanbepolledatagivenratetogetinformationaboutthecurrentGDO2 andGDO0valuesrespectively.TheTXBYTESregistercanbepolledatagivenratetoget informationaboutthenumberofbytesintheTXFIFO.Alternatively,thenumberofbytesintheTX FIFOcanbereadfromthechipstatusbytereturnedontheMISOlineeachtimeaheaderbyte, databyte,orcommandstrobeissentontheSPIbus. 22 DetailedDescription Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 – ItisrecommendedtoemployaninterruptdrivensolutionduetothatwhenusingSPIpolling,there isasmall,butfinite,probabilitythatasinglereadfromregistersPKTSTATUSandTXBYTESis beingcorrupt.Thesameisthecasewhenreadingthechipstatusbyte.Thisisexplainedinthe CC1150ErrataNotes[8]RefertotheTIwebsiteforSWexamples [12]. 5.9 Modulation Formats CC1150 supports amplitude, frequency and phase shift modulation formats. The desired modulation formatissetintheMDMCFG2.MOD_FORMATregister. Optionally, the data stream can be Manchester coded by the modulator. This option is enabled by setting MDMCFG2.MANCHESTER_EN=1. Manchester encoding cuts the effective data rate in half, and thus Manchester is not supported for 500 kBaud. Further note that Manchester encoding is not supported at thesametimeasusingtheFEC/InterleaveroptionorwhenusingMSKmodulation. 5.9.1 Frequency Shift Keying CC1150 has the possibility to use Gaussian shaped 2_FSK (GFSK). The 2-FSK signal is then shaped by aGaussianfilterwithBT=1,producingaGFSKmodulatedsignal.Thisspectrum-shapingfeatureimproves adjacentchannelpower(ACP)andoccupiedbandwidth. In “true” 2-FSK systems with abrupt frequency shifting, the spectrum is inherently broad. By making the frequency shift “softer”, the spectrum can be made significantly narrower. Thus, higher data rates can be transmittedinthesamebandwidthusingGFSK. The frequency deviation is programmed with the DEVIATION_M and DEVIATION_E values in the DEVIATN register. The value has an exponent/mantissa form, and the resultant deviation is given by Equation3. f f = xosc ´(8+DEVIATION_M)´2DEVIATION_E dev 217 (3) ThesymbolencodingisshowninTable5-5. Table5-5.SymbolEncodingfor2-FSK/GFSK Modulation FORMAT SYMBOL CODING 0 –Deviation 2-FSK/GFSK 1 +Deviation 5.9.2 Minimum Shift Keying When using MSK [(Identical to offset QPSK with half-sine shaping (data coding may differ)], the complete transmission(preamble,syncword,andpayload)willbeMSKmodulated. Phase shifts are performed with a constant transition time. The fraction of a symbol period used to change the phase can be modified with the DEVIATN.DEVIATION_M setting. This is equivalent to changing the shapingofthesymbol. NOTE When using MSK, Manchester encoding must be disabled by setting MDMCFG2.MANCHESTER_EN=0. The MSK modulation format implemented in CC1150 inverts the data compared to, forexample,signalgenerators. Copyright©2006–2015,TexasInstrumentsIncorporated DetailedDescription 23 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com 5.9.3 Amplitude Modulation CC1150 supports two different forms of amplitude modulation: On-Off Keying (OOK) and Amplitude Shift Keying(ASK). OOKmodulationsimplyturnsonoroffthePAtomodulate1and0respectively. The ASK variant supported by the CC1150 allows programming of the modulation depth (the difference between 1 and 0), and shaping of the pulse amplitude. Pulse shaping will produce a more bandwidth constrainedoutputspectrum. NOTE The OOK/ASK pulse shaping feature on the CC1150 does only support output power up to about–1dBm.TheDEVIATNregisterhasnoeffectwhenusingASK/OOK. 5.10 Forward Error Correction with Interleaving 5.10.1 Forward Error Correction (FEC) CC1150 has built in support for Forward Error Correction (FEC) that can be used with CC1101 at the receiver end. To enable this option, set MDMCFG1.FEC_EN to 1. FEC is only supported in fixed packet length mode, that is, when PKTCTRL0.LENGTH_CONFIG=0. FEC is employed on the data field and CRC word in order to reduce the gross bit error rate when operating near the sensitivity limit. Redundancy is added to the transmitted data in such a way that the receiver can restore the original data in the presence ofsomebiterrors. The use of FEC allows correct reception at a lower Signal-to-Noise RATIO (SNR), thus extending communication range. Alternatively, for a given SNR, using FEC decreases the bit error rate (BER). As thepacketerrorrate(PER)isrelatedtoBERbyEquation4. PER=1–(1–BER)packet_length (4) A lower BER can be used to allow longer packets, or a higher percentage of packets of a given length, to betransmittedsuccessfully. Finally, in realistic ISM radio environments, transient and time-varying phenomena will produce occasional errors even in otherwise good reception conditions. FEC will mask such errors and, combined with interleavingofthecodeddata,evencorrectrelativelylongperiodsoffaultyreception(bursterrors). The FEC scheme adopted for CC1150 is convolutional coding, in which n bits are generated based on k input bits and the m most recent input bits, forming a code stream able to withstand a certain number of biterrorsbetweeneachcodingstate(them-bitwindow). The convolutional coder is a rate 1/2 code with a constraint length of m = 4. The coder codes one input bit and produces two output bits; hence, the effective data rate is halved. This means that in order to transmit atthesameeffectivedataratewhenusingFEC,itisnecessarytousetwiceashighover-the-airdatarate. 24 DetailedDescription Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 5.10.2 Interleaving Data received through real radio channels will often experience burst errors due to interference and time- varying signal strengths. In order to increase the robustness to errors spanning multiple bits, interleaving isusedwhenFECisenabled.Afterde-interleaving,acontinuousspanoferrorsinthereceivedstreamwill becomesingleerrorsspreadapart. CC1150 employs matrix interleaving, which is illustrated in Figure 5-10. The on-chip interleaving buffer is a 4 × 4 matrix. In the transmitter, the data bits are written into the rows of the matrix, whereas the bit sequence to be transmitted is read from the columns of the matrix and fed to the rate ½ convolutional coder. Conversely, in a CC1101 receiver, the received symbols are written into the rows of the matrix, whereasthedatapassedontotheconvolutionaldecoderisreadfromthecolumnsofthematrix. When FEC and interleaving is used, at least one extra byte is required for trellis termination. In addition, the amount of data transmitted over the air must be a multiple of the size of the interleaver buffer (two bytes). The packet control hardware therefore automatically inserts one or two extra bytes at the end of the packet, so that the total length of the data to be interleaved is an even number. Note that these extra bytes are invisible to the user, as they are removed before the received packet enters the RX FIFO in a CC1101. When FEC and interleaving is used, the minimum data payload is 2 bytes in fixed and variable packet lengthmode. Interleaver Interleaver Writebuffer Readbuffer Packet FEC Modulator Engine Encoder Interleaver Interleaver Writebuffer Readbuffer FEC Packet Demodulator Decoder Engine Figure5-10.:GeneralPrincipleofMatrixInterleaving Copyright©2006–2015,TexasInstrumentsIncorporated DetailedDescription 25 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com 5.11 Radio Control SIDLE SLEEP CAL_COMPLETE SPWD 0 MANCAL IDLE CSn=0 3,4,5 1 SXOFF SCAL CSn=0 STX | SFSTXON XOFF 2 FS_WAKEUP 6,7 FS_AUTOCAL=01 & STX | SFSTXON FS_AUTOCAL=00|10|11 & CALIBRATE STX | SFSTXON 8 CAL_COMPLETE SETTLING 9,10 SFSTXON FSTXON 18 STX STX TXOFF_MODE=01 TX TXOFF_MODE=10 19,20 TXFIFO_UNDERFLOW TXOFF_MODE=00 & FS_AUTOCAL=10|11 TXOFF_MODE=00 CALIBRATE TX_UNDERFLOW & 12 22 FS_AUTOCAL=00|01 SFTX IDLE 1 Figure5-11.RadioControlStateDiagram 26 DetailedDescription Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 CC1150 has a built-in state machine that is used to switch between different operations states (modes). The change of state is done either by using command strobes or by internal events such as TX FIFO underflow. A simplified state diagram, together with typical usage and current consumption, is shown in Figure 5-2. The complete radio control state diagram is shown in Figure 5-11. The numbers refer to the state number readableintheMARCSTATEstatusregister.Thisfunctionalityisprimarilyfortestpurposes. 5.11.1 Power On Start-up Sequence When the power supply is turned on, the system must be reset. This is achieved by one of the two sequences described in Section 5.11.1.1 or Section 5.11.1.2, that is, automatic power-on reset or manual reset. After the automatic power-on reset or manual reset it is also recommended to change the signal that is output on the GDO0 pin. The default setting is to output a clock signal with a frequency of CLK_XOSC/192, but to optimize performance in TX, an alternative GDO setting should be selected from thesettingsfoundinTable5-10. 5.11.1.1 AutomaticPOR A power-on reset circuit is included in the CC1150. The minimum requirements stated in Section 4.7 must be followed for the power-on reset to function properly. The internal power-up sequence is completed when CHIP_RDYn goes low. CHIP_RDYn is observed on the SO pin after CSn is pulled low. See Section 10.1formoredetailsonCHIP_RDYn. WhentheCC1150resetiscompletedthechipwillbeintheIDLEstateandthecrystaloscillatorrunning.If the chip has had sufficient time for the crystal oscillator and voltage regulator to stabilize after the power- on-reset, the SO pin will go low immediately after taking CSn low. If CSn is taken low before reset is completed the SO pin will first go high, indicating that the crystal oscillator and voltage regulator is not stabilized,beforegoinglowasshowninFigure5-12. CSn SO XOSC Stable Figure5-12.Power-onReset 5.11.1.2 ManualReset The other global reset possibility on CC1150 is the SRES command strobe. By issuing this strobe, all internal registers and states are set to the default, IDLE state. The power-up sequence is as follows (see Figure5-13): • SetSCLK=1andSI=0. • StrobeCSnlow/high.MakesuretoholdCSnhighforatleast40 µsrelativetopullingCSnlow. • PullCSnlowandwaitforSOtogolow(CHIP_RDYn). • IssuetheSRESstrobeontheSIline. • WhenSOgoeslowagain,resetiscompleteandthechipisintheIDLEstate. Copyright©2006–2015,TexasInstrumentsIncorporated DetailedDescription 27 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com XOSC and voltage regulator switched on 40 µs CSn SO XOSC Stable SI SRES Figure5-13.Power-upwithSRES NOTE The above reset procedure is only required just after the power supply is first turned on. If the user wants to reset the CC1150 after this, it is only necessary to issue an SRES commandstrobe. It is recommended to always send a SRES command strobe on the SPI interface after power-on even thoughpower-onresetisused. 5.11.2 Crystal Control The crystal oscillator is automatically turned on when CSn goes low. It will be turned off if the SXOFF or SPWD command strobes are issued; the state machine then goes to XOFF or SLEEP respectively. This can only be done from IDLE state. The XOSC will be turned off when CSn is released (goes high). The XOSC will be automatically turned on again when CSn goes low. The state machine will then go to the IDLE state. The SO pin on the SPI interface must be pulled low before the SPI interface is ready to be used;asdescribedinSection5.5.1. Crystal oscillator start-up time depends on crystal ESR and load capacitances. The electrical specification forthecrystaloscillatorcanbefoundinSection4.7. 5.11.3 Voltage Regulator Control The voltage regulator to the digital core is controlled by the radio controller. When the chip enters the SLEEP state, which is the state with the lowest current consumption, the voltage regulator is disabled. This occurs after CSn is released when a SPWD command strobe has been sent on the SPI interface. The chip is then in the SLEEP state. Setting CSn low again will turn on the regulator and crystal oscillator andmakethechipentertheIDLEstate. On the CC1150, all register values (with the exception of the MCSM0.PO_TIMEOUT field) are lost in the SLEEP state. After the chip gets back to the IDLE state, the registers will have default (reset) contents andmustbereprogrammedovertheSPIinterface. 5.11.4 Active Mode TheactivetransmitmodeisactivatedbytheMCUbyusingtheSTXcommandstrobe. The frequency synthesizer must be calibrated regularly. CC1150 has one manual calibration option (using the SCAL strobe), and three automatic calibration options, controlled by the MCSM0.FS_AUTOCAL setting: • CalibratewhengoingfromIDLEtoTX(orFSTXON) • CalibratewhengoingfromTXtoIDLE • CalibrateeveryfourthtimewhengoingfromTXtoIDLE 28 DetailedDescription Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 The calibration takes a constant number of XOSC cycles; see Table 5-6 for timing details. When TX is active,thechipwillremainintheTXstateuntilthecurrentpackethasbeensuccessfullytransmitted.Then thestatewillchangeasindicatedbytheMCSM1.TXOFF_MODEsetting.Thepossibledestinationsare: • IDLE • FSTXON:FrequencysynthesizeronandreadyattheTXfrequency.ActivateTXwithSTX. • TX:Startsendingpreambles The SIDLE command strobe can always be used to force the radio controller to go to the IDLE state. Note that if the radio goes from TX to IDLE by issuing an SIDLE strobe, the automatic calibration-when-going- from-TX-to-IDLEwillnotbeperformed. 5.11.5 Timing The radio controller controls most timing in CC1150, such as synthesizer calibration and PLL lock. Table 5-6 shows timing in crystal clock cycles for key state transitions. Timing from IDLE to TX is constant, dependent on the auto calibration setting. The calibration time is constant 18739 clock periods. PowerontimeandXOSCstart-uptimesarevariable,butwithinthelimitsstatedinSection4.7. NOTE Inafrequencyhoppingspreadspectrumoramulti-channelprotocol,thecalibrationtimecan bereducedfrom721µstoapproximately150µs.ThisisexplainedinSection5.19.2. Table5-6.StateTransitionTiming DESCRIPTION XOSCPERIODS 26MHzCRYSTAL IdletoTX/FSTXON,nocalibration 2298 88.4µs IdletoTX/FSTXON,withcalibration ≈21037 809µs TXtoIDLE,nocalibration 2 0.1µs TXtoIDLE,includingcalibration ≈18739 721µs Manualcalibration ≈18739 721µs 5.12 Data FIFO The CC1150 contains a 64 byte FIFO for data to be transmitted. The SPI interface is used for writing to the TX FIFO. Section 10.5 contains details on the SPI FIFO access. The FIFO controller will detect underflowintheTXFIFO. WhenwritingtotheTXFIFO,itistheresponsibilityoftheMCUtoavoidTXFIFOoverflow.Thiswillnotbe detectedbytheCC1150.ATXFIFOoverflowwillresultinanerrorintheTXFIFOcontent. Table5-7.FIFO_THRSettings andtheCorrespondingFIFO Thresholds BYTESinTX FIFO_THR FIFO 0000 61 0001 57 0010 53 0011 49 0100 45 0101 41 0110 37 Copyright©2006–2015,TexasInstrumentsIncorporated DetailedDescription 29 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com Table5-7.FIFO_THRSettings andtheCorrespondingFIFO Thresholds(continued) BYTESinTX FIFO_THR FIFO 0111 33 1000 29 1001 25 1010 21 1011 17 1100 13 1101 9 1110 5 1111 1 The chip status byte that is available on the SO pin while transferring the SPI address contains the fill gradeoftheTXFIFO.Section5.5.1containsmoredetailsonthis. ThenumberofbytesintheTXFIFOcanalsobereadfromtheTXBYTES.NUM_TXBYTESstatusregister. The 4-bit FIFOTHR.FIFO_THR setting is used to program the FIFO threshold point. Table 5-7 lists the 16 FIFO_THRsettingsandthecorrespondingthresholdsfortheTXFIFO. FIFO_THR=13 Underflow 8 bytes margin TXFIFO Figure5-14.ExampleofFIFOatThreshold A flag will assert when the number of bytes in the FIFO is equal to or higher than the programmed threshold. The flag is used to generate the FIFO status signals that can be viewed on the GDO pins (see Section5.17). Figure 5-15 shows the number of bytes in the TX FIFO when the threshold flag toggles, in the case of FIFO_THR=13. Figure 5-15 shows the flag as the FIFO is filled above the threshold, and then drained below. 30 DetailedDescription Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 NUM_TXBYTES 6 7 8 9 10 9 8 7 6 GDO Figure5-15.FIFO_THR=13versusNumberofBytesinFIFO 5.13 Frequency Programming The frequency programming in CC1150 is designed to minimize the programming needed in a channel- orientedsystem. To set up a system with channel numbers, the desired channel spacing is programmed with the MDMCFG0.CHANSPC_M and MDMCFG1.CHANSPC_E registers. The channel spacing registers are mantissaandexponentrespectively. The base or start frequency is set by the 24-bit frequency word located in the FREQ2, FREQ1 and FREQ0 registers. This word will typically be set to the centre of the lowest channel frequency that is to be used. The desired channel number is programmed with the 8-bit channel number register, CHANNR.CHAN, whichismultipliedbythechanneloffset.TheresultantcarrierfrequencyisgivenbyEquation5. f = fXOSC ´(FREQ+CHAN´((256+CHANSPC_M)´2CHANSPC_E-2)) carrier 216 (5) With a 26-MHz crystal, the maximum channel spacing is 405 kHz. To get, for example, 1-MHz channel spacingonsolutionistouse333-kHzchannelspacingandselecteachthirdchannelinCHANNR.CHAN. If any frequency programming register is altered when the frequency synthesizer is running, the synthesizer may give an undesired response. Hence, the frequency programming should only be updated whentheradioisintheIDLEstate. 5.14 VCO TheVCOiscompletelyintegratedon-chip. 5.14.1 VCO and PLL Self-Calibration The VCO characteristics will vary with temperature and supply voltage changes, as well as the desired operating frequency. In order to ensure reliable operation, CC1150 includes frequency synthesizer self- calibration circuitry. This calibration should be done regularly, and must be performed after turning on power and before using a new frequency (or channel). The number of XOSC cycles for completing the PLLcalibrationisgiveninTable5-6. The calibration can be initiated automatically or manually. The synthesizer can be automatically calibrated each time the synthesizer is turned on, or each time the synthesizer is turned off. This is configured with theMCSM0.FS_AUTOCALregistersetting. In manual mode, the calibration is initiated when the SCAL command strobe is activated in the IDLE mode. The calibration values are not maintained in sleep mode. Therefore, the CC1150 must be recalibrated afterreprogrammingtheconfigurationregisterswhenthechiphasbeenintheSLEEPstate. To check that the PLL is in lock the user can program register IOCFGx.GDOx_CFG to 0x0A and use the lock detector output available on the GDOx pin as an interrupt for the MCU (x = 0, 1, or 2). A positive transition on the GDOx pin means that the PLL is in lock. As an alternative the user can read register FSCAL1. The PLL is in lock if the register content is different from 0x3F. See more information in the CC1150ErrataNotes[8]. For more robust operation the source code could include a check so that the PLL is re-calibrated until PLL lockisachievedifthePLLdoesnotlockthefirsttime. Copyright©2006–2015,TexasInstrumentsIncorporated DetailedDescription 31 SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 SWRS037B–JANUARY2006–REVISEDMARCH2015 www.ti.com 5.15 Voltage Regulators CC1150 contains several on-chip linear voltage regulators, which generate the supply voltage needed by low-voltage modules. These voltage regulators are invisible to the user, and can be viewed as integral parts of the various modules. The user must however make sure that the absolute maximum ratings and requiredpinvoltagesinSection4.1andTable3-1arenotexceeded. Setting the CSn pin low turns on the voltage regulator to the digital core and start the crystal oscillator. The SO pin on the SPI interface must go low before the first positive edge on the SCLK (setup time is s giveninTable5-1). If the chip is programmed to enter power-down mode (SPWD strobe issued), the power will be turned off afterCSngoeshigh.ThepowerandcrystaloscillatorwillbeturnedonagainwhenCSngoeslow. The voltage regulator for the digital core requires one external decoupling capacitor. The voltage regulator outputshouldonlybeusedfordrivingtheCC1150. 5.16 Output Power Programming The RF output power level from the device has two levels of programmability, as illustrated in Figure 5-16. Firstly, the special PATABLE register can hold up to eight user selected output power settings. Secondly, the 3-bit FREND0.PA_POWER value selects the PATABLE entry to use. This two-level functionality provides flexible PA power ramp up and ramp down at the start and end of transmission, as well as ASK modulation shaping. In each case, all the PA power settings in the PATABLE from index 0 up to the FREND0.PA_POWERvalueareused. The power ramping at the start and at the end of a packet can be turned off by setting FREND0.PA_POWER to zero and then programming the desired output power to index 0 in the PATABLE. If OOK modulation is used, the logic 0 and logic 1 power levels shall be programmed to index 0 and 1 respectively. Table 5-8 contains recommended PATABLE settings for various output levels and frequency bands. DN012 [3] gives complete tables for the different frequency bands. Using PA settings from 0x61 to 0x6F is not recommended. Table 5-9contains output power and current consumption for default PATABLE setting (0xC6). PATABLE must be programmed in burst mode if you want to write to other entries than PATABLE[0]. See Section5.5.6forPATABLEprogrammingdetails. PATABLE(7)[7:0] ThePAusesthis PATABLE(6)[7:0] setting. PATABLE(5)[7:0] PATABLE(4)[7:0] Settings0toPA_POWERare PATABLE(3)[7:0] usedduringramp-upatstartof transmissionandramp-downat PATABLE(2)[7:0] endoftransmission,andfor PATABLE(1)[7:0] ASK/OOKmodulation. PATABLE(0)[7:0] IndexintoPATABLE(7:0) TheSmartRFTM Studiosoftware e.g6 shouldbeusedtoobtainoptimum PATABLEsettingsforvarious PA_POWER[2:0] outputpowers. inFREND0register Figure5-16.PA_POWERandPATABLE 32 DetailedDescription Copyright©2006–2015,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLinks:CC1150

CC1150 www.ti.com SWRS037B–JANUARY2006–REVISEDMARCH2015 Table5-8.OptimumPATABLESettingsforVariousOutputPowerLevelsandFrequencyBands 315MHz 433MHz 868MHz 915MHz OUTPUT POWER CURRENT CURRENT CURRENT CURRENT [dBm] SETTING CONSUMPTION, SETTING CONSUMPTION, SETTING CONSUMPTION, SETTING CONSUMPTION, TYP.[mA] TYP.[mA] TYP.[mA] TYP.[mA] –30 0x12 9.9 0x03 10.8 0x03 11.2 0x03 11.1 –20 0x0E 10.4 0x0E 11.4 0x0C 11.7 0x0F 11.7 –10 0x26 12.5 0x26 13.3 0x26 13.7 0x34 13.6 –5 0x57 12.2 0x57 12.9 0x57 13.3 0x56 13.3 0 0x60 14.1 0x60 14.6 0x60 15.5 0x50 15.2 3 0x8B 15.8 0x8A 16.5 0x8A 17.4 0x89 17.4 7 0xCC 21.4 0xC8 23 0xCC 24.4 0xC8 24.6 10 0xC4 25.6 0xC2 26.1 0xC3 29.3 0xC0 29.3 Table5-9.OutputPowerandCurrentConsumptionforDefaultPATABLESetting 315MHz 433MHz 868MHz 915MHz DEFAULT POWER OUTPUT CURRENT OUTPUT CURRENT OUTPUT CURRENT OUTPUT CURRENT SETTING POWER CONSUMPTION, POWER CONSUMPTION, POWER CONSUMPTION, POWER CONSUMPTION, [dBm] TYP.[mA] [dBm] TYP.[mA] [dBm] TYP.[mA] [dBm] TYP.[mA] 0xC6 9.3 24.4 8.1 23.9 8.9 27.3 7.7 25.5 5.16.1 Shaping and PA Ramping With ASK modulation, up to eight power settings are used for shaping. The modulator contains a counter that counts up when transmitting a one and down when transmitting a zero. The counter counts at a rate equal to 8 times the symbol rate. The counter saturates at FREND0.PA_POWER and 0 respectively. This counter value is used as an index for a lookup in the power table. Thus, in order to utilize the whole table, FREND0.PA_POWER should be 7 when ASK is active. The shaping of the ASK signal is dependent on theconfigurationofthePATABLE.Figure5-17showssomeexamplesofASKshaping. NOTE The OOK/ASK pulse shaping feature on the CC1150 is only supported for output power levelsbelow–1dBm. Output Power PATABLE[7] PATABLE[6] PATABLE[5] PATABLE[4] PATABLE[3] PATABLE[2] PATABLE[1] PATABLE[0] Time 1 0 0 1 0 1 1 0 Bit Sequence FREND0.PA_POWER = 3 FREND0.PA_POWER = 7 Figure5-17.ShapingofASKSignal 5.17 General Purpose and Test Output Control Pins The two digital output pins GDO0 and GDO1 are general control pins. Their functions are programmed by IOCFG0.GDO0_CFG and IOCFG1.GDO1_CFG respectively. Table 5-10 shows the different signals that canbemonitoredontheGDOpins.ThesesignalscanbeusedasaninterrupttotheMCU. GDO1 is the same pin as the SO pin on the SPI interface, thus the output programmed on this pin will only be valid when CSn is high. The default value for GDO1 is 3-stated, which is useful when the SPI interfaceissharedwithotherdevices. Copyright©2006–2015,TexasInstrumentsIncorporated DetailedDescription 33 SubmitDocumentationFeedback ProductFolderLinks:CC1150