ICGOO在线商城 > 集成电路(IC) > 数据采集 - 模拟前端(AFE) > AFE7225IRGC25

- 型号: AFE7225IRGC25

- 制造商: Texas Instruments

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

AFE7225IRGC25产品简介:

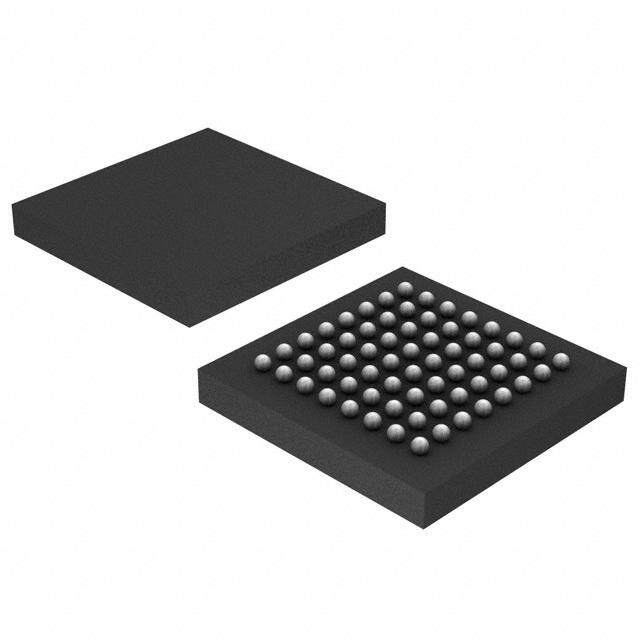

ICGOO电子元器件商城为您提供AFE7225IRGC25由Texas Instruments设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 AFE7225IRGC25价格参考。Texas InstrumentsAFE7225IRGC25封装/规格:数据采集 - 模拟前端(AFE), 4 Channel AFE 12 Bit 650mW 64-VQFN (9x9)。您可以下载AFE7225IRGC25参考资料、Datasheet数据手册功能说明书,资料中有AFE7225IRGC25 详细功能的应用电路图电压和使用方法及教程。

Texas Instruments(德州仪器)的AFE7225IRGC25是一款高性能模拟前端(AFE)器件,主要面向通信和射频(RF)应用领域。该器件集成了双通道14位ADC(模数转换器)和DAC(数模转换器),支持高精度信号采集与处理,适用于需要高性能信号转换的场景。 其主要应用场景包括: 1. 无线通信基础设施:如基站、微波回传系统和软件定义无线电(SDR),AFE7225可实现高带宽信号的采集与处理,满足4G/5G通信系统对高精度射频信号处理的需求。 2. 测试与测量设备:用于示波器、频谱分析仪等仪器中,提供高精度、高采样率的信号采集能力,确保测量结果的准确性与稳定性。 3. 工业自动化与控制系统:在高精度传感器信号采集和处理中发挥重要作用,适用于需要多通道、高速模拟信号转换的工业场景。 4. 医疗成像设备:如超声波设备等,AFE7225的高分辨率和低噪声特性有助于提升图像质量和诊断精度。 该器件采用先进的CMOS工艺制造,具有低功耗、高性能的特点,适用于对空间和能效有要求的嵌入式系统设计。其封装为64引脚QFN(RGC),便于集成于各类高性能电子系统中。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC)半导体 |

| 描述 | IC AFE 12BIT 125/250MSPS 64VQFN射频前端 Dual 12B,125MSPS ADC |

| 产品分类 | 数据采集 - 模拟前端 (AFE)集成电路 - IC |

| 品牌 | Texas Instruments |

| 产品手册 | |

| 产品图片 |

|

| rohs | 符合RoHS无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | RF集成电路,射频前端,Texas Instruments AFE7225IRGC25- |

| 数据手册 | http://www.ti.com/lit/pdf/slos711a |

| 产品型号 | AFE7225IRGC25 |

| PCN封装 | |

| 产品种类 | 射频前端 |

| 位数 | 12 |

| 供应商器件封装 | 64-VQFN(9x9) |

| 其它名称 | 296-30112-2 |

| 制造商产品页 | http://www.ti.com/general/docs/suppproductinfo.tsp?distId=10&orderablePartNumber=AFE7225IRGC25 |

| 功率(W) | 650mW |

| 包装 | 带卷 (TR) |

| 商标 | Texas Instruments |

| 安装风格 | SMD/SMT |

| 封装 | Reel |

| 封装/外壳 | 64-VFQFN 裸露焊盘 |

| 封装/箱体 | VQFN-64 |

| 工作电源电压 | 1.7 V to 1.9 V, 2.85 V to 3.6 V |

| 工作频率 | 10 kHz |

| 工厂包装数量 | 25 |

| 带宽 | 550 MHz |

| 最大工作温度 | + 85 C |

| 最大数据速率 | 250 MSPs |

| 最小工作温度 | - 40 C |

| 标准包装 | 25 |

| 电压-电源,数字 | 1.7 V ~ 1.9 V |

| 电压-电源,模拟 | 2.85 V ~ 3.6 V |

| 电源电流 | 115 mA |

| 类型 | RF Front End |

| 系列 | AFE7225 |

| 通道数 | 4 |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 Analog Front End Wideband Mixed-Signal Transceiver CheckforSamples:AFE7222,AFE7225 1 INTRODUCTION 1.1 FEATURES 1 • AFE7225 – TXPathInterpolationby2or4 – Dual12-Bit250MSPSTXDACs – RXPathDecimationby2 – Dual12-Bit125MSPSRXADCs – 3.0V/1.8VSupplies,LowPower • AFE7222 – FastWakeupModesforHalf-Duplex – Dual12-Bit130MSPSTXDACs – CoarseorFineDigitalMixer – Dual12-Bit65MSPSRXADCs – QuadratureModulationCorrections • OPTIONS – ClockInputDivide/Multiply – Dual12-BitAuxiliaryDACs – SerialLVDSorInterleavedParallelCMOS Interface – DualInput12-BitAuxiliaryADC – 64-PinQFNPackage(9mm ×9mm) 1.2 APPLICATIONS • Portable,LowPowerRadio • WirelessInfrastructure • Point-to-PointRadio • Pico-CellBTS 1.3 DESCRIPTION The AFE7225/7222 is an analog front end designed for full- or half-duplex radios. Over-sampling transmit 12-bit DACs provide output frequencies from baseband to Nyquist. Under-sampling receive 12-bit ADCs allow analog inputs from baseband to ~230MHz. Most blocks within the AFE7225/7222 are independently controlled for optimization of power consumption versus utilization. Two auxiliary control 12-bit DACs and a dual input auxiliary monitoring 12-bit ADC are available via serial interface. Digital features include QMC (quadrature modulation correction), interpolation, decimation, RMS/peak power meter and mixers with independentNCOsforRXandTXpath. The AFE7225/7222 is available in a 64-pin 9x9mm QFN package (RGC). The AFE7225/7222 is built on Texas Instrument’s low power analog CMOS process and is specified over the full industrial temperature range(–40°Cto85°C). 1 Pleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsofTexas Instrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet. PRODUCTIONDATAinformationiscurrentasofpublicationdate.Productsconformto Copyright©2011,TexasInstrumentsIncorporated specifications per the terms of the Texas Instruments standard warranty. Production processingdoesnotnecessarilyincludetestingofallparameters.

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com Thesedeviceshavelimitedbuilt-inESDprotection.Theleadsshouldbeshortedtogetherorthedeviceplacedinconductivefoam duringstorageorhandlingtopreventelectrostaticdamagetotheMOSgates. 1.4 DETAILED BLOCK DIAGRAM IIIINNNNNPNP____BAAB____AAAADDDDCCCC RRXX11AA22DDbbCC AB QMCOffset QMCGain/Phase ±Fs/4CoarseMixer FineMixer /2HBFDecimation erialLVDSorarallelCMOS AVD1OD2u3-tB_pAiutUtAsXD C= 3 V SP VCM SYNC SYNC SYNC AVDD3_DAC = 3 V ADC CLK RX RMS/ SYNC DVDD18_DAC=1.8V Peak NCO CLKINP Clock Power Meter AVDD18_ADC=1.8V CLKINN Divide/Multiply SYNC SYNCSYNC RIenfteerrennacle DVDD18=1.8V DAC CLK BIASJ SYNC NCO DVDD18_CLK=1.8V IIIIOOOOUUUUTTTTNNPP____AABB____DDDDAAAACCCC TTXX 11DD22AAbbCC AB QMCOffset InverseSINC QMCGain/Phase ±Fs/4CoarseMixer FineMixer 2xHBFInterpolation 2xHBFInterpolation SerialLVDSorParallelCMOS(8deepFIFO) The1Irnm2p-aBult iPts DadAC=Ground SYNC SYNC SYNC SYNC AUXDAC_A 12bAux DAC SYNC SYNC SYNC AUXDAC_B 12bAux DAC SEN SCLK SDATA SPI Interface,Registers and Control AUXADC_A 2-1 12bAuxADC SDOUT AUXADC_B MUX RESET PDN SYNC Figure1-1.BlockDiagramofAFE7222/AFE7225 2 INTRODUCTION Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 2 DEVICE INFORMATION 2.1 PACKAGE/ORDERING INFORMATION SPECIFIED TRANSPORT PACKAGE PACKAGE ORDERING PRODUCT PACKAGE-LEAD TEMPERATURE MEDIA, DESIGNATOR MARKING NUMBER RANGE QUANTITY AFE7222IRGCT TapeandReel AFE7222 QFN-64 RGC –40°Cto85°C AFE7222I AFE7222IRGCR TapeandReel AFE7222IRGC25 TapeandReel AFE7225IRGCT TapeandReel AFE7225 QFN-64 RGC –40°Cto85°C AFE7225I AFE7225IRGCR TapeandReel AFE7225IRGC25 TapeandReel 2.2 DEVICE PINOUT, CMOS INPUT/OUTPUT MODE RGC Package (Top View) C C D D 0 1 2 3 4 5 A A A A A A A A D18_ D18_ ET UT K TA DAT DAT DAT DAT DAT DAT D18 D M D S O L A N N C C C C C C D V C V E D C D E D D D D D D D V A V A R S S S S P A A A A A A D 6463 62 61 60 59 58 57 56 55 54 53 52 51 50 49 AVDD18_ADC 1 48 ADCDATA6 INN_B_ADC 2 47 ADC_DCLKOUT INP_B_ADC 3 46 ADCDATA7 Thermal pad connected to ground AVDD18_ADC 4 45 ADCDATA8 INN_A_ADC 5 44 ADCDATA9 INP_A_ADC 6 43 ADCDATA10 AVDD18_ADC 7 42 ADCDATA11 CLKINN 8 6464-QQFNFN 41 DVDD18 CLKINP 9 40 SYNCIN DVDD18_CLK 10 39 DACDATA0 AVDD3_DAC 11 38 DACDATA1 IOUTP_A_DAC 12 37 DACDATA2 IOUTN_A_DAC 13 36 DACDATA3 AVDD3_DAC 14 35 DACDATA4 IOUTP_B_DAC 15 34 DAC_DCLKIN IOUTN_B_DAC 16 33 DACDATA5 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 C J C A B X A B C 1 0 9 8 7 6 8 3_DA BIAS 8_DA DAC_ DAC_ 3_AU ADC_ ADC_ 8_AD ATA1 ATA1 DATA DATA DATA DATA VDD1 D 1 X X D X X 1 D D C C C C D D D U U D U U D C C A A A A V D A A V A A D A A D D D D A V A V D D D A Figure2-1.DevicePinout,CMOSInput/OutputMode Copyright©2011,TexasInstrumentsIncorporated DEVICEINFORMATION 3 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com Table2-1. PinConfiguration:CMOSInput/OutputMode PIN DESCRIPTION NO. NAME 1 AVDD18_ADC 1.8VsupplyforRXADCs 2 INN_B_ADC RXADCchannelBanaloginput,negative 3 INP_B_ADC RXADCchannelBanaloginput,positive 4 AVDD18_ADC 1.8VsupplyforRXADCs 5 INN_A_ADC RXADCchannelAanaloginput,negative 6 INP_A_ADC RXADCchannelAanaloginput,positive 7 AVDD18_ADC 1.8VsupplyforRXADCs 8 CLKINN mainclockinput,negativesideifdifferentialmode,TXsideifsingle-ended2clockmode 9 CLKINP mainclockinput,positivesideifdifferentialmode,RXsideifsingle-ended2clockmode 10 DVDD18_CLK 1.8VsupplyforClockingcircuit 11 AVDD3_DAC 3VsupplyforTXDACs 12 IOUTP_A_DAC TXDACchannelAcurrentoutput,positive(currentsinkDACs) 13 IOUTN_A_DAC TXDACchannelAcurrentoutput,negative(currentsinkDACs) 14 AVDD3_DAC 3VsupplyforTXDACs 15 IOUTP_B_DAC TXDACchannelBcurrentoutput,positive(currentsinkDACs) 16 IOUTN_B_DAC TXDACchannelBcurrentoutput,negative(currentsinkDACs) 17 AVDD3_DAC 3VsupplyforTXDACs setstheTXDACoutputcurrent(resistorfrompintoground).Use960Ohmtosetafullscalecurrentof 18 BIASJ 20mA. 19 DVDD18_DAC 1.8VDACdigitalsupply 20 AUXDAC_A auxiliaryDACchannelAoutput,currentsourcingupto7.5mA(SPIprogrammable) 21 AUXDAC_B auxiliaryDACchannelBoutput,currentsourcingupto7.5mA(SPIprogrammable) 22 AVDD3_AUX 3VsupplyforauxiliaryADC/DACs 23 AUXADC_A auxiliaryADCchannelAinput 24 AUXADC_B auxiliaryADCchannelBinput 25 AVDD18_ADC 1.8VsupplyforRXADCs 26 DACDATA11 CMOSdatainputforTXdata,MSBofTXDACs 27 DACDATA10 CMOSdatainputforTXdata 28 DACDATA9 CMOSdatainputforTXdata 29 DACDATA8 CMOSdatainputforTXdata 30 DACDATA7 CMOSdatainputforTXdata 31 DACDATA6 CMOSdatainputforTXdata 32 DVDD18 1.8Vsupplyfordigitalinterface 33 DACDATA5 CMOSdatainputforTXdata 34 DAC_DCLKIN CMOSclockinputforTXdata.Sendclockwithdata. 35 DACDATA4 CMOSdatainputforTXdata 36 DACDATA3 CMOSdatainputforTXdata 37 DACDATA2 CMOSdatainputforTXdata 38 DACDATA1 CMOSdatainputforTXdata 39 DACDATA0 CMOSdatainputforTXdata.LSBofTXDACs 40 SYNCIN CMOSsyncinput.UsedtoresetinternalclockdividersandresetTXdataFIFOpointer 41 DVDD18 1.8Vsupplyfordigitalinterface 42 ADCDATA11 CMOSdataoutputforRXdata,MSBofRXADCs 43 ADCDATA10 CMOSdataoutputforRXdata 44 ADCDATA9 CMOSdataoutputforRXdata 45 ADCDATA8 CMOSdataoutputforRXdata 46 ADCDATA7 CMOSdataoutputforRXdata 4 DEVICEINFORMATION Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 Table2-1. PinConfiguration:CMOSInput/OutputMode(continued) PIN DESCRIPTION NO. NAME 47 ADC_DCLKOUT CMOSclockoutputforRXdata 48 ADCDATA6 CMOSdataoutputforRXdata 49 DVDD18 1.8Vsupplyfordigitalinterface 50 ADCDATA5 CMOSdataoutputforRXdata 51 ADCDATA4 CMOSdataoutputforRXdata 52 ADCDATA3 CMOSdataoutputforRXdata 53 ADCDATA2 CMOSdataoutputforRXdata 54 ADCDATA1 CMOSdataoutputforRXdata 55 ADCDATA0 CMOSdataoutputforRXdata,LSBofRXADCs Canbeprogrammedasglobalpowerdown(deepsleep),fastrecoverypowerdown(lightsleep)orTX/RX 56 PDN switch.Activehigh. 57 SEN SPIenable(1.8VCMOS) 58 SDATA SPIdatainput(1.8VCMOS) 59 SCLK SPIclockinput(1.8VCMOS) 60 SDOUT SPIdataoutput(1.8VCMOS) 61 RESET ResettheSPI.Activehigh(1.8VCMOS). 62 AVDD18_ADC 1.8VsupplyforRXADCs Commonmodevoltageoutput.OutputstheidealcommonmodeinputvoltagefortheADC.Nominally 63 VCM around0.95V. 64 AVDD18_ADC 1.8VsupplyforRXADCs Thermal VSS Connectthermalpadtotheboardground pad Copyright©2011,TexasInstrumentsIncorporated DEVICEINFORMATION 5 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com 2.3 DEVICE PINOUT, LVDS INPUT/OUTPUT MODE RGC Package (Top View) P N P N P N T T C C _1 _1 _0 _0 U U D D A A A A O O A A T T T T K K 18_ 18_ T T A _DA _DA _DA _DA DCL DCL 18 D D E U K T A A A A _ _ D D M D S O L A N N C C C C C C D V C V E D C D E D D D D D D D V A V A R S S S S P A A A A A A D 6463 62 61 60 59 58 57 56 55 54 53 52 51 50 49 AVDD18_ADC 1 48 NC INN_B_ADC 2 47 ADC_FCLKOUTP INP_B_ADC 3 46 ADC_FCLKOUTN Thermal pad connected to ground AVDD18_ADC 4 45 ADCB_DATA_0P INN_A_ADC 5 44 ADCB_DATA_0N INP_A_ADC 6 43 ADCB_DATA_1P AVDD18_ADC 7 42 ADCB_DATA_1N CLKINN 8 64-QQFNFN 41 DVDD18 CLKINP 9 40 SYNCINN DVDD18_CLK 10 39 SYNCINP AVDD3_DAC 11 38 DACB_DATA_1N IOUTP_A_DAC 12 37 DACB_DATA_1P IOUTN_A_DAC 13 36 DACB_DATA_0N AVDD3_DAC 14 35 DACB_DATA_0P IOUTP_B_DAC 15 34 DAC_DCLKINN IOUTN_B_DAC 16 33 DAC_DCLKINP 1718 19 20 21 22 23 24 25 26 27 28 29 30 31 32 C J C A B X A B C P N P N P N 8 A S A _ _ U _ _ D 1 1 0 0 N N 1 AVDD3_D BIA DVDD18_D AUXDAC AUXDAC AVDD3_A AUXADC AUXADC AVDD18_A ACA_DATA_ ACA_DATA_ ACA_DATA_ ACA_DATA_ DAC_FCLKI DAC_FCLKI DVDD D D D D Figure2-2.DevicePinout,LVDSInput/OutputMode Table2-2.PinConfiguration:LVDSInput/OutputMode PIN DESCRIPTION NO. NAME 1 AVDD18_ADC 1.8VsupplyforRXADCs 2 INN_B_ADC RXADCchannelBanaloginput,negative 3 INP_B_ADC RXADCchannelBanaloginput,positive 4 AVDD18_ADC 1.8VsupplyforRXADCs 5 INN_A_ADC RXADCchannelAanaloginput,negative 6 INP_A_ADC RXADCchannelAanaloginput,positive 7 AVDD18_ADC 1.8VsupplyforRXADCs 8 CLKINN mainclockinput,negativesideifdifferentialmode,TXsideifsingle-ended2clockmode 6 DEVICEINFORMATION Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 Table2-2.PinConfiguration:LVDSInput/OutputMode(continued) PIN DESCRIPTION NO. NAME 9 CLKINP mainclockinput,positivesideifdifferentialmode,RXsideifsingle-ended2clockmode 10 DVDD18_CLK 1.8VsupplyforClockingcircuit 11 AVDD3_DAC 3VsupplyforTXDACs 12 IOUTP_A_DAC TXDACchannelAcurrentoutput,positive(currentsinkDACs) 13 IOUTN_A_DAC TXDACchannelAcurrentoutput,negative(currentsinkDACs) 14 AVDD3_DAC 3VsupplyforTXDACs 15 IOUTP_B_DAC TXDACchannelBcurrentoutput,positive(currentsinkDACs) 16 IOUTN_B_DAC TXDACchannelBcurrentoutput,negative(currentsinkDACs) 17 AVDD3_DAC 3VsupplyforTXDACs setstheTXDACoutputcurrent(resistorfrompintoground).Use960Ohmtosetafullscalecurrentof 18 BIASJ 20mA. 19 DVDD18_DAC 1.8VDACdigitalsupply 20 AUXDAC_A auxiliaryDACchannelAoutput,currentsourcingupto7.5mA(SPIprogrammable) 21 AUXDAC_B auxiliaryDACchannelBoutput,currentsourcingupto7.5mA(SPIprogrammable) 22 AVDD3_AUX 3VsupplyforauxiliaryADC/DACs 23 AUXADC_A auxiliaryADCchannelAinput 24 AUXADC_B auxiliaryADCchannelBinput 25 AVDD18_ADC 1.8VsupplyforRXADCs 26,27 LVDSWire1datainputforChannelATXdata–inactivein1-wiremode,LSBbytein2-wiremode 26 DAC_DATA_11 Positive 27 DAC_DATA_10 Negative 28,29 LVDSWire0datainputforChannelATXdata–activein1-wiremode,MSBbytein2-wiremode 28 DAC_DATA_9 Positive 29 DAC_DATA_8 Negative 30,31 LVDSframeclockinput 30 DAC_FCLKINP Positive 31 DAC_FCLKINN Negative 32 DVDD18 1.8Vsupplyfordigitalinterface 33,34 LVDSbitclockinput 33 DAC_DCLKINP Positive 34 DAC_DCLKINN Negative 35,36 LVDSWire0datainputforChannelBTXdata–activein1-wiremode,LSBbytein2-wiremode 35 DACB_DATA_0P Positive 36 DACB_DATA_0N Negative 37,38 LVDSWire1datainputforChannelBTXdata–inactivein1-wiremode,MSBbytein2-wiremode 37 DACB_DATA_1P Positive 38 DACB_DATA_1N Negative 39,40 LVDSSYNCinput–UsedtoresetinternalclockdividersandresetTXdataFIFOpointer 39 SYNCINP Positive 40 SYNCINN Negative 41 DVDD18 1.8Vsupplyfordigitalinterface 42,43 LVDSWire1dataoutputforChannelBRXdata–inactivein1-wiremode,MSBbytein2-wiremode 42 ADCB_DATA_1N Positive 43 ADCB_DATA_1P Negative 44,45 LVDSWire0dataoutputforChannelBRXdata–activein1-wiremode,LSBbytein2-wiremode 44 ADCB_DATA_0N Positive 45 ADCB_DATA_0P Negative Copyright©2011,TexasInstrumentsIncorporated DEVICEINFORMATION 7 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com Table2-2.PinConfiguration:LVDSInput/OutputMode(continued) PIN DESCRIPTION NO. NAME 46,47 LVDSframeclockoutput 46 ADC_FCLKOUTN Positive 47 ADC_FCLKOUTP Negative 48 NC NoConnect 49 DVDD18 1.8Vsupplyfordigitalinterface 50,51 LVDSbitclockoutput 50 ADC_DCLKOUTN Positive 51 ADCDCLKOUTP Negative 52,53 LVDSWire0dataoutputforChannelARXdata–activein1-wiremode,MSBbytein2-wiremode 52 ADCA_DATA_0N Positive 53 ADCA_DATA_0P Negative 54,55 LVDSWire1dataoutputforChannelARXdata–inactivein1-wiremode,LSBbytein2-wiremode 54 ADCA_DATA_1N Positive 55 ADCA_DATA_1P Negative Canbeprogrammedasglobalpowerdown(deepsleep),fastrecoverypowerdown(lightsleep)orTX/RX 56 PDN switch.Activehigh. 57 SEN SPIenable(1.8VCMOS) 58 SDATA SPIdatainput(1.8VCMOS) 59 SCLK SPIclockinput(1.8VCMOS) 60 SDOUT SPIdataoutput(1.8VCMOS) 61 RESET ResettheSPI.Activehigh(1.8VCMOS). 62 AVDD18_ADC 1.8VsupplyforRXADCs Commonmodevoltageoutput.OutputstheidealcommonmodeinputvoltagefortheADC.Nominally 63 VCM around0.95V. 64 AVDD18_ADC 1.8VsupplyforRXADCs Thermal VSS Connectthermalpadtotheboardground pad 8 DEVICEINFORMATION Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 3 ELECTRICAL SPECIFICATIONS 3.1 ABSOLUTE MAXIMUM RATINGS(1) overoperatingfree-airtemperaturerange(unlessotherwisenoted) MIN MAX UNIT Supplyvoltagerange,*VDD3* –0.3 3.6 V Supplyvoltagerange,*VDD18* –0.3 2.1 V Voltagebetweeen*VDD3*to*VDD18* –2.4 3.9 V INP_A_ADC,INM_A_ADC,INP_B_ADC,INM_B_ADC,AUXADC_A,AUXADC_B,CLKINN,CLKINP –0.3 2.1 V RESET,SCLK,SDATASEN –0.3 3.9 V DAC*_DATA_nP/M,DAC_DCLK –0.3 2.1 V T Operatingfree-airtemperaturerange –40 85 °C A T Operatingjunctiontamperaturerange 125 °C J T Storagetemperaturerange –65 150 °C stg ESDratingHumanBodyModel(HBM) 2 kV (1) Stressesbeyondthoselistedunderabsolutemaximumratingsmaycausepermanentdamagetothedevice.Thesearestressratings onlyandfunctionaloperationofthedeviceattheseoranyotherconditionsbeyondthoseindicatedunderrecommendedoperating conditionsisnotimplied.Exposuretoabsolutemaximumratedconditionsforextendedperiodsmayaffectdevicereliability. 3.2 THERMAL INFORMATION AFE7222/AFE7225 THERMALMETRIC RGCPACKAGE UNITS 64PINS θ Junction-to-ambientthermalresistance 22.8 JA θ Junction-to-case(top)thermalresistance 6.7 JCtop θ Junction-to-boardthermalresistance 2.3 JB °C/W ψ Junction-to-topcharacterizationparameter 0.1 JT ψ Junction-to-boardcharacterizationparameter 2.2 JB θ Junction-to-case(bottom)thermalresistance 0.2 JCbot 3.3 RECOMMENDED OPERATING CONDITIONS overoperatingfree-airtemperaturerange(unlessotherwisenoted) AFE7222 AFE7225 PARAMETER TESTCONDITIONS UNIT MIN TYP MAX MIN TYP MAX DVDD18voltagerange 1.7 1.8 1.9 1.7 1.8 1.9 V AVDD3voltagerange 2.85 3.0 3.6 2.85 3.0 3.6 V Commonmodevoltageat VCM-0.05 VCM VCM+0.05 VCM–0.05 VCM VCM+0.05 V ADCinputpins Commonmodevoltageat AVDD3 AVDD3 V DACoutputpins ADC_CLKspeed(1) 2.5 65 2.5 125 MSPS DAC_CLKspeed(1) 1 130 1 250 MSPS (1) SeeTable10-1andTable10-2forcorrespondingmaximuminterfacerates. Copyright©2011,TexasInstrumentsIncorporated ELECTRICALSPECIFICATIONS 9 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com 3.4 SUPPLY CHARACTERISTICS AVDD18_ADC=1.8V,DVDD18_CLK=1.8V,DVDD18=1.8V,DVDD18_DAC=1.8V,AVDD3_DAC=3.0V,AVDD3_AUX=3.0V, IOUTFS=20mA,typicalvaluesatT =25°C,fulltemperaturerangeisT =–40°CtoT =85°C,unlessotherwisenoted. A MIN MAX PARAMETER TESTCONDITIONS AFE7222 AFE7225 DualRXADC,DualTXDAC DualRXADC,DualTX withInterpolateby2,CMOS DACwithInterpolateby2, interface 2-wireLVDSinterface FADCCLK=65MSPS FADCCLK=125MSPS UNIT fADCIN=10MHz fADCIN=10MHz FDACCLK=130MSPS FDACCLK=250MSPS fDACOUT=10MHz fDACOUT=10MHz MIN TYP MAX MIN TYP MAX RXandTXactive. Powerdissipation,fullduplexmode 545 610 577 650 mW NoinputsignalappliedonADCandDAC RXactive,TXinlightsleep,TXclockis Powerdissipation,halfduplexRXmode off. 360 420 362 417 mW NoinputsignalappliedonADCandDAC TXactive,RXinlightsleep,RXclockis Powerdissipation,halfduplexTXmode on. 338 370 419 482 mW NoinputsignalappliedonADCandDAC Globalpowerdownenabled 12 40 12 40 Fastrecoverypowerdownenabled, 140 165 215 246 TX/RXsleeping,clockson PowerdissipationinSleepmodes mW Fastrecoverypowerdownenabled, TX/RXsleeping,TXclockoff,RXclock 120 165 177 231 on. Differentialinputclock 25 25 Globalpowerdown,RXrecoverytime µs Single-endedinputclock 20 20 GlobalpowerdowninLowpowerRX Differentialinputclock 25 25 CMOSmode,RXrecoverytime(ADC µs runningatlessthan40MSPS) Single-endedinputclock 13 13 Differentialinputclock 25 25 Globalpowerdown,TXrecoverytime µs Single-endedinputclock 5 5 RXrecoverytimeinfastrecoverymode RXclockisONduringpowerdown 5 5 µs TXrecoverytimeinfastrecoverymode 5 5 µs RXrecoverytimefromRXpowerdown RXclockisonduringpowerdown 5 5 µs TXrecoverytimefromTXpowerdown 5 5 µs 10 ELECTRICALSPECIFICATIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 3.5 RX ADC ELECTRICAL CHARACTERISTICS TypicalvaluesatT =25°C,fulltemperaturerangeisT =–40°CtoT =85°C,suppliesatnominalvoltages,50%clock A MIN MAX dutycycle,LVDSoutputinterface,–1dBFSdifferentialinput,unlessotherwisenoted. AFE7222 AFE7225 PARAMETER TESTCONDITIONS UNIT MIN TYP MAX MIN TYP MAX MaximumClockRate 65 125 MSPS Resolution 12 12 bits ANALOGINPUTS Differentialinputrange 2 2 Vpp V Commonmodeoutputvoltage 0.95 0.95 V CM Inputresistance(DC) Differential >1 >1 MΩ Inputcapacitance Differential 4 4 pF Analoginputbandwidth 550 550 MHz CMRR Commonmoderejectionratio Fin=10MHz 40 40 dB DYNAMICACCURACY NoMissingCodes, DNL Differentiallinearityerror –0.95 ±0.5 1.4 –0.95 ±0.5 1.4 LSB Fin=10MHz INL Integrallinearityerror Fin=10MHz –1.7 ±0.2 1.7 –1.7 ±0.2 1.7 LSB Offseterror –15 2 15 –15 3 15 mV Offsettemperatureco-efficient >0.005 >0.005 mV/°C Gainerrorasaresultofinternalreference –2.5 2.5 –2.5 2.5 %FS inaccuracyalone–EGREF Gainerrorofchannelalone–EGCHAN ±1 ±1 %FS DYNAMICACCHARACTERISTICS Fin=10MHz 67.5 70.5 67 70.7 dBFS SNR Signal-to-noiseratio(1) Fin=70MHz 70 70.1 dBFS Fin=140MHz 68.7 69.5 dBFS Fin=10MHz 73 85 73 84 dBc SFDR Spuriousfreedynamicrange(1) Fin=70MHz 81 79 dBc Fin=140MHz 77 76 dBc (1) Upto65MSPStypicalSNRandSFDRperformanceinCMOSinterfaceissameaswithLVDSinterface. Copyright©2011,TexasInstrumentsIncorporated ELECTRICALSPECIFICATIONS 11 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com 3.6 TX DAC ELECTRICAL CHARACTERISTICS TypicalvaluesatT =25°C,fulltemperaturerangeisT =–40°CtoT =85°C,50%clockdutycycle,suppliesatnominal A MIN MAX voltages,I =20mA,DACoutputcommonmodevoltageisAVDD3=3.0V,unlessotherwisenoted. OUTFS AFE7222 AFE7225 PARAMETER TESTCONDITIONS UNIT MIN TYP MAX MIN TYP MAX Maximumclockoutputrate 130 250 MSPS Resolution 12 12 Bits ANALOGOUTPUTS Fullscaleoutputcurrent,perDAC 2 20 2 20 mA Outputvoltagecompliancerange IOUTFS=20mA, AVDD3_DAC–0.5 AVDD3_DAC+0.5 AVDD3_DAC–0.5 AVDD3_DAC+0.5 V Currentsinkoutput Outputresistance 300 300 kΩ Outputcapacitance 5 5 pF Offseterror Midcodeoffset ±0.03 ±0.03 %FS(1) Gainerror Internalreference ±1 ±1 %FS(1) Gainmismatch InternalreferencedualDAC ±0.5 ±0.5 %FS(1) DCPERFORMANCE INL Integralnon-linearity Fout=10MHz –2 ±1 2 –2 ±1 2 LSB DNL Differentialnon-linearity Fout=10MHz ±0.5 ±0.5 LSB ACPERFORMANCE Noisespectraldensity Fout=10MHz,0dBFS 145.5 149 148.5 151 dBc/Hz Fout=10MHz,0dBFS 70 76 70 76 dBc SFDR Spuriousfreedynamicrange Fout=20MHz,0dBFS 75 74 dBc Fout=5.1/6.1MHz, IMD Inter-modulationdistortion 73 73 dBc –7dBFSeach DACclock=122.88MSPS, 75 Fout=30.72MHz ACLR Adjacentchannelleakageratio dB DACclock=245.76MSPS, 73 Fout=61.44MHz (1) %FS=%DifferentialFullScale 3.7 AUXILIARY ADC ELECTRICAL CHARACTERISTICS TypicalvaluesatT =25°C,fulltemperaturerangeisT =–40°CtoT =85°C,suppliesatnominalvoltages,unless A MIN MAX otherwisenoted. PARAMETER TESTCONDITIONS AFE7222/AFE7225 UNIT MIN TYP MAX MaximumClockRate 100 kSPS Resolution 12 Bits ANALOGINPUTS Inputvoltagerange 1.5 V Inputcapacitance 4 pF Maximuminputsignalfrequency 10 kHz DCPERFORMANCE INL Integralnon-linearity Staticconditions(nearDCinput) –4.5 ±2 4.5 LSB 12 ELECTRICALSPECIFICATIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 3.8 AUXILIARY DAC ELECTRICAL CHARACTERISTICS TypicalvaluesatT =25°C,fulltemperaturerangeisT =–40°CtoT =85°C,suppliesatnominalvoltages,I = A MIN MAX OUTFS 5mA,300Ωtermination,unlessotherwisenoted. AFE7222/AFE7225 PARAMETER TESTCONDITIONS UNIT MIN TYP MAX MaximumClockRate ContinuousrefreshofAUXDACChannelAfromSDATA 3.33(1) MSPS andChannelBfromSDOUT Resolution 12 Bits ANALOGOUTPUTS Outputcurrent,perauxDAC 2.5 7.5 mA Outputvoltagecompliancerange 1.5 V DYNAMICPERFORMANCE INL Integralnon-linearity Staticconditions(nearDCinput) –1.7 ±0.5 1.7 LSB DNL Differentialnon-linearity Staticconditions(nearDCinput) ±0.3 LSB (1) 12bitsx(1/SCLK)indirectaccessmode,SCLKmaxlimitis40MHz 3.9 DIGITAL CHARACTERISTICS TheDCspecificationsrefertotheconditionwherethedigitaloutputsarenotswitching,butarepermanentlyatavalidlogic level0or1.AVDD18*,DVDD18*=1.8V,AVDD3*=3.0V PARAMETER TESTCONDITIONS MIN TYP MAX UNIT DIGITALINPUTS–RESET,SCLK,SDATA,SEN,PDN Allthesepinssupport1.8Vand3VCMOS High-levelinputvoltage 1.3 V logiclevels. Low-levelinputvoltage 0.4 V DACDIGITALINPUTSINCMOSINTERFACEMODE High-levelinputvoltage 1.8VCMOSlogiclevelsonly 1.3 V Low-levelinputvoltage 0.4 V DACDIGITALINPUTSINLVDSINTERFACEMODE StandardswingLVDSwithexternal100ohms V High-leveldifferentialinputvoltage 350 mV IDH termination StandardswingLVDSwithexternal100ohms V Low-leveldifferentialinputvoltage –350 mV IDL termination V Inputcommon-modevoltage 1.2 V ICM DIGITALOUTPUTS–CMOSINTERFACE–SDOUT,ADCOUTPUTS(INCMOSINTERFACEMODE) High-leveloutputvoltage DVDD18–0.1 DVDD18 V Low-leveloutputvoltage 0 0.1 V DIGITALOUTPUTS–LVDSINTERFACE(ADCOUTPUTSINLVDSMODE) V High-leveldifferentialoutputvoltage StandardswingLVDS 235 375 mV ODH V Low-leveldifferentialoutputvoltage StandardswingLVDS –375 –235 mV ODL V Outputcommon-modevoltage 0.9 1.05 1.2 V OCM Copyright©2011,TexasInstrumentsIncorporated ELECTRICALSPECIFICATIONS 13 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com 3.10 TIMING REQUIREMENTS TypicalvaluesatT =25°C,fulltemperaturerangeisT =–40°CtoT =85°C,unlessotherwisenoted. A MIN MAX AFE7222 AFE7225 PARAMETER TESTCONDITIONS UNIT MIN TYP MAX MIN TYP MAX SCLKINPUT t CLOCKperiod 25 25 ns SCLK t CLOCKpulsewidthhigh 12.5 12.5 ns SCLKH Assuming50/50dutycycle t CLOCKpulsewidthlow 12.5 12.5 ns SCLKL 3.11 TIMING REQUIREMENTS FOR RECEIVE PATH – LVDS AND CMOS MODES Typicalvaluesareat25°C,AVDD3_DAC=3.0V,AVDD3_AUX=3.0V,AVDD18_ADC=1.8V,DVDD18_CLK=1.8V, DVDD18_DAC=1.8V,DVDD18=1.8V,samplingfrequency=125MSPS,sinewaveinputclock,1.5V clockamplitude, pp C =5pF (1),R =100Ω (2),unlessotherwisenoted.MinandmaxvaluesareacrossthefulltemperaturerangeT = LOAD LOAD MIN -40°CtoT =85°C,AVDD3_DAC=3.0V,AVDD3_AUX=3.0V,AVDD18_ADC=1.8V,DVDD18_CLK=1.8V, MAX DVDD18_DAC=1.8V,DVDD18=1.7Vto1.9V PARAMETER TESTCONDITIONS MIN TYP MAX UNIT T Aperturedelay 2 ns A Aperturedelaymatching Betweentwochannelsonthesamedevice ±120 ps Aperturedelaymatching BetweentwodevicesatsametemperatureandDVDD18supply ±450 ps Jitteraddedbyinternalclockdistribution,specifiedasitrelates T Aperturejitter 250 fsrms J tothereceiveADC DefaultMode 16 ADCLatency(3) MixerEnabled(RX_MIXER_EN=1) 33 clock cycles RXQMCGainPhaseCorrectionEnabled 22 (RX_QMC_CORR_ENA=1,RX_QMC_CORR_ENB=1) LVDSOUTPUTINTERFACE 2-WIREMODE,DDRCLOCK(4),Samplingfrequency=125MSPS t Datasetuptime (5) Datavalid(5)tozero-crossingofCLKOUTP 0.29 0.42 ns su t Dataholdtime (5) Zero-crossingofCLKOUTPtodatabecominginvalid (5) 0.3 0.47 ns h t Clockpropagationdelay Inputclockrisingedgecross-overtooutputclockrisingedge t =t ns PDI PDI DELAY cross-over10MSPS≤Samplingfrequency≤125MSPSTs= tdelay 1/Samplingfrequency 11.5 13.8 15.5 ns Variationoft BetweentwodevicesatsametemperatureandDVDD18supply ±300 ps delay Dutycycleofdifferentialclock,(ADC_DCLKOUTP- LVDSbitclockdutycycle ADC_DCLKOUTM)10MSPS≤Samplingfrequency≤125 50% MSPS 2-WIREMODE,SDRCLOCK(4),Samplingfrequency=65MSPS t Datasetuptime (5) Datavalid (5)tozero-crossingofCLKOUTP 0.85 1.08 ns su t Dataholdtime (5) Zero-crossingofCLKOUTPtodatabecominginvalid (5) 1.08 1.21 ns h Inputclockrisingedgecross-overtooutputclockrisingedge t Clockpropagationdelay cross-over10MSPS≤Samplingfrequency≤65MSPSTs= t =0.5*Ts+t ns PDI PDI DELAY 1/Samplingfrequency t 11.5 14 16.5 ns delay Variationoft BetweentwodevicesatsametemperatureandDVDD18supply ±300 ps delay Dutycycleofdifferentialclock,(CLKOUTP-CLKOUTM)10 LVDSbitclockdutycycle 50% MSPS≤Samplingfrequency≤65MSPS 1-WIREMODE(DDRCLOCKONLY)(4),Samplingfrequency=65MSPS t Datasetuptime (5) Datavalid (5)tozero-crossingofCLKOUTP 0.25 0.39 ns su (1) C istheeffectiveexternalsingle-endedloadcapacitancebetweeneachoutputpinandground LOAD (2) R isthedifferentialloadresistancebetweentheLVDSoutputpair. LOAD (3) Athigherfrequencies,t isgreaterthanoneclockperiodandoveralllatency=ADClatency+1. PDI (4) Measurementsaredonewithatransmissionlineof100-Ωcharacteristicimpedancebetweenthedeviceandtheload.Setupandhold timespecificationstakeintoaccounttheeffectofjitterontheoutputdataandclock. (5) DatavalidreferstoLOGICHIGHof+100.0mVandLOGICLOWof-100.0mV. 14 ELECTRICALSPECIFICATIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 Typicalvaluesareat25°C,AVDD3_DAC=3.0V,AVDD3_AUX=3.0V,AVDD18_ADC=1.8V,DVDD18_CLK=1.8V, DVDD18_DAC=1.8V,DVDD18=1.8V,samplingfrequency=125MSPS,sinewaveinputclock,1.5V clockamplitude, pp C =5pF(1),R =100Ω(2),unlessotherwisenoted.MinandmaxvaluesareacrossthefulltemperaturerangeT = LOAD LOAD MIN -40°CtoT =85°C,AVDD3_DAC=3.0V,AVDD3_AUX=3.0V,AVDD18_ADC=1.8V,DVDD18_CLK=1.8V, MAX DVDD18_DAC=1.8V,DVDD18=1.7Vto1.9V PARAMETER TESTCONDITIONS MIN TYP MAX UNIT t Dataholdtime (5) Zero-crossingofCLKOUTPtodatabecominginvalid (5) 0.26 0.4 ns h Inputclockrisingedgecross-overtooutputclockrisingedge t Clockpropagationdelay cross-over10MSPS≤Samplingfrequency≤65MSPSTs= t =0.5*Ts+t ns PDI PDI DELAY 1/Samplingfrequency t 11.5 13.5 15.5 ns delay Variationoft BetweentwodevicesatsametemperatureandDVDD18supply ±300 ps delay Dutycycleofdifferentialclock,(CLKOUTP-CLKOUTM)10 LVDSbitclockdutycycle 50% MSPS≤Samplingfrequency≤65MSPS COMMON Risetimemeasuredfrom-100mVto+100mVFalltime t , Datarisetime,Datafall RISE measuredfrom+100mVto-100mV10MSPS≤Sampling 0.08 ns t time FALL frequency≤125MSPS Risetimemeasuredfrom-100mVto+100mVFalltime t , Outputclockrisetime, CLKRISE measuredfrom+100mVto-100mV10MSPS≤Sampling 0.1 ns t Outputclockfalltime CLKFALL frequency≤125MSPS CMOSOUTPUTINTERFACE (6),Samplingfrequency=105MSPS(7) t Datasetuptime (8) Datavalidtocross-overofADC_DCLKOUT (8) 0.5 1.4 ns su t Dataholdtime (8) Cross-overofADC_DCLKOUTtodatabecominginvalid (8) 1.4 1.8 ns h Inputclockrisingedgecross-overtooutputclockrisingedge t Clockpropagationdelay cross-over10MSPS≤Samplingfrequency≤105MSPSTs= t =0.5*Ts+t ns PDI PDI DELAY 1/Samplingfrequency t 14 16.5 19 ns delay Variationoft BetweentwodevicesatsametemperatureandDVDD18supply ±350 ps delay Dutycycleofoutputclock,ADC_DCLKOUT10MSPS≤ Outputclockdutycycle 46% Samplingfrequency≤105MSPS Risetimemeasuredfrom20%to80%ofDVDD18Falltime t , Datarisetime,Datafall RISE measuredfrom80%to20%ofDVDD181≤Sampling 0.76 ns t time FALL frequency≤105MSPS Risetimemeasuredfrom20%to80%ofDVDD18Falltime t , Outputclockrisetime, CLKRISE measuredfrom80%to20%ofDRVDD1≤Samplingfrequency 0.74 ns t Outputclockfalltime CLKFALL ≤105MSPS (6) ForFs>105MSPS,itisrecommendedtouseexternalclockfordatacaptureandNOTthedeviceoutputclocksignal (ADC_DCLKOUT). (7) ForFs>65MSPS,CMOSoutputbuffersstrengthisincreasedbywritingserialregisterbitsSTR_CTRL<1:0>='10'. (8) DatavalidreferstoLOGICHIGHof1.26VandLOGICLOWof0.54V. Copyright©2011,TexasInstrumentsIncorporated ELECTRICALSPECIFICATIONS 15 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com Table3-1.LVDSTimingsatLowerSamplingFrequencies 2-WIREMODEDDRCLOCK Setuptime,ns Holdtime,ns SamplingFrequency,MSPS MIN TYP MAX MIN TYP MAX 20 3.75 3.93 3.64 3.9 35 1.99 2.18 1.96 2.2 50 1.28 1.46 1.28 1.51 65 0.84 1.06 0.85 1.14 80 0.59 0.81 0.70 0.90 95 0.46 0.67 0.49 0.70 110 0.31 0.52 0.36 0.58 125 0.29 0.42 0.30 0.47 Clockpropagationdelay,t =t t ,ns PDI DELAY DELAY Fs≤125MSPS 11.5 13.8 15.5 11.5 13.8 15.5 2-WIREMODE,SDRCLOCK Setuptime,ns Holdtime,ns SamplingFrequency,MSPS MIN TYP MAX MIN TYP MAX 10 8.14 8.32 7.90 8.06 20 3.89 4.08 3.85 4.01 30 2.33 2.6 2.51 2.71 40 1.68 1.91 1.81 2.03 50 1.22 1.48 1.41 1.64 65 0.85 1.08 1.08 1.21 t ,ns DELAY Fs≤65MSPS Clockpropagationdelay,t =0.5*Ts+t PDI DELAY 11.5 14 16.5 1-WIREMODE,DDRCLOCK Setuptime,ns Holdtime,ns SamplingFrequency,MSPS MIN TYP MAX MIN TYP MAX 20 1.71 1.90 1.67 1.92 35 0.77 0.99 0.82 1.04 50 0.36 0.61 0.39 0.62 65 0.25 0.39 0.26 0.40 t ,ns DELAY Fs≤65MSPS Clockpropagationdelay,t =0.5*Ts+t MIN TYP MAX PDI DELAY 11.50 13.50 15.50 Table3-2.CMOSTimingsatLowerSamplingFrequencies TimingsspecifiedwithrespecttoCLKOUT SamplingFrequency,MSPS Setuptime,ns Holdtime,ns MIN TYP MAX MIN TYP MAX 20 10.90 11.50 11.22 11.60 40 4.62 5.25 4.99 5.33 65 2.06 2.66 2.46 2.86 90 1 1.9 1.8 2.3 105 0.5 1.4 1.4 1.8 t ,ns DELAY Fs≤105MSPS Clockpropagationdelay,t =0.5*Ts+t MIN TYP MAX PDI DELAY 14 16.50 19 16 ELECTRICALSPECIFICATIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 3.12 TIMING REQUIREMENTS FOR TRANSMIT PATH – LVDS AND CMOS MODES(1) Typicalvaluesareat25°C,AVDD3_DAC=3.0V,AVDD3_AUX=3.0V,AVDD18_ADC=1.8V,DVDD18_CLK=1.8V, DVDD18_DAC=1.8V,DVDD18=1.8V,sinewaveinputclock,1.5V clockamplitude,unlessotherwisenoted.Minand pp maxvaluesareacrossthefulltemperaturerangeT =-40°CtoT =85°C,AVDD3_DAC=3.0V,AVDD3_AUX=3.0V, MIN MAX AVDD18_ADC=1.8V,DVDD18_CLK=1.8V,DVDD18_DAC=1.8V,DVDD18=1.7Vto1.9V PARAMETER TESTCONDITIONS MIN TYP MAX UNIT clock DACLatency DefaultMode 16 cycles LVDSINPUTINTERFACE t Datasetuptime Datavalid(2)tozero-crossingofDAC_DCLKINP 0.5 ns su t Dataholdtime Zero-crossingofDAC_DCLKINPtodatabecominginvalid (2) 0.3 ns h CMOSINPUTINTERFACE t Datasetuptime Datavalidtocross-overofDAC_DCLKIN (3) 0.3 ns su t Dataholdtime Cross-overofDAC_DCLKINtodatabecominginvalid (3) 0.5 ns h (1) Timingparametersareensuredbydesignandcharacterizationandnottestedinproduction. (2) DatavalidreferstoLOGICHIGHof+100mVandLOGICLOWof-100mV. (3) DatavalidreferstoLOGICHIGHof1.26VandLOGICLOWof0.54V. Copyright©2011,TexasInstrumentsIncorporated ELECTRICALSPECIFICATIONS 17 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com 4 SERIAL PERIPHERAL INTERFACE 4.1 DESCRIPTION The SPI (serial peripheral interface) is used to program the AFE7225/7222. It is used to read data from and write data to the registers, from the rms/peak power meter and the auxiliary ADC. It is also used to senddatatotheauxiliaryDACs. The interface is formed with pins SEN (Serial Interface Enable), SCLK (Serial Interface Clock), SDATA (Serialinterfaceinputdata)andSDOUT(Serialinterfaceoutputdata). The serial shift of bits into the device is enabled when SEN is low. Serial data SDATA is latched at every rising edge of SCLK when SEN is active (low). The SPI uses a 20-bit serial arrangement – the first 12-bits aretheregisteraddress,andthelast8-bitsrepresentthedatafortheaddress. The interface can work with SCLK frequency from a frequency of 40MHz down to a few Hertz and also withnon-50%SCLKdutycycle. Direct access modes exist for reading from the auxiliary ADC and writing to the auxiliary DACs by using theSPIpins. REGISTERADDRESS REGISTER DATA (A11:A0) (D7:D0) SDATA SCLK SEN Figure4-1.Timing Address bits (A11:A8) are referred to as the Page address of the register, and address bits (A7:A0) are referredtoastheRowaddressoftheregister. 4.2 SPI REGISTER READOUT Data stored in a register corresponding to a page can be read out by programming the readout bit corresponding to that page. The read out bit for a register addressed by (A11:A0) is the D0 bit of the registerwiththePageaddressof(A11:A8)androwaddressof00000000. Toreadoutaparticularregister,thefollowingstepshavetobefollowed: 1. ConfigureSDOUTasadigitaloutputpinusingbits 2. Settheregisterspecificreadoutbit.Thisbitcanbesetbywritingthefollowing20-bitsequence– A11:A8,00000000,00000001where(A11..A8)isthepageaddressoftheregisterwhosecontentsare desiredtobereadout 3. Onceinthereadoutmode,writetheaddressoftheregistertobereadoutasbelow.Thenewdata writeisignored.ThedatacontentsoftheregistercomeoutseriallyontheSDOUTpinasshown below. 18 SERIALPERIPHERALINTERFACE Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 REGISTER DATA REGISTERADDRESS (D7:D0) (A11:A0) Ignored SDATA SCLK SEN SDOUT Contents of addressed register (D7..D0) Figure4-2.Timing 4. Ifthenextregistertobereadouthasthesamepageaddress,thenrepeatStep3withthenew addresstobereadout. 5. Toexittheregisterreadoutmode,writeA11:A8,00000000,00000000. Copyright©2011,TexasInstrumentsIncorporated SERIALPERIPHERALINTERFACE 19 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com 5 REGISTER DESCRIPTIONS 5.1 TRANSMIT DIGITAL SIGNAL CHAIN REGISTERS SYNC NCO DTTAXXC B_AC ooLuuKttppuutt QMCOffset InverseSINC QMCGain/Phase CoarseMixer(CMIX) FineMixer 2xInterpolationTxFIR2 2xInterpolationTxFIR1 8deepFIFO (TQT(IXX cc BhhAa aiinnnnnpnpeueulltt)) SYNC SYNC SYNC SYNC DAC_DCLKIN DAC_CLK %1,2,4 Figure5-1.SignalChain Input data is shifted into the 8-deep FIFO at the rate of DAC_DCLKIN. At its output, the FIFO hands off thedatausingadividedversionoftheDAC_CLK(basedontheinterpolationfactor).Therestofthesignal chainrunsoffDAC_CLKanditsdividedderivatives. RegisterName–CONFIG0–Address0x103,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> Tx_BYP_SRC TX_BYP TX_ChB_PDN_SRC TX_CHB_PDN TX_CHA_PDN_SRC TX_CHA_PDN TX_DIS TX_DIS – Disables the digital signal chain of both channels in TX . All blocks in digital signal chain are powereddown,andtheoutputisDACmid-code.Note:theDACsarenotpowereddowninthismode. TX_CHA_PDN – Powers down digital signal chain of Channel A in Tx . Output of the channel is mid code. SetTX_CHA_PDN_SRCforthistotakeeffect. TX_CHA_PDN_SRC– SettingthiscausesthevalueprogrammedintoTX_CHA_PDNtotakeeffect. TX_CHB_PDN – Powers down digital signal chain of Channel B in Tx . Output of the channel is mid code. SetTX_CHB_PDN_SRCforthistotakeeffect. TX_CHB_PDN_SRC– SettingthiscausesthevalueprogrammedintoTX_CHB_PDNtotakeeffect. Note that when in default mode of operation (none of the register-selectable digital features enabled), all 4 of above bits (TX_CHA_PDN, TX_CHA_PDN_SRC, TX_CHB_PDN, TX_CHB_PDN_SRC) have to be set together to '1' for them to take effect. However, if any of the digital features (like interpolation, Fine mixer, Coarse mixer, or QMC gain/phase or offset) are enabled, then the channel A can be independently powered down using bits TX_CHA_PDN and TX_CHA_PDN_SRC, and channel B can be independently powereddownusingbitsTX_CHB_PDNandTX_CHB_PDN_SRC. TX_BYP – The inputs to both the Tx channels are directly passed to the outputs. FIFO is bypassed. Set TX_BYP_SRCforthistotakeeffect. TX_BYP_SRC– SettingthiscausesthevalueprogrammedintoTX_BYPtotakeeffect. 20 REGISTERDESCRIPTIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 RegisterName–CONFIG1–Address0x104,Default=0x10 <7> <6> <5> <4> <3> <2> <1> <0> MASK_2_AWAY_DET TX_CHB_8_IP_EN TX_CHA_8_IP_EN TX_CHA_8_IP_EN – Enable the 8- sample mode FIFO mode for Channel A . The 8 samples written into theregs0x11Fto0x12Earerepeatedlycycledthrough,andsenttotheDACA.Thisisausefuldiagnostic mode. TX_CHB_8_IP_EN – Enable the 8- sample mode FIFO mode for Channel B . The 8 samples written into theregs0x12Fto0x13Earerepeatedlycycledthrough,andsenttotheDACB. MASK_2_AWAY_DET – Refer CONFIG58 for a description of the collision condition in the FIFO. Setting the MASK_2_AWAY_DET prevents the 2-away condition from triggering collision detection. If collision detection is enabled, and 2-away condition occurs, the output samples will be forced to DAC mid code, unlessMASK_2_AWAY_DETisset. RegisterName–CONFIG2–Address0x105,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> STORE_FIFO_PTRS RX_TX_LPBK_SRC RX_TX_LPBK STORE_FIFO_PTRS–Whenset,theFIFOReadandWritepointersarewrittenintotheregister0x141at the rate of the divided DAC_CLK. The pointers are no longer written to the serial interface regs when Registerreadoutisenabled. RX_TX_LPBK – When this bit and RX_TX_LPBK_SRC are both set , the input to the TX signal chain is tapped from the the final output of the RX signal chain. As is obvious, the ADC_CLK and DAC_CLK rates shouldbethesamewhenusingthismode. RX_TX_LPBK_SRC – When this bit and RX_TX_LPBK are both set , the input to the TX signal chain is tappedfromthethefinaloutputoftheRXsignalchain TheRXtoTXloopbackisshownbelow.Thedottedarrowsillustratetheloopbackpath. Note that though the data going into the TX digital signal chain is looped back internally from the RX Digital signal chain, it is still required to give an active DAC_DCLKIN in this mode because the Tx FIFO requiresitforproperdatatransfer. INP_A_ADC 12b LAIN orOS INN_A_ADC RXADCA GITACH VDSCM 12-bitADC IINNPN__BB__AADDCC RX1A2DbC B RXDIGNAL erialLarallel Output SI SP IIOOUUTTNP__AA__DDAACC TX 1D2AbCA GITALCHAIN MUX VDSorCMOS 12-bit DAC IIOOUUTTNP__BB__DDAACC TX 1D2AbC B TXDISIGNAL MUX SerialLParallel Input Figure5-2.Loopback Copyright©2011,TexasInstrumentsIncorporated REGISTERDESCRIPTIONS 21 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com RegisterName–CONFIG3–Address0x106,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> FIR2B_MODE FIR1B_MODE FIR2A_MODE FIR1A_MODE TX_INT_MODE_SRC TX_INT_MODE(1:0) TX_INT_MODE(1:0)–Specifiestheinterpolationfactor.Tousethismode,setTX_INT_MODE_SRCto1. VALUE INTERPOLATIONFACTOR 0 1 1 2 2 4 3 4 While interpolating by a factor of 2, the DAC_DCLKIN rate should be set to half of the DAC_CLK rate. While interpolating by a factor of 4, the DAC_DCLKIN rate should be set to one fourth of the DAC_CLK rate. In interpolate by 2 mode , TxFIR1 alone is used. In Interpolate by 4 mode, both TxFIR1, and TxFIR2 areused. TX_INT_MODE_SRC– Needstobesetto1whenprogrammingTX_INT_MODE(1:0) FIR1A_MODE – Specifies whether TxFIR1 in Channel A is in low pass or high pass mode . Set this bit to configurethefilterinhighpassmode.Ininterpolateby4mode,alwayssetTxFIR1tolowpassmode. FIR2A_MODE – Specifies whether TxFIR2 in Channel A is in low pass or high pass mode. Set this bit to configurethefilterinhighpassmode FIR1B_MODE – Specifies whether TxFIR1 in Channel B is in low pass or high pass mode. Set this bit to configurethefilterinhighpassmode FIR2B_MODE – Specifies whether TxFIR2 in Channel B is in low pass or high pass mode . Set this bit to configurethefilterinhighpassmode RegisterName–CONFIG4–Address0x107,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> TX_CMIX_PHASE(1:0) TX_CMIX_PHASE_INCR TX_CMIX_MODE(1:0) TX_CMIX_EN TX_CMIX_EN– EnablestheTxCoarseMixer. TX_CMIX_MODE (1:0) – Specifies the mode in which the TX CMIX is configured. Set TX_CMIX_EN for thistotakeeffect. VALUE MIXINGMODE 0 Normal(Lowpass) 1 Fs/2(HighPass)–realmixingmode 2 +Fs/4–complexmixingmode 3 –Fs/4–complexmixingmode TX_CMIX_PHASE_INCR– ThisbitisamethodtocontrolthemixingphasewithoutusingtheSYNCpin.A 0to1transitiononthisbitcausesthephaseofmixingintheTXCMIXtobeincrementedby1withrespect to the current phase of mixing. To increment the phase of mixing more than once, clear and then set this bit once again. Syncing needs to be disabled for Tx CMIX for this mode to work. (This means that global syncingshouldbedisabled,andCMIX-specifcsyncingshouldalsobedisabled). TX_CMIX_PHASE (1:0) – The value programmed into this is applied as the current TX CMIX phase, when the CMIX is synced, Syncing needs to be enabled for CMIX for this mode to work. This mode is meanttosynchronizethephaseofmixingacrossmultiplechips. 22 REGISTERDESCRIPTIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 RegisterName–CONFIG5–Address0x108,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> Tx_INV_SINC_FIL_EN_SRC Tx_INV_SINC_FIL_EN TX_DIV_PHASE_ TX_DIV_PHASE(1:0) TX_DATA_ROUTE_ INCR ORDER(1:0) TX_DATA_ROUTE_ORDER (1:0) – Specifies the order in which the A and B outputs of the TX Signal ChainareroutedtotheDACs VALUE ROUTINGORDER 0 Normal–DACAgetsTXOutputAandDACBgetsTXOutputB 1 BothDACsgetTXOutputA 2 BothDACsgetTXOutputB 3 Swapped–DACAgetsTXOutputBandDACBgetsTXOutputA TX_DIV_PHASE (1:0) – The value programmed into this is applied as the TX Divider phase, when the divider is synced. The divider here refers to the clock divider that divides the DAC_CLK depending on the interpolation factor. For division by 2, there are 2 possible phases of the divided clock. For division by 4, there are 4 possible phases. If the divider phase is not synced across chips, then it will cause a phase uncertaintyintheDACanalogoutput,andcanalsocauseuncertaintyintheCMIXoperation. TX_DIV_PHASE_INCR – This bit is a method to control the phase of the divided clock without using the SYNC pin. A 0 to 1 transition on this bit causes the phase of division in the TX Divider to be incremented by 1 with respect to the current phase of division. To increment the phase of division more than once, clear and then set this bit once again. Global syncing as well as Syncing for the Tx Divider needs to be disabledforthismodetowork. Tx_INV_SINC_FIL_EN – Enables the Tx Inverse Sinc Filter. Set Tx_INV_SINC_FIL_EN_SRC for this to takeeffect. Tx_INV_SINC_FIL_EN_SRC–Whenset,thisallowsTx_INV_SINC_FIL_ENtotakeeffect. RegisterName–CONFIG6–Address0x10B,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> TX_CMIX_SYNC_ TX_GLOBAL_ TX_QMC_GAIN_PH_ TX_QMC_OFF_ TX_DIV_ TX_CMIX_ TX_FIFO_ SRC SYNC_DIS SYNC_DIS SYNC_DIS SYNC_DIS SYNC_DIS SYNC_DIS TX_FIFO_SYNC_DIS – Disables Syncing of the FIFO. This takes effect only when TX_GLOBAL_SYNC_DIS is set. This is only a enable/ disable bit – the actual sync source can be set to pin or serial interface. When the FIFO is synced, the read and write pointers are initialized such that they areseparatedby4positions.Thismodeiscommonforbothchannels. TX_CMIX_SYNC_DIS – Disables Syncing of the Tx CMIX .This takes effect only when TX_GLOBAL_SYNC_DIS is set. CMIX syncing refers to setting the phase of the complex mixing. This modeiscommonforbothchannels. TX_DIV_SYNC_DIS – Disables Syncing of the Tx Divider phase .This takes effect only when TX_GLOBAL_SYNC_DISisset.Commonforbothchannels. TX_QMC_OFF_SYNC_DIS – Disables Syncing of Tx QMC Offset Correction .This takes effect only when TX_GLOBAL_SYNC_DISisset.Thismodeiscommonforbothchannels. TX_QMC_GAIN_PH_SYNC_DIS – Disables Syncing of Tx QMC Gain Phase Correction .This takes effect onlywhenTX_GLOBAL_SYNC_DISisset.Thismodeiscommonforbothchannels. TX_GLOBAL_SYNC_DIS – When set, disables global syncing of TX and enables block level syncing. Whencleared,arisingedgeontheselectedsyncsourcecausesallTXblockstobesynced. Copyright©2011,TexasInstrumentsIncorporated REGISTERDESCRIPTIONS 23 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com TX_CMIX_SYNC_SRC – Specifies the sync source for TX CMIX. When cleared, SYNC pin is used as the sync source. When set, a rising edge on serial interface bit TX_CMIX_SER_IF_SYNC in Register 0x10D is used as the sync source for TX CMIX. This is applicable when TX_GLOBAL_SYNC_DIS is set and TX_CMIX_SYNC_DISiscleared. VALUE SYNCSOURCE 0 Pin 1 Serialinterfacebit RegisterName–CONFIG7–Address0x10C,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> TX_GLOBAL_ TX_QMC_GAIN_PH_ TX_QMC_OFF_SYNC_ TX_DIV_SYNC_ TX_FIFO_SYNC_ SYNC_SRC SYNC_SRC SRC SRC SRC TX_FIFO_SYNC_SRC – Specifies the Sync source for TX FIFO. It is applicable when TX_GLOBAL_SYNC_DISissetandTX_FIFO_SYNC_DISiscleared. VALUE SYNCSOURCE 0 Pin 1 Serialinterfacebit When the value programmed is 1, a rising edge on the serial interface bit TX_FIFO_SER_IF_SYNC in register0x10DisusedasthesyncsourcefortheFIFO. TX_DIV_SYNC_SRC – Specifies the sync source for TX Divider. When cleared, SYNC pin is used as the sync source. When set, a rising edge on serial interface bit TX_DIV_SER_IF_SYNC in register 0x10D is used as the sync source for TX Divider. This is applicable when TX_GLOBAL_SYNC_DIS is set and TX_DIV_SYNC_DISiscleared. TX_QMC_OFF_SYNC_SRC – Specifies the sync source for TX QMC Offset Correction. When cleared, SYNC pin is used as the sync source. When set, a rising edge on serial interface bit TX_QMC_OFF_SER_IF_SYNC in register 0x10D is used as the sync source for TX QMC Offset Correction. This is applicable when TX_GLOBAL_SYNC_DIS is set and TX_QMC_OFF_SYNC_DIS is cleared. TX_QMC_GAIN_PH_SYNC_SRC – Specifies the sync source for TX QMC Gain Phase Correction. When cleared, SYNC pin is used as the sync source. When set, a rising edge on serial interface bit TX_QMC_GAIN_PH_SER_IF_SYNC in register 0x10D is used as the sync source for TX QMC Gain Phase Correction. This is applicable when TX_GLOBAL_SYNC_DIS is set and TX_QMC_GAIN_PH_SYNC_DISiscleared. TX_GLOBAL_SYNC_SRC – Specifies the sync source for TX. This is applicable when TX_GLOBAL_SYNC_DISiscleared. VALUE SYNCSOURCE 0 AllblockssyncedfromtheSYNCpin 1 AllblockssyncedusingserialInterfacebit When serial interface is specified to be the sync source, a rising edge on the serial interface bit TX_GLOB_SER_IF_SYNCinregister0x10Disusedasthesyncsource. 24 REGISTERDESCRIPTIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 RegisterName–CONFIG8–Address0x10D,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> TX_GLOBAL_SER_ TX_QMC_GAIN_PH_ TX_QMC_OFF_ TX_DIV_SER_ TX_CMIX_SER_ TX_FIFO_SER_ IF_SYNC SER_IF_SYNC SER_IF_SYNC IF_SYNC IF_SYNC IF_SYNC TX_FIFO_SER_IF_SYNC – A rising edge on this bit is used as the sync source for TX FIFO. This is applicable when TX_GLOBAL_SYNC_DIS is set, and TX_FIFO_SYNC_DIS is cleared, and TX_FIFO_SYNC_SRCspecifiesserialinterfacebittobethesyncsourcefortheFIFO. TX_CMIX_SER_IF_SYNC – A rising edge on this bit is used as the sync source for TX CMIX. This is applicable when TX_GLOBAL_SYNC_DIS is set, and TX_CMIX_SYNC_DIS is cleared, and TX_CMIX_SYNC_SRCspecifiesserialinterfacebittobethesyncsourcefortheTXCMIX. TX_DIV_SER_IF_SYNC – A rising edge on this bit is used as the sync source for TX Divider. This is applicable when TX_GLOBAL_SYNC_DIS is set, and TX_DIV_SYNC_DIS is cleared, and TX_DIV_SYNC_SRCspecifiesserialinterfacebittobethesyncsourcefortheTXDivider. TX_QMC_OFF_SER_IF_SYNC – A rising edge on this bit is used as the sync source for TX QMC Offset correctionblock.ThisisapplicablewhenTX_GLOBAL_SYNC_DISisset,andTX_QMC_OFF_SYNC_DIS is cleared, and TX_QMC_OFF_SYNC_SRC specifies serial interface bit to be the sync source for the TX QMCOffsetcorrection. TX_QMC_GAIN_PH_SER_IF_SYNC – A rising edge on this bit is used as the sync source for TX QMC Gain Phase correction block. This is applicable when TX_GLOBAL_SYNC_DIS is set, and TX_QMC_GAIN_PH_SYNC_DIS is cleared, and TX_QMC_GAIN_PH_SYNC_SRC specifies serial interfacebittobethesyncsourcefortheTXQMCGainPhasecorrection. TX_GLOBAL_SER_IF_SYNC– ArisingedgeonthisisusedasthesyncsourceforTX.Thisisapplicable when TX_GLOBAL_SYNC_DIS is cleared, and TX_GLOBAL_SYNC_SRC(1:0) specifies serial interface bittobethesyncsourceforTX. RegisterName–CONFIG9–Address0x10E,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> TX_QMC_CORR_ TX_QMC_OFFSET_ TX_QMC_GAIN_PH_ TX_QMC_OFF_ ENA ENA SYNC_NEEDED SYNC_NEEDED TX_QMC_OFF_SYNC_NEEDED – Specifies if syncing is needed for TX QMC Offset Correction . If set, QMC Offset values programmed in the serial interface registers are not applied to the QMC Offset correctionblockuntilasyncisapplied. TX_QMC_GAIN_PH_SYNC_NEEDED – Specifies if syncing is needed for TX QMC Gain Phase Correction. If set, QMC gain and Phase values programmed into the serial interface registers are not appliedtotheQMCGainPhasecorrectionblockuntilasyncisapplied. TX_QMC_OFFSET_ENA– EnablesTXQMCOffsetCorrection.Commonforbothchannels. TX_QMC_CORR_ENA – Enable TX QMC Gain Phase Correction. Common for both channels. Note that by default, the TX_QMC_GAINA(2:0) and TX_QMC_GAINB(2:0) are set to 0. So when TX_QMC_CORR_ENA is written, the output goes to zero until the time TX_QMC_GAINA(2:0) and TX_QMC_GAINB(2:0)arewrittentothedesiredvalue. RegisterName–CONFIG10–Address0x10FDefault=0x00(OptionallySynced) <7> <6> <5> <4> <3> <2> <1> <0> TX_QMC_OFFSETA(12:5) TX_QMC_OFFSETA(12:5) – Upper 8 bits of DAC A Offset Correction . The lower 5 bits are in CONFIG11 Register.Offsetisasignedvalue(2scomplement). Copyright©2011,TexasInstrumentsIncorporated REGISTERDESCRIPTIONS 25 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com RegisterName–CONFIG11–Address0x110Default=0x00(OptionallySynced) <7> <6> <5> <4> <3> <2> <1> <0> TX_QMC_OFFSETA(4:0) TX_QMC_GAINA(2:0) TX_QMC_OFFSETA(4:0)–Lower5bitsofDACAOffsetCorrection. TX_QMC_GAINA(2:0) – Lower 3 bits of the 11 bit QMC Gain word for DAC A. The upper 8 bits are in CONFIG12 register.The full 11 bit TX_QMC_GAINA(10:0) word is formatted as UNSIGNED with a range or0to1.9990.Theimplieddecimalpointforthemultiplicationisbetweenbits(9)and(10). RegisterName–CONFIG12–Address0x111Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> TX_QMC_GAINA(10:3) TX_QMC_GAINA(10:3)–Upper8bitsifthe11bitQMCGainwordforDACA. RegisterName–CONFIG13–Address0x112Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> TX_QMC_OFFSETB(12:5) TX_QMC_OFFSETB(12:5) –Upper 8 bits of DAC B Offset Correction. The lower 5 bits are in CONFIG14 Register. RegisterName–CONFIG14–Address0x113Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> TX_QMC_OFFSETB(4:0) TX_QMC_GAINB(2:0) TX_QMC_OFFSETB(4:0)–Lower5bitsofDACBOffsetCorrection. TX_QMC_GAINB(2:0) – Lower 3 bits of the 11 bit QMC Gain word for DAC B. The upper 8 bits are in CONFIG15 register.The full 11 bit TX_QMC_GAINB(10:0) word is formatted as UNSIGNED with a range or0to1.9990. RegisterName–CONFIG15–Address0x114Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> TX_QMC_GAINB(10:3) TX_QMC_GAINB(10:3)–Upper8bitsifthe11bitQMCGainwordforDACB. RegisterName–CONFIG16–Address0x115Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> TX_QMC_PHASE(9:2) TX_QMC_PHASE(9:2) – Upper Upper 8 bits if the 10 bit QMC Phase word. The lower two bits are in the CONFIG17 register. The full QMC_PHASE(9:0) correction word is formatted as 2s complement and scaled to occupy a range of -0.125 to 0.12475. To acomplish QMC Phase correction, this value is multipliedbythecurrentQsample,thensummedtotheIsample. RegisterName–CONFIG17–Address0x116Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> TX_QMC_PHASE(1:0) TX_QMC_PHASE(1:0)– Lower2bitsofthe10bitQMCPhaseword. 26 REGISTERDESCRIPTIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 RegisterName–CONFIG18–Address0x117Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> TX_NCO_FREQ_WORD(31:24) TX_NCO_FREQ_WORD(31:24)– SeeCONFIG21below. RegisterName–CONFIG19–Address0x118Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> TX_NCO_FREQ_WORD(23:16) TX_NCO_FREQ_WORD(23:16)– SeeCONFIG21below. RegisterName–CONFIG20–Address0x119Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> TX_NCO_FREQ_WORD(15:8) TX_NCO_FREQ_WORD(15:8)– SeeCONFIG21below. RegisterName–CONFIG21–Address0x11ADefault=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> TX_NCO_FREQ_WORD(7:0) TX_NCO_FREQ_WORD(7:0) – This is used to determine the frequency, F of the NCO. The twos mix complementformattedvaluecanbepositiveornegative,andtheLSBisequaltoFs/232 RegisterName–CONFIG22–Address0x11BDefault=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> TX_NCO_PHASE_OFF(15:8) TX_NCO_FREQ_WORD(15:8)– SeeCONFIG23below. RegisterName–CONFIG23–Address0x11CDefault=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> TX_NCO_PHASE_OFF(7:0) TX_NCO_PHASE_OFF(7:0) – This is the 2s complement Phase offset added to the NCO accumulator justbeforethegenerationoftheSINandCOSvalues. RegisterName–CONFIG24–Address0x11D,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> TX_MIXER_EN TX_MIXER_GAIN(1:0) TX_MIXER_GAIN(1:0) – The fine mixer realizes the functions {Acos(ω t) – B sin(ω t)} and {Asin(ω t) mix mix mix + Bcos(ω )} This can cause the fine mixer output to be up to 3 dB higher than the individual inputs.The mixt mixergaincanrestorethesignalleveltothedesiredlevelbyprovidingaprogrammableattenuation. VALUE GAIN 0 –2.5dB(default)–usewhencomplexmixing 1 –6dB 2 0dB–usewhenoneinputiszero 3 0dB TX_MIXER_EN– Thisenablesthefinemixer,whichalsocausestheNCOtobeenabled. Copyright©2011,TexasInstrumentsIncorporated REGISTERDESCRIPTIONS 27 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com RegisterName–CONFIG25–Address0x11EDefault=0x00 <7> <6> <5> <4> <3> <2> <1> <0> TX_NCO_SYNC_ TX_NCO_SYNC_ TX_NCO_SER_IF_ TX_NCO_SYNC_ DIS SRC SYNC NEEDED TX_NCO_SYNC_NEEDED – Specifies if syncing is needed for TX NCO. If set, NCO Frequency and Offset words programmed into the serial interface registers are not applied to the NCO until a sync is applied TX_NCO_SER_IF_SYNC – A rising edge on this bit is used as the sync source for TX NCO. This is applicable when TX_GLOBAL_SYNC_DIS is set, and TX_NCO_SYNC_DIS is cleared, and TX_NCO_SYNC_SRCspecifiesserialinterfacebittobethesyncsourcefortheNCO. TX_NCO_SYNC_SRC – Specifies the sync source for TX NCO. When cleared, SYNC pin is used as the sync source. When set, a rising edge on serial interface bit TX_NCO_SER_IF_SYNC is used as the sync sourceforTXNCO.ThisisapplicablewhenTX_GLOBAL_SYNC_DISisset. TX_NCO_SYNC_DIS – Disables Syncing of the Tx NCO. This takes effect only when TX_GLOBAL_SYNC_DISisset. RegisterName–CONFIG26–Address0x11F,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG1(15:8) CHA_REG1(15:8) – Upper 8 bits for sample 1 for DAC A in 8-sample FIFO mode . TX_CHA_8_IP_EN in CONFIG1needstobesetforRegsCONFIG26toCONFIG41totakeeffect. RegisterName–CONFIG27–Address0x120,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG1(7:0) CHA_REG1(7:0)– Lower8bitsforsample1forDACA RegisterName–CONFIG28–Address0x121,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG2(15:8) CHA_REG2(15:8)–Upper8bitsforsample2forDACA . RegisterName–CONFIG29–Address0x122,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG2(7:0) CHA_REG2(7:0)– Lower8bitsforsample2forDACA RegisterName–CONFIG30–Address0x123,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG3(15:8) CHA_REG3(15:8)–Upper8bitsforsample3forDACA RegisterName–CONFIG31–Address0x124,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG3(7:0) CHA_REG3(7:0)– Lower8bitsforsample3forDACA 28 REGISTERDESCRIPTIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 RegisterName–CONFIG32–Address0x125,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG4(15:8) CHA_REG4(15:8)–Upper8bitsforsample4forDACA . RegisterName–CONFIG33–Address0x126,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG4(7:0) CHA_REG4(7:0)– Lower8bitsforsample4forDACA RegisterName–CONFIG34–Address0x127,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG5(15:8) CHA_REG5(15:8)–Upper8bitsforsample5forDACA RegisterName–CONFIG35–Address0x128,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG5(7:0) CHA_REG5(7:0)– Lower8bitsforsample5forDACA . RegisterName–CONFIG36–Address0x129,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG6(15:8) CHA_REG6(15:8)–Upper8bitsforsample6forDACA RegisterName–CONFIG37–Address0x12A,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG6(7:0) CHA_REG6(7:0)– Lower8bitsforsample6forDACA RegisterName–CONFIG38–Address0x12B,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG7(15:8) CHA_REG7(15:8)–Upper8bitsforsample7forDACA RegisterName–CONFIG39–Address0x12C,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG7(7:0) CHA_REG7(7:0)– Lower8bitsforsample7forDACA. RegisterName–CONFIG40–Address0x12D,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG8(15:8) CHA_REG8(15:8)–Upper8bitsforsample8forDACA Copyright©2011,TexasInstrumentsIncorporated REGISTERDESCRIPTIONS 29 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com RegisterName–CONFIG41–Address0x12E,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHA_REG8(7:0) CHA_REG8(7:0)– Lower8bitsforsample8forDACA RegisterName–CONFIG42–Address0x12F,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG1(15:8) CHB_REG1(15:8) – Upper 8 bits for sample 1 for DAC B . TX_CHB_8_IP_EN in CONFIG 1 needs to be setforRegsCONFIG42toCONFIG57totakeeffect. RegisterName–CONFIG43–Address0x130,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG1(7:0) CHB_REG1(7:0)– Lower8bitsforsample1forDACB RegisterName–CONFIG44–Address0x131,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG2(15:8) CHB_REG2(15:8)–Upper8bitsforsample2forDACB. RegisterName–CONFIG45–Address0x132,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG2(7:0) CHB_REG2(7:0)– Lower8bitsforsample2forDACB RegisterName–CONFIG46–Address0x133,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG3(15:8) CHB_REG3(15:8)–Upper8bitsforsample3forDACB. RegisterName–CONFIG47–Address0x134,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG3(7:0) CHB_REG3(7:0)– Lower8bitsforsample3forDACB RegisterName–CONFIG48–Address0x135,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG4(15:8) CHB_REG4(15:8)–Upper8bitsforsample4forDACB. RegisterName–CONFIG49–Address0x136,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG4(7:0) CHB_REG4(7:0)– Lower8bitsforsample4forDACB. 30 REGISTERDESCRIPTIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 RegisterName–CONFIG50–Address0x137,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG5(15:8) CHB_REG5(15:8)–Upper8bitsforsample5forDACB. RegisterName–CONFIG51–Address0x138,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG5(7:0) CHB_REG5(7:0)– Lower8bitsforsample5forDACB RegisterName–CONFIG52–Address0x139,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG6(15:8) CHB_REG6(15:8)–Upper8bitsforsample6forDACB. RegisterName–CONFIG53–Address0x13A,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG6(7:0) CHB_REG6(7:0)– Lower8bitsforsample6forDACB. RegisterName–CONFIG54–Address0x13B,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG7(15:8) CHB_REG7(15:8)–Upper8bitsforsample7forDACB. RegisterName–CONFIG55–Address0x113C,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG7(7:0) CHB_REG7(7:0)– Lower8bitsforsample7forDACB RegisterName–CONFIG56–Address0x13D,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG8(15:8) CHB_REG8(15:8)–Upper8bitsforsample8forDACB. RegisterName–CONFIG57–Address0x13E,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> CHB_REG8(7:0) CHB_REG8(7:0)– Lower8bitsforsample8forDACB RegisterName–CONFIG58–Address0x13F,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> EN_IP_CLK_STOP_DET EN_FIFO_COLLISION_DET EN_FIFO_COLLISION_DET–OnRESET(andwhensynced),thereadandwritepointersoftheFIFOare set 4 positions away. The read pointer increments at the DAC_DCLKIN rate whereas the write pointer increments at the divided DAC_CLK rate. While the frequencies of these 2 clocks are expected to be the same, relative phase drifts can cause this relative difference of 4 positions to drift. When the EN_FIFO_COLLISION_DET bit is set, a collision condition is detected when the relative difference Copyright©2011,TexasInstrumentsIncorporated REGISTERDESCRIPTIONS 31 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com between the read and write pointers becomes either 0,1 or 2. Detection of this collision condition automatically causes masks the DACs to give out an output corresponding to mid code. The read and write pointer differing by 2 is referred to as 2-way detection. 2-away detection can be prevented from triggering collision by setting MASK_2_AWAY_DET in CONFIG 1. Collision detection is done once every 8inputsamples. EN_IP_CLK_STOP_DET – When set, the condition of input clock being stopped causes the DAC outputs tobeforcedtomidcode. RegisterName–CONFIG59–Address0x140,Default=0x00(ReadOnly) <7> <6> <5> <4> <3> <2> <1> <0> FIFO_ERROR FIFO_COLLISION FIFO_1_AWAY FIFO_2_AWAY INP_CLK_STOP ThesearerefreshedattherateofthedividedDAC_CLK. INP_CLK_STOP– Ifset,itindicatesthattheinputclockhasbeendetectedashavingbeenstopped. FIFO_2_AWAY – If set, it indicates that the condition of the read and write pointers being 2 locations awayfromeachotherhasbeendetected. FIFO_1_AWAY – If set, it indicates that the condition of the read and write pointers being 1 location away fromeachotherhasbeendetected. FIFO_COLLISION – If set, this indicates that the read and write pointers have been detected as overlappingwitheachother FIFO_ERROR – If set, this indicates that either Collision , or 1-away or 2-away condition has been detected. RegisterName–CONFIG60–Address0x141,Default=0x00(ReadOnly) <7> <6> <5> <4> <3> <2> <1> <0> FIFO_INP_PTR(2:0) FIFO_OP_PTR(2:0) FIFO_OP_PTR(2:0) – Containts the FIFO read pointer value. Its written into the register when STORE_FIFO_PTRS is set in CONFIG2. It is not updated once the device is configured into readout mode. FIFO_INP_PTR(2:0) – Containts the FIFO write pointer value. Its written into the register when STORE_FIFO_PTRS is set in CONFIG2. It is not updated once the device is configured into readout mode. 5.2 RECEIVE DIGITAL SIGNAL CHAIN REGISTERS RX InputA Offset Gain/ase eMixerMIX) Mixer HBFmation R(I XC hOauntpnuelt)A RX Input B QMC QMCPh Coars(C Fine /2Deci R(QX COhuatnpnuet lB) SYNC SYNC SYNC RX RMS/ Peak NCO Power Meter SYNC SYNC Figure5-3.SignalChain 32 REGISTERDESCRIPTIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 RegisterName–CONFIG61–Address0x165,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> TX_RX_LPBK_ TX_RX_LPBK RX_DECB_MODE RX_DECA_MODE RX_DEC_FIL_ RX_DEC_FIL_ SRC EN_SRC EN RX_DEC_FIL_EN – Enables the decimation filter in the RX path in both the A and B channels. Set RX_DEC_FIL_EN_SRCforthistotakeeffect.Outputclockautomaticallysetto0.5X. RX_DEC_FIL_EN_SRC– Whenset,thisallowsRX_DEC_FIL_ENtotakeeffect. RX_DECA_MODE – When set, configures the decimation filter in Channel A in high pass mode. By default,thefilterisinlowpassmode. RX_DECB_MODE – When set, configures the decimation filter in Channel B in high pass mode. By default,thefilterisinlowpassmode. TX_RX_LPBK – When this bit and TX_Rx_LPBK_SRC are both set , the input to the RX signal chain is tappedfromthethefinaloutputoftheTXsignalchain. TX_Rx_LPBK_SRC – When this bit and TX_RX_LPBK are both set , the input to the RX signal chain is tappedfromthethefinaloutputoftheTXsignalchain. TheTXtoRXloopbackisillustratedbelow.Thedottedarrowsshowtheloopbackmode. INP_A_ADC 12b X LAIN orOS INN_A_ADC RXADCA MU GITACH VDSCM 12-bitADC IINNPN__BB__AADDCC RX1A2DbC B UX RXDIGNAL erialLarallel Output M SI SP IOUTP_A_DAC 12b LAIN orOS IOUTN_A_DAC TX DACA GITACH VDSCM 12-bit DAC IIOOUUTTNP__BB__DDAACC TX 1D2AbC B TXDISIGNAL SerialLParallel Input Figure5-4.SignalChain RegisterName–CONFIG62–Address0x166,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> RX_DIV_PHASE_INV RX_DIV_PHASE RX_CMIX_PHASE(1:0) RX_CMIX_PHASE_ RX_CMIX_MODE(1:0) RX_CMIX_EN INCR RX_CMIX_EN–EnablestheRXCoarsemixer. RX_CMIX_MODE(1:0) – Specifies the mode in which the RX Coarse mixer is configured . Set RX_CMIX_ENforthistotakeeffect. VALUE MIXINGMODE 0 Normal(Lowpass) 1 Fs/2(HighPass) 2 +Fs/4 3 –Fs/4 Copyright©2011,TexasInstrumentsIncorporated REGISTERDESCRIPTIONS 33 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com RX_CMIX_PHASE_INCR – This bit can be used to control the mixing phase without the need for the SYNC pin. A 0 to 1 transition on this bit causes the phase of mixing in the RX CMIX to be incremented by 1 with respect to the current phase of mixing . To increment the phase of mixing more than once, clear and then set this bit once again. Syncing needs to be disabled for RX CMIX for this mode to work. (This meansthatbothglobalsyncing,aswellasblocklevelsyncingneedstobedisabledforCMIX) RX_CMIX_PHASE(1:0) – The value programmed into this is applied as the RX CMIX phase, when the CMIXissynced,SyncingneedstobeenabledforCMIXforthismodetowork. RX_DIV_PHASE – The value programmed into this is applied as the RX Divider phase, when the divider is synced. If divider is not synced, then output latency can differ by 1 with respect to the sampling clock. TheRXdividerisusedwheneverthedecimationfilterisenabled. RX_DIV_PHASE_INV – This bit is used to control the phase of the RX divider without the need for the SYNC pin. A 0 to 1 transition on this bit causes the phase of division in the RX Divider to be inverted by 1 with respect to the current phase of division. To invert the phase of division more than once, clear and thensetthisbitonceagain.SyncingneedstobedisabledforRXDividerforthismodetowork. RegisterName–CONFIG63–Address0x167,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> RX_BYP_SRC RX_BYP RX_CHB_PDN_SRC RX_CHB_PDN RX_CHA_PDN RX_CHA_PDN_S RX_DIS RC RX_DIS–DisablestheRXsignalchainofbothchannels.Allblocksinthesignalchainarepowereddown, andtheRXoutputismid-code. RX_CHA_PDN_SRC– SettingthiscausesthevalueprogrammedintoRX_CHA_PDNtotakeeffect. RX_CHA_PDN – Powers down Channel A in Rx signal chain. Output of the channel is mid code. Set RX_CHA_PDN_SRCforthistotakeeffect.Outputclockisnotpowereddown. RX_CHB_PDN – Powers down Channel B in Rx signal chain. Output of the channel is mid code. Set RX_CHB_PDN_SRCforthistotakeeffect.Outputclockisnotpowereddown. RX_CHB_PDN_SRC– SettingthiscausesthevalueprogrammedintoRX_CHB_PDNtotakeeffect. Note that when in default mode of operation (none of the register-selectable digital features enabled), all 4 of above bits (RX_CHA_PDN, RX_CHA_PDN_SRC, RX_CHB_PDN, RX_CHB_PDN_SRC) have to be set together to ‘1’ for them to take effect. However, if any of the digital features (like interpolation, Fine mixer, Coarse mixer, or QMC gain/phase or offset) are enabled, then the channel A can be independently powered down using bits RX_CHA_PDN and RX_CHA_PDN_SRC, and channel B can be independently powereddownusingbitsRX_CHB_PDNandRX_CHB_PDN_SRC. RX_BYP – The inputs to both the Rx channels are directly passed to the outputs. Set RX_BYP_SRC for thistotakeeffect.UsethismodetooperatetheRxwithlowestlatency. RX_BYP_SRC– SettingthiscausesthevalueprogrammedintoRX_BYPtotakeeffect. RegisterName–CONFIG64–Address0x168,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> RX_GLOBAL_SYNC_ RX_QMC_GAIN_PH_SYNC_ RX_QMC_OFF_SYNC_ RX_DIV_SYNC_ RX_CMIX_SYNC_ DIS DIS DIS DIS DIS RX_CMIX_SYNC_DIS – Disables Syncing of the Rx Coarse mixer. This takes effect only when RX_GLOBAL_SYNC_DISisset. RX_DIV_SYNC_DIS – Disables Syncing of the Rx clock divider .This takes effect only when RX_GLOBAL_SYNC_DISisset. RX_QMC_OFF_SYNC_DIS – Disables Syncing of Rx QMC Offset Correction .This takes effect only when RX_GLOBAL_SYNC_DISisset. 34 REGISTERDESCRIPTIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 www.ti.com SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 RX_QMC_GAIN_PH_SYNC_DIS– DisablesSyncingofRxQMCGainPhaseCorrection. ThistakeseffectonlywhenRX_GLOBAL_SYNC_DISisset. RX_GLOBAL_SYNC_DIS – When set, disables global syncing of RX signal chain. When cleared, a rising edgeontheselectedsyncsourcecausesRXblockstobesynced. RegisterName–CONFIG65–Address0x169,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> RX_GLOBAL_SYNC_ RX_QMC_GAIN_PH_SYNC_ RX_QMC_OFF_SYNC_ RX_DIV_SYNC_ RX_CMIX_SYNC_ SRC SRC SRC SRC SRC RX_CMIX_SYNC_SRC – Specifies the sync source for the RX Coarse mixer. When cleared, SYNC pin is used as the sync source . When set, a rising edge on serial interface bit RX_CMIX_SER_IF_SYNC in Register 0x16A is used as the sync source for RX CMIX. This is applicable when RX_GLOBAL_SYNC_DISisset,andRX_CMIX_SYNC_DISiscleared. RX_DIV_SYNC_SRC – Specifies the sync source for the RX Divider. When cleared, SYNC pin is used as thesyncsource.Whenset,arisingedgeonserialinterfacebitRX_DIV_SER_IF_SYNCinregister0x16A is used as the sync source for RX Divider. This is applicable when RX_GLOBAL_SYNC_DIS is set and RX_DIV_SYNC_DISiscleared. RX_QMC_OFF_SYNC_SRC – Specifies the sync source for RX QMC Offset Correction. When cleared, SYNC pin is used as the sync source . When set , a rising edge on serial interface bit RX_QMC_OFF_SER_IF_SYNC in register 0x16A is used as the sync source for RX QMC Offset Correction. This is applicable when RX_GLOBAL_SYNC_DIS is set and RX_QMC_OFF_SYNC_DIS is cleared. RX_QMC_GAIN_PH_SYNC_SRC – Specifies the sync source for RX QMC Gain Phase Correction. When cleared, SYNC pin is used as the sync source. When set, a rising edge on serial interface bit RX_QMC_GAIN_PH_SER_IF_SYNC in register 0x16A is used as the sync source for RX QMC Gain Phase Correction. This is applicable when RX_GLOBAL_SYNC_DIS is set and RX_QMC_GAIN_PH_SYNC_DISiscleared. RX_GLOBAL_SYNC_SRC – Specifies the sync source for RX. When cleared, SYNC pin is used as the sync source. When set, a rising edge on serial interface bit RX_GLOB_SER_IF_SYNC in register 0x16A isusedasthesyncsourceforRX.ThisisapplicablewhenRX_GLOBAL_SYNC_DISiscleared. RegisterName–CONFIG66–Address0x16A,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> RX_GLOBAL_SER_ RX_QMC_GAIN_PH_ RX_QMC_OFF_SER_ RTX_DIV_SER_ RX_CMIX_SER_IF_ IF_SYNC SER_IF_SYNC IF_SYNC IF_SYNC SYNC RX_CMIX_SER_IF_SYNC – A rising edge on this bit is used as the sync source for RX CMIX. This is applicable when RX_GLOBAL_SYNC_DIS is set, and RX_CMIX_SYNC_DIS is cleared, and RX_CMIX_SYNC_SRCspecifiesserialinterfacebittobethesyncsourcefortheRXCMIX. RX_DIV_SER_IF_SYNC – A rising edge on this bit is used as the sync source for RX Divider. This is applicable when RX_GLOBAL_SYNC_DIS is set, and RX_DIV_SYNC_DIS is cleared, and RX_DIV_SYNC_SRCspecifiesserialinterfacebittobethesyncsourcefortheRXDivider. RX_QMC_OFF_SER_IF_SYNC – A rising edge on this bit is used as the sync source for RX QMC Offset correction block. This is applicable when RX_GLOBAL_SYNC_DIS is set, and RX_QMC_OFF_SYNC_DIS is cleared, and RX_QMC_OFF_SYNC_SRC specifies serial interface bit to be thesyncsourcefortheRXQMCOffsetcorrection. RX_QMC_GAIN_PH_SER_IF_SYNC – A rising edge on this bit is used as the sync source for RX QMC Gain Phase correction block. This is applicable when RX_GLOBAL_SYNC_DIS is set, and RX_QMC_GAIN_PH_SYNC_DIS is cleared, and RX_QMC_GAIN_PH_SYNC_SRC specifies serial interfacebittobethesyncsourcefortheRXQMCGainPhasecorrection. Copyright©2011,TexasInstrumentsIncorporated REGISTERDESCRIPTIONS 35 SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225

AFE7222 AFE7225 SLOS711A–NOVEMBER2011–REVISEDDECEMBER2011 www.ti.com RX_GLOBAL_SER_IF_SYNC – A rising edge on this is used as the sync source for RX . This is applicable when RX_GLOBAL_SYNC_DIS is cleared, and RX_GLOBAL_SYNC_SRC specifies serial interfacebittobethesyncsourceforRX. RegisterName–CONFIG67–Address0x16B,Default=0x00 <7> <6> <5> <4> <3> <2> <1> <0> RX_QMC_CORR_ RX_QMC_OFFSET_ RX_QMC_GAIN_PH_SYNC_ RX_QMC_OFF_SYNC_ ENA ENA NEEDED NEEDED RX_QMC_OFF_SYNC_NEEDED – Specifies if syncing is needed for RX QMC Offset Correction. If set, QMC Offset values programmed into the serial interface registers are not applied to the QMC Offset correctionblockuntilaSyncisapplied. RX_QMC_GAIN_PH_SYNC_NEEDED – Specifies if syncing is needed for RX QMC Gain Phase Correction. If set, QMC gain and Phase values programmed into the serial interface registers are not appliedtotheQMCGainPhasecorrectionblockuntilasyncisapplied. RX_QMC_OFFSET_ENA– EnablesRXQMCOffsetCorrection. RX_QMC_CORR_ENA– EnableRXQMCGainPhaseCorrection. RegisterName–CONFIG68–Address0x16C,Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> RX_QMC_OFFSETA(12:5) RX_QMC_OFFSETA(12:5)– Upper8bitsofADCAOffsetCorrection.Thelower5bitsareinCONFIG69 Register. RegisterName–CONFIG69–Address0x16D,Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> RX_QMC_OFFSETA(4:0) RX_QMC_GAINA(2:0) RX_QMC_OFFSETA(4:0)–Lower5bitsofADCAOffsetCorrection. RX_QMC_GAINA(2:0) – Lower 3 bits of the 11 bit QMC Gain word for ADC A. The upper 8 bits are in CONFIG70 register.The full 11 bit RX_QMC_GAINA(10:0) word is formatted as UNSIGNED with a range or0to1.9990.Theimplieddecimalpointforthemultiplicationisbetweenbits(9)and(10). RegisterName–CONFIG70–Address0x16E,Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> RX_QMC_GAINA(10:3) RX_QMC_GAINA(10:3)–Upper8bitsifthe11bitQMCGainwordforADCA RegisterName–CONFIG71–Address0x16F,Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> RX_QMC_OFFSETB(12:5) RX_QMC_OFFSETB(12:5)– Upper8bitsofADCBOffsetCorrection.Thelower5bitsareinCONFIG72 Register. RegisterName–CONFIG72–Address0x170,Default=0x00(Synced) <7> <6> <5> <4> <3> <2> <1> <0> RX_QMC_OFFSETB(4:0) RX_QMC_GAINB(2:0) RX_QMC_OFFSETB(4:0)–Lower5bitsofADCBOffsetCorrection. RX_QMC_GAINB(2:0) – Lower 3 bits of the 11 bit QMC Gain word for ADC B. The upper 8 bits are in CONFIG73 register.The full 11 bit RX_QMC_GAINB(10:0) word is formatted as UNSIGNED with a range or0to1.9990. 36 REGISTERDESCRIPTIONS Copyright©2011,TexasInstrumentsIncorporated SubmitDocumentationFeedback ProductFolderLink(s):AFE7222AFE7225