ICGOO在线商城 > 集成电路(IC) > 接口 - 模拟开关,多路复用器,多路分解器 > ADG1209YCPZ-REEL7

- 型号: ADG1209YCPZ-REEL7

- 制造商: Analog

- 库位|库存: xxxx|xxxx

- 要求:

| 数量阶梯 | 香港交货 | 国内含税 |

| +xxxx | $xxxx | ¥xxxx |

查看当月历史价格

查看今年历史价格

ADG1209YCPZ-REEL7产品简介:

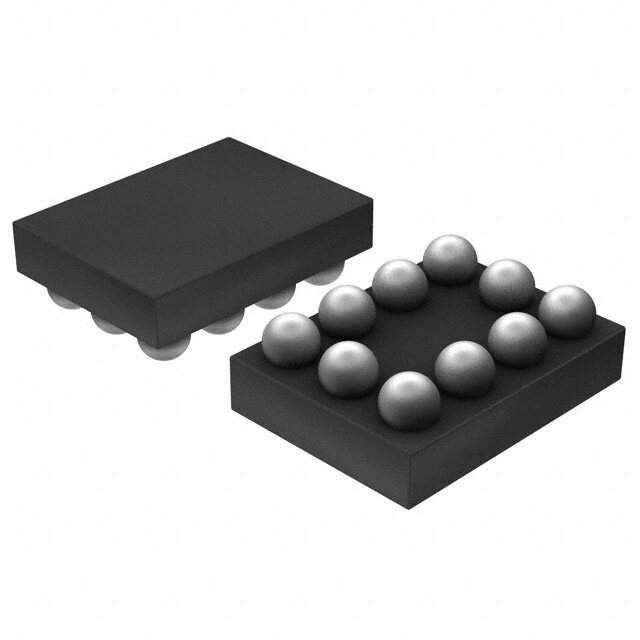

ICGOO电子元器件商城为您提供ADG1209YCPZ-REEL7由Analog设计生产,在icgoo商城现货销售,并且可以通过原厂、代理商等渠道进行代购。 ADG1209YCPZ-REEL7价格参考。AnalogADG1209YCPZ-REEL7封装/规格:接口 - 模拟开关,多路复用器,多路分解器, 2 Circuit IC Switch 4:1 200 Ohm 16-LFCSP-VQ (4x4)。您可以下载ADG1209YCPZ-REEL7参考资料、Datasheet数据手册功能说明书,资料中有ADG1209YCPZ-REEL7 详细功能的应用电路图电压和使用方法及教程。

ADG1209YCPZ-REEL7 是由 Analog Devices Inc. 生产的一款接口类模拟开关、多路复用器和多路分解器。以下是其主要应用场景: 1. 信号切换与路由 - ADG1209 是一款低电容的 SPDT(单刀双掷)模拟开关,适用于需要在多个信号源之间进行快速切换的应用场景,例如音频信号切换、视频信号路由或传感器信号选择。 - 在通信系统中,可用于射频信号或低频信号的路径切换。 2. 数据采集系统 - 在多通道数据采集系统中,ADG1209 可用于将多个输入信号依次连接到 ADC(模数转换器),实现高效的数据采集。 - 其低导通电阻和低泄漏电流特性使其适合高精度测量应用。 3. 医疗设备 - 在医疗设备中,如心电图仪(ECG)、超声波设备或多参数监护仪中,ADG1209 可用于选择不同的传感器输入信号,确保信号的准确性和稳定性。 - 其低电荷注入特性减少了信号切换时的干扰,适合对噪声敏感的医疗应用。 4. 工业自动化 - 在工业控制系统中,ADG1209 可用于多路传感器信号的切换,例如温度、压力或流量传感器的信号选择。 - 其宽工作电压范围(-16V 至 +16V 或 -5.5V 至 +5.5V 单电源)使其能够适应各种工业环境。 5. 通信与网络设备 - 在通信设备中,ADG1209 可用于信号路径的选择和切换,支持高频信号传输。 - 其低电容特性(典型值为 2.2pF)使其适合高速信号切换应用。 6. 消费电子 - 在音频设备中,ADG1209 可用于音频输入/输出的切换,例如耳机插孔检测或麦克风输入选择。 - 在便携式设备中,其低功耗特性有助于延长电池寿命。 7. 测试与测量设备 - 在示波器、信号发生器或多路测试仪中,ADG1209 可用于信号路径的控制和优化。 - 其高线性度和低失真特性确保了测试结果的准确性。 总之,ADG1209YCPZ-REEL7 的高性能和灵活性使其广泛应用于需要精确信号切换和多路复用的场合,尤其是在对带宽、精度和低功耗有较高要求的领域。

| 参数 | 数值 |

| 产品目录 | 集成电路 (IC) |

| 描述 | IC MULTIPLEXER DUAL 4X1 16LFCSP |

| 产品分类 | |

| 品牌 | Analog Devices Inc |

| 数据手册 | |

| 产品图片 |

|

| 产品型号 | ADG1209YCPZ-REEL7 |

| PCN组件/产地 | |

| rohs | 无铅 / 符合限制有害物质指令(RoHS)规范要求 |

| 产品系列 | iCMOS® |

| 产品培训模块 | http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=16843http://www.digikey.cn/PTM/IndividualPTM.page?site=cn&lang=zhs&ptm=16845 |

| 产品目录页面 | |

| 供应商器件封装 | 16-LFCSP-VQ (4x4) |

| 其它名称 | ADG1209YCPZ-REEL7-ND |

| 功能 | 多路复用器 |

| 包装 | 带卷 (TR) |

| 安装类型 | 表面贴装 |

| 导通电阻 | 475 欧姆 |

| 封装/外壳 | 16-VQFN 裸露焊盘,CSP |

| 工作温度 | -40°C ~ 125°C |

| 标准包装 | 1,500 |

| 电压-电源,单/双 (±) | 12V, ±15V |

| 电压源 | 单/双电源 |

| 电流-电源 | 220µA |

| 电路 | 2 x 4:1 |

| 设计资源 |

- 商务部:美国ITC正式对集成电路等产品启动337调查

- 曝三星4nm工艺存在良率问题 高通将骁龙8 Gen1或转产台积电

- 太阳诱电将投资9.5亿元在常州建新厂生产MLCC 预计2023年完工

- 英特尔发布欧洲新工厂建设计划 深化IDM 2.0 战略

- 台积电先进制程称霸业界 有大客户加持明年业绩稳了

- 达到5530亿美元!SIA预计今年全球半导体销售额将创下新高

- 英特尔拟将自动驾驶子公司Mobileye上市 估值或超500亿美元

- 三星加码芯片和SET,合并消费电子和移动部门,撤换高东真等 CEO

- 三星电子宣布重大人事变动 还合并消费电子和移动部门

- 海关总署:前11个月进口集成电路产品价值2.52万亿元 增长14.8%

PDF Datasheet 数据手册内容提取

Low Capacitance, 4-/8-Channel, ±15 V/+12 V iCMOS Multiplexers Data Sheet ADG1208/ADG1209 FEATURES FUNCTIONAL BLOCK DIAGRAMS <1 pC charge injection over full signal range ADG1208 ADG1209 1 pF off capacitance S1 S1A 33 V supply range DA 120 Ω on resistance S4A Fully specified at ±15 V/+12 V D 3 V logic compatible inputs Rail-to-rail operation S1B DB Break-before-make switching action S8 S4B Available in a 16-lead TSSOP, a 16-lead LFCSP, and a 16-lead SOIC 1-OF-8 1-OF-4 DECODER DECODER Typical power consumption < 0.03 µW APPLICATIONS A0A1A2EN A0 A1 EN 05713-001 Figure 1. Audio and video routing Automatic test equipment Data-acquisition systems Battery-powered systems Sample-and-hold systems Communication systems GENERAL DESCRIPTION The ADG1208 and ADG1209 are monolithic, iCMOS® analog The ultralow capacitance and exceptionally low charge injection multiplexers comprising eight single channels and four differential of these multiplexers make them ideal solutions for data acquisition channels, respectively. The ADG1208 switches one of eight inputs and sample-and-hold applications, where low glitch and fast to a common output as determined by the 3-bit binary address settling are required. Figure 2 shows that there is minimum lines A0, A1, and A2. The ADG1209 switches one of four charge injection over the entire signal range of the device. differential inputs to a common differential output as determined iCMOS construction also ensures ultralow power dissipation, by the 2-bit binary address lines A0 and A1. An EN input on making the devices ideally suited for portable and battery- both devices enable or disable the device. When disabled, all powered instruments. channels are switched off. When on, each channel conducts 1.0 MUX(SOURCETODRAIN) equally well in both directions and has an input signal range 0.9 TA=25°C that extends to the supplies. 0.8 The industrial CMOS (iCMOS) modular manufacturing C) p 0.7 process combines high voltage complementary metal-oxide N ( sdeemveilcoopnmduenctto orf (aC wMidOeS r)a anngde boifp hoilgahr tpeecrhfonromloagniecse. aItn eanloagb lIeCs st he NJECTIO 00..65 VVDSSD==–+1155VV capable of 33 V operation in a footprint that no other generation GE I 0.4 R oICf sh iugshin vgo cltoangvee dnetvioicneasl hCaMs bOeSe np raobclee stsoe sa,c ihCieMveO. SU cnolimkep oannaelnotgs CHA 0.3 VVDSSD==0+V12V 0.2 can tolerate high supply voltages while providing increased 0.1 VDD=+5V performance, dramatically lower power consumption, and VSS=–5V r educed package size. 0–15 –10 –5 VS0(V) 5 10 15 05713-051 Figure 2. Source to Drain Charge Injection vs. Source Voltage Rev. E Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Tel: 781.329.4700 ©2006–2016 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com

ADG1208/ADG1209 Data Sheet TABLE OF CONTENTS Features .............................................................................................. 1 ESD Caution...................................................................................7 Applications ....................................................................................... 1 Pin Configurations and Function Descriptions ............................8 Functional Block Diagrams ............................................................. 1 Typical Performance Characteristics ........................................... 12 General Description ......................................................................... 1 Terminology .................................................................................... 16 Revision History ............................................................................... 2 Test Circuits ..................................................................................... 17 Specifications ..................................................................................... 3 Outline Dimensions ....................................................................... 20 Dual Supply ................................................................................... 3 Ordering Guide .......................................................................... 21 Single Supply ................................................................................. 5 Absolute Maximum Ratings ............................................................ 7 REVISION HISTORY 6/2016—Rev. D to Rev. E 1/2009—Rev. A to Rev. B Changes to Analog Inputs Parameter, Table 3 .............................. 7 Change to I Parameter, Table 1 .................................................... 4 DD Added Digital Inputs Parameter, Table 3 ...................................... 7 Change to I Parameter, Table 2 .................................................... 6 DD Moved Figure 7 ............................................................................... 10 Change to Table 7 ........................................................................... 10 4/2007—Rev. 0 to Rev. A Deleted Table 8; Renumbered Sequentially ................................ 11 Added 16-lead SOIC .......................................................... Universal Updated Outline Dimensions ....................................................... 20 Changes to Table 1 ............................................................................. 3 Changes to Ordering Guide .......................................................... 21 Changes to Table 2 ............................................................................. 5 Changes to Figure 10 and Figure 11............................................. 10 3/2016—Rev. C to Rev. D Updated Outline Dimensions ....................................................... 17 Changes to Table 4 Title ................................................................... 8 Changes to Ordering Guide .......................................................... 18 Changes to Table 5 Title ................................................................... 9 Changes to Table 7 Title ................................................................. 10 4/2006—Revision 0: Initial Version Changes to Figure 7 ........................................................................ 11 Added Table 8; Renumbered Sequentially .................................. 11 Changes to Table 9 Title ................................................................. 12 8/2015—Rev. B to Rev. C Changes to Features Section............................................................ 1 Added Figure 4; Renumbered Sequentially .................................. 8 Changes to Table 4 ............................................................................ 8 Changes to Figure 5 .......................................................................... 9 Added Table 5; Renumbered Sequentially .................................... 9 Added Figure 7 ................................................................................ 10 Changes to Table 7 .......................................................................... 10 Changes to Figure 8 ........................................................................ 11 Added Table 8 .................................................................................. 11 Updated Outline Dimensions ....................................................... 19 Changes to Ordering Guide .......................................................... 20 Rev. E | Page 2 of 21

Data Sheet ADG1208/ADG1209 SPECIFICATIONS DUAL SUPPLY V = +15 V ± 10%, V = –15 V ± 10%, GND = 0 V, unless otherwise noted. Temperature range is as follows: Y version: –40°C to +125°C. DD SS Table 1. −40ºC to −40ºC to Parameter +25ºC +85ºC +125ºC Unit Test Conditions/Comments ANALOG SWITCH Analog Signal Range V to V V SS DD On Resistance, R 120 Ω typ V = ±10 V, I = −1 mA, see Figure 31 ON S S 200 240 270 Ω max V = +13.5 V, V = −13.5 V DD SS On-Resistance Match Between Channels, ∆R 3.5 Ω typ V = ±10 V, I = −1 mA ON S S 6 10 12 Ω max On-Resistance Flatness, R (On) 20 Ω typ V = −5 V/0 V/+5 V, I = −1 mA FLAT S S 64 76 83 Ω max LEAKAGE CURRENTS Source Off Leakage, I (Off) ±0.003 nA typ V = ±10 V, V = −10 V, see Figure 32 S D S ±0.1 ±0.6 ±1 nA max Drain Off Leakage, I (Off) ±0.003 nA typ V = 1 V/10 V, V = 10 V/1 V, see Figure 32 D S D ADG1208 ±0.1 ±0.6 ±1 nA max ADG1209 ±0.1 ±0.6 ±1 nA max Channel On Leakage, I , I (On) ±0.02 nA typ V = V = ±10 V, see Figure 33 D S S D ADG1208 ±0.2 ±0.6 ±1 nA max ADG1209 ±0.2 ±0.6 ±1 nA max DIGITAL INPUTS Input High Voltage, V 2.0 V min INH Input Low Voltage, V 0.8 V max INL Input Current, I or I ±0.005 µA max V = V or V INL INH IN INL INH ±0.1 µA max Digital Input Capacitance, C 2 pF typ IN DYNAMIC CHARACTERISTICS1 Transition Time, t 80 ns typ R = 300 Ω, C = 35 pF TRANSITION L L 130 165 185 ns max V = 10 V, see Figure 34 S t (EN) 75 ns typ R = 300 Ω, C = 35 pF ON L L 95 105 115 ns max V = 10 V, see Figure 36 S t (EN) 83 ns typ R = 300 Ω, C = 35 pF OFF L L 100 125 140 ns max V = 10 V, see Figure 36 S Break-Before-Make Time Delay, t 25 ns typ R = 300 Ω, C = 35 pF BBM L L 10 ns min V = V = 10 V, see Figure 35 S1 S2 Charge Injection 0.4 pC typ V = 0 V, R = 0 Ω, C = 1 nF, see Figure 37 S S L Off Isolation −85 dB typ R = 50 Ω, C = 5 pF, f = 1 MHz, see Figure 38 L L Channel to Channel Crosstalk −85 dB typ R = 50 Ω, C = 5 pF, f = 1 MHz, see Figure 40 L L Total Harmonic Distortion Plus Noise 0.15 % typ R = 10 kΩ, 5 V rms, f = 20 Hz to 20 kHz, L see Figure 41 −3 dB Bandwidth 550 MHz typ R = 50 Ω, C = 5 pF, see Figure 39 L L C (Off) 1 pF typ f = 1 MHz, V = 0 V S S 1.5 pF max f = 1 MHz, V = 0 V S C (Off), ADG1208 6 pF typ f = 1 MHz, V = 0 V D S 7 pF max f = 1 MHz, V = 0 V S C (Off), ADG1209 3.5 pF typ f = 1 MHz, V = 0 V D S 4.5 pF max f = 1 MHz, V = 0 V S Rev. E | Page 3 of 21

ADG1208/ADG1209 Data Sheet −40ºC to −40ºC to Parameter +25ºC +85ºC +125ºC Unit Test Conditions/Comments C , C (On), ADG1208 7 pF typ f = 1 MHz, V = 0 V D S S 8 pF max f = 1 MHz, V = 0 V S C , C (On), ADG1209 5 pF typ f = 1 MHz, V = 0 V D S S 6 pF max f = 1 MHz, V = 0 V S POWER REQUIREMENTS V = +16.5 V, V = −16.5 V DD SS I 0.002 µA typ Digital inputs = 0 V or V DD DD 1.0 µA max I 220 µA typ Digital inputs = 5 V DD 380 µA max I 0.002 µA typ Digital inputs = 0 V or V SS DD 1.0 µA max I 0.002 µA typ Digital inputs = 5 V SS 1.0 µA max V /V ±5/±16.5 V min/max |V | = |V | DD SS DD SS 1 Guaranteed by design, not subject to production test. Rev. E | Page 4 of 21

Data Sheet ADG1208/ADG1209 SINGLE SUPPLY V = 12 V ± 10%, V = 0 V, GND = 0 V, unless otherwise noted. Temperature range is as follows: Y version: –40°C to +125°C. DD SS Table 2. −40ºC to −40ºC to Parameter +25ºC +85ºC +125ºC Unit Test Conditions/Comments ANALOG SWITCH Analog Signal Range 0 to V V DD On Resistance, R 300 Ω typ V = 0 V to 10 V, I = −1 mA, see Figure 31 ON S S 475 567 625 Ω max V = 10.8 V, V = 0 V DD SS On-Resistance Match Between 5 Ω typ V = 0 V to 10 V, I = −1 mA S S Channels, ∆R ON 16 26 27 Ω max On-Resistance Flatness, R (On) 60 Ω typ V = 3 V/6 V/9 V, I = −1 mA FLAT S S LEAKAGE CURRENTS V = 13.2 V DD Source Off Leakage, I (Off) ±0.003 nA typ V = 1 V/10 V, V = 10 V/1 V, see Figure 32 S S D ±0.1 ±0.6 ±1 nA max Drain Off Leakage, I (Off) ±0.003 nA typ V = 1 V/10 V, V = 10 V/1 V, see Figure 32 D S D ADG1208 ±0.1 ±0.6 ±1 nA max ADG1209 ±0.1 ±0.6 ±1 nA max Channel On Leakage I , I (On) ±0.02 nA typ V = V = 1 V or 10 V, see Figure 33 D S S D ADG1208 ±0.2 ±0.6 ±1 nA max ADG1209 ±0.2 ±0.6 ±1 nA max DIGITAL INPUTS Input High Voltage, V 2.0 V min INH Input Low Voltage, V 0.8 V max INL Input Current, I or I ±0.001 INL INH ±0.1 µA max V = V or V IN INL INH Digital Input Capacitance, C 3 pF typ IN DYNAMIC CHARACTERISTICS1 Transition Time, t 100 ns typ R = 300 Ω, C = 35 pF TRANSITION L L 170 210 235 V = 8 V, see Figure 34 S t (EN) 90 ns typ R = 300 Ω, C = 35 pF ON L L 110 140 160 V = 8 V, see Figure 36 S t (EN) 105 ns typ R = 300 Ω, C = 35 pF OFF L L 130 155 175 V = 8 V, see Figure 36 S Break-Before-Make Time Delay, t 45 ns typ R = 300 Ω, C = 35 pF BBM L L 20 ns min V = V = 8 V, see Figure 35 S1 S2 Charge Injection −0.2 pC typ V = 6 V, R = 0 Ω, C = 1 nF, see Figure 37 S S L Off Isolation −85 dB typ R = 50 Ω, C = 5 pF, f = 1 MHz, see Figure 38 L L Channel to Channel Crosstalk −85 dB typ R = 50 Ω, C = 5 pF, f = 1 MHz, see Figure 40 L L −3 dB Bandwidth 450 MHz typ R = 50 Ω, C = 5 pF, see Figure 39 L L C (Off) 1.2 pF typ f = 1 MHz, V = 6 V S S 1.8 pF max f = 1 MHz, V = 6 V S C (Off), ADG1208 7.5 pF typ f = 1 MHz, V = 6 V D S 9 pF max f = 1 MHz, V = 6 V S C (Off), ADG1209 4.5 pF typ f = 1 MHz, V = 6 V D S 5.5 pF max f = 1 MHz, V = 6 V S C , C (On), ADG1208 9 pF typ f = 1 MHz, V = 6 V D S S 10.5 pF max f = 1 MHz, V = 6 V S C , C (On), ADG1209 6 pF typ f = 1 MHz, V = 6 V D S S 7.5 pF max f = 1 MHz, V = 6 V S Rev. E | Page 5 of 21

ADG1208/ADG1209 Data Sheet −40ºC to −40ºC to Parameter +25ºC +85ºC +125ºC Unit Test Conditions/Comments POWER REQUIREMENTS V = 13.2 V DD I 0.002 µA typ Digital inputs = 0 V or V DD DD 1.0 µA max I 220 µA typ Digital inputs = 5 V DD 380 µA max V 5/16.5 V min/max V = 0 V, GND = 0 V DD SS 1 Guaranteed by design, not subject to production test. Rev. E | Page 6 of 21

Data Sheet ADG1208/ADG1209 ABSOLUTE MAXIMUM RATINGS TA = 25°C, unless otherwise noted. Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a Table 3. stress rating only; functional operation of the product at these Parameter Rating or any other conditions above those indicated in the operational V to V 35 V DD SS section of this specification is not implied. Operation beyond V to GND −0.3 V to +25 V DD the maximum operating conditions for extended periods may V to GND +0.3 V to −25 V SS affect product reliability. Analog Inputs1 V − 0.3 V to V + 0.3 V or SS DD ESD CAUTION 30 mA (whichever occurs first) Digital Inputs1 GND − 0.3 V to V + 0.3 V or DD 30 mA (whichever occurs first) Continuous Current, S or D 30 mA Peak Current, S or D (Pulsed at 100 mA 1 ms, 10% Duty Cycle Maximum) Operating Temperature Range Industrial (Y Version) −40°C to +125°C Storage Temperature −65°C to +150°C Junction Temperature 150°C θ Thermal Impedance JA TSSOP 112°C/W LFCSP 30.4°C/W SOIC 77°C/W Reflow Soldering Peak 260(+0/−5)°C Temperature (Pb-Free) 1 Overvoltages at A, EN, S, or D are clamped by internal diodes. Current should be limited to the maximum ratings given. Rev. E | Page 7 of 21

ADG1208/ADG1209 Data Sheet PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS A0 1 16 A1 A0 1 16 A1 EN 2 15 A2 EN 2 15 A2 VSS 3 ADG1208 14 GND VSSS1 34 ATDOPG V1I2E0W8 1143 GVDNDD S1 4 (NToOtPtoVSIEcWale) 13 VDD S2 5 (Not to Scale) 12 S5 S2 5 12 S5 S3 6 11 S6 SSD43 678 11910 SSS786 05713-002 SD4 78 190 SS78 05713-006 Figure 3. 16-Lead TSSOP Pin Configuration (ADG1208) Figure 4. 16-Lead SOIC Pin Configuration (ADG1208) Table 4. 16-Lead TSSOP and 16-Lead SOIC Pin Function Descriptions (ADG1208) Pin No. Mnemonic Description 1 A0 Logic Control Input. 2 EN Active High Digital Input. When low, the device is disabled and all switches are off. When high, Ax logic inputs determine on switches. 3 V Most Negative Power Supply Potential. In single-supply applications, it can be connected to ground. SS 4 S1 Source Terminal 1. Can be an input or an output. 5 S2 Source Terminal 2. Can be an input or an output. 6 S3 Source Terminal 3. Can be an input or an output. 7 S4 Source Terminal 4. Can be an input or an output. 8 D Drain Terminal. Can be an input or an output. 9 S8 Source Terminal 8. Can be an input or an output. 10 S7 Source Terminal 7. Can be an input or an output. 11 S6 Source Terminal 6. Can be an input or an output. 12 S5 Source Terminal 5. Can be an input or an output. 13 V Most Positive Power Supply Potential. DD 14 GND Ground (0 V) Reference. 15 A2 Logic Control Input. 16 A1 Logic Control Input. Rev. E | Page 8 of 21

Data Sheet ADG1208/ADG1209 N 0 1 2 E A A A 6 5 4 3 1 1 1 1 VSS 1 12 GND S1 2 ADG1208 11 VDD TOP VIEW S2 3 (Not to Scale) 10 S5 S3 4 9 S6 5 6 7 8 4 D 8 7 S S S 1. THE EXPOSEDPAD IS CONNECTED INTERNALLY. FOR INCREASED RELIABILITY OF THE SOLDER JISTOO IILSND TRESERACENODDMT MMOEA TNXHDIMEE USDMU T BHTSAHTTER RTAMHTEAEL,P VACSDAS P.BAEBILITY, 05713-004 Figure 5. 16-Lead LFCSP Pin Configuration (ADG1208) Table 5. 16-Lead LFCSP Pin Function Descriptions (ADG1208) Pin No. Mnemonic Description 1 V Most Negative Power Supply Potential. In single-supply applications, it can be connected to ground. SS 2 S1 Source Terminal 1. Can be an input or an output. 3 S2 Source Terminal 2. Can be an input or an output. 4 S3 Source Terminal 3. Can be an input or an output. 5 S4 Source Terminal 4. Can be an input or an output. 6 D Drain Terminal. Can be an input or an output. 7 S8 Source Terminal 8. Can be an input or an output. 8 S7 Source Terminal 7. Can be an input or an output. 9 S6 Source Terminal 6. Can be an input or an output. 10 S5 Source Terminal 5. Can be an input or an output. 11 V Most Positive Power Supply Potential. DD 12 GND Ground (0 V) Reference. 13 A2 Logic Control Input. 14 A1 Logic Control Input. 15 A0 Logic Control Input. 16 EN Active High Digital Input. When low, the device is disabled and all switches are off. When high, Ax logic inputs determine on switches. EPAD Exposed Pad. The exposed pad is connected internally. For increased reliability of the solder joints and maximum thermal capability, it is recommended that the pad be soldered to the substrate, V . SS Table 6. ADG1208 Truth Table A2 A1 A0 EN On Switch X X X 0 None 0 0 0 1 1 0 0 1 1 2 0 1 0 1 3 0 1 1 1 4 1 0 0 1 5 1 0 1 1 6 1 1 0 1 7 1 1 1 1 8 Rev. E | Page 9 of 21

ADG1208/ADG1209 Data Sheet A0 1 16 A1 A0 1 16 A1 EN 2 15 GND EN 2 15 GND VSS 3 ADG1209 14 VDD SV1SAS 34 ATDOPG V1I2E0W9 1143 SVD1BD S1A 4 (NToOtPtoVSIEcWale) 13 S1B S2A 5 (Not to Scale) 12 S2B S2A 5 12 S2B S3A 6 11 S3B SSD43AAA 678 11910 DSS43BBB 05713-003 SD4AA 78 190 DS4BB 05713-007 Figure 6. 16-Lead TSSOP Pin Configuration (ADG1209) Figure 7.16-Lead SOIC Pin Configuration (ADG1209) Table 7. 16-Lead TSSOP and 16-Lead SOIC Pin Function Descriptions (ADG1209) Pin No. Mnemonic Description 1 A0 Logic Control Input. 2 EN Active High Digital Input. When low, the device is disabled and all switches are off. When high, Ax logic inputs determine on switches. 3 V Most Negative Power Supply Potential. In single-supply applications, it can be connected to ground. SS 4 S1A Source Terminal 1A. Can be an input or an output. 5 S2A Source Terminal 2A. Can be an input or an output. 6 S3A Source Terminal 3A. Can be an input or an output. 7 S4A Source Terminal 4A. Can be an input or an output. 8 DA Drain Terminal A. Can be an input or an output. 9 DB Drain Terminal B. Can be an input or an output. 10 S4B Source Terminal 4B. Can be an input or an output. 11 S3B Source Terminal 3B. Can be an input or an output. 12 S2B Source Terminal 2B. Can be an input or an output. 13 S1B Source Terminal 1B. Can be an input or an output. 14 V Most Positive Power Supply Potential. DD 15 GND Ground (0 V) Reference. 16 A1 Logic Control Input. Rev. E | Page 10 of 21

Data Sheet ADG1208/ADG1209 D NE 0A 1A NG 6 5 4 3 1 1 1 1 VSS 1 12 VDD S1A 2 ADG1209 11 S1B TOP VIEW S2A 3 (Not to Scale) 10 S2B S3A4 9 S3B 5 6 7 8 A A B B 4 D D 4 S S 1. THE EXPOSEDPAD IS CONNECTED INTERNALLY. FOR INCREASED RELIABILITY OF THE SOLDER JISTOO IILSND TRESERACENODDMT MMOEA TNXHDIMEE UDSMU T BHTSAHTTER RTAMHTEAEL,P VACSDAS P.BAEBILITY, 05713-005 Figure 8. 16-Lead LFCSP Pin Configuration (ADG1209) Table 8. 16-Lead LFCSP Pin Function Descriptions (ADG1209) Pin No. Mnemonic Description 1 V Most Negative Power Supply Potential. In single-supply applications, it can be connected to ground. SS 2 S1A Source Terminal 1A. Can be an input or an output. 3 S2A Source Terminal 2A. Can be an input or an output. 4 S3A Source Terminal 3A. Can be an input or an output. 5 S4A Source Terminal 4A. Can be an input or an output. 6 DA Drain Terminal A. Can be an input or an output. 7 DB Drain Terminal B. Can be an input or an output. 8 S4B Source Terminal 4B. Can be an input or an output. 9 S3B Source Terminal 3B. Can be an input or an output. 10 S2B Source Terminal 2B. Can be an input or an output. 11 S1B Source Terminal 1B. Can be an input or an output. 12 V Most Positive Power Supply Potential. DD 13 GND Ground (0 V) Reference. 14 A1 Logic Control Input. 15 A0 Logic Control Input. 16 EN Active High Digital Input. When low, the device is disabled and all switches are off. When high, Ax logic inputs determine on switches. EPAD Exposed Pad. The exposed pad is connected internally. For increased reliability of the solder joints and maximum thermal capability, it is recommended that the pad be soldered to the substrate, V . SS Table 9. ADG1209 Truth Table A1 A0 EN On Switch Pair X X 0 None 0 0 1 1 0 1 1 2 1 0 1 3 1 1 1 4 Rev. E | Page 11 of 21

ADG1208/ADG1209 Data Sheet TYPICAL PERFORMANCE CHARACTERISTICS 200 250 180 TA=25°C VVDSSD==–+1155VV VVDSSD == –+1155VV 160 VDD=+13.5V 200 VSS=–13.5V TA = +125°C Ω) 140 Ω) CE ( 120 CE ( 150 TA = +85°C N N SISTA 100 VVDSSD==–+1166..55VV SISTA TA = +25°C RE 80 RE 100 N N TA = –40°C O 60 O 40 50 20 0–18 –15 –12 –S9OUR–C6E O–R3DRA0INV3OLTA6GE(9V) 12 15 18 05713-030 0–15 –10 SOUR–C5E OR DRA0IN VOLTA5GE (V) 10 15 05713-033 Figure 9. On Resistance as a Function of VD (VS) for Dual Supply Figure 12. On Resistance as a Function of VD (VS) for Different Temperatures, Dual Supply 600 600 TA=25°C VVDSSD==–+44..55VV TA = +125°C VVDSSD == 01V2V 500 500 VDD=+5V NCE (Ω) 400 VSS=–5V NCE (Ω) 400 TA = T+A8 5=° C+25°C A A SIST 300 VVDSSD==–+55..55VV SIST 300 E E R R ON 200 ON 200 TA = –40°C 100 100 0 0 –6 –4 SOUR–C2E ORDRA0INVOLTA2GE(V) 4 6 05713-031 0 2 SOUR4CE OR DRA6IN VOLTA8GE (V) 10 12 05713-034 Figure 10. On Resistance as a Function of VD (VS) for Dual Supply Figure 13. On Resistance as a Function of VD (VS) for Different Temperatures, Single Supply 450 400 400 TA=25°C VVDSSD==01V0.8V 300 VVVDSBSDIA =S= =–+1 1+551VV0V/–10V E (Ω) 330500 VVDSSD==01V2V NT (pA) 210000 ID (OFF) + – ID, S (ON) + + RESISTANC 225000 VVDSSD==01V3.2V AGE CURRE–1000 ID, S (ON) – – IS (OFF) + – ON 150 LEAK–200 ID (OFF) – + IS (OFF) – + 100 –300 50 00 2 SO4URCE OR6DRAINV8OLTAG1E0(V) 12 14 05713-032 –4000 10 20 30 40TEM50PER6A0TU7R0E (°8C0) 90 100 110 120 05713-057 Figure 11. On Resistance as a Function of VD (VS) for Single Supply Figure 14. ADG1208 Leakage Currents as a Function of Temperature, Dual Supply Rev. E | Page 12 of 21

Data Sheet ADG1208/ADG1209 150 6 VVDSSD == 01V2V DTAEM=U2X5°(CDRAINTOSOURCE) 100 VBIAS = 1V/10V 4 IS (OFF) + – VDD=+5V pA) ID, S (ON) + + pC) VSS=–5V T ( 50 N ( 2 N O RE ID (OFF) + – TI R C EAKAGE CU –500 ID, S (ON) – – ID (OFF) – + IS (OFF) – + HARGE INJE –20 VVDSSD==–+1155VV VVDSSD==0+V12V L C –100 –4 –1500 10 20 30 40TEM50PER6A0TU7R0E (°8C0) 90 100 110 120 05713-058 –6–15 –10 –5 VS0(V) 5 10 15 05713-041 Figure 15. ADG1208 Leakage Currents as a Function of Temperature, Figure 18. Drain-to-Source Charge Injection vs. Source Voltage Single Supply 200 350 IDDPERCHANNEL 180 TA=25C 300 160 140 VVDSDS==–+1155VV 250 VVDSSD==–+55VV 120 I (µA)DD 10800 TIME (ns) 210500 VVDSSD==0+V12V 60 100 VDD=+15V VSS=–15V 40 50 20 VDD=+12V VSS=0V 00 2 4 6LOGIC8, INX(V)10 12 14 16 05713-035 0–40 –20 0 T2E0MPER4A0TURE6(0°C) 80 100 120 05713-052 Figure 16. IDD vs. Logic Level Figure 19. tON/tOFF Times vs. Temperature 1.0 0 MUX(SOURCETODRAIN) 0.9 TA=25°C –10 VVDSSD==–+1155VV 0.8 –20 TA=25C CHARGE INJECTION (pC) 00000.....76543 VVDSSD==–+1155VV VVDSSD==0+V12V OFF ISOLATION (dB) ––––––345678000000 0.2 –90 0.1 VDD=+5V –100 VSS=–5V 0–15 –10 –5 VS0(V) 5 10 15 05713-040 –11010k 100k F1RMEQUENCY1(0HMz) 100M 1G 05713-049 Figure 17. Source-to-Drain Charge Injection vs. Source Voltage Figure 20. Off Isolation vs. Frequency Rev. E | Page 13 of 21

ADG1208/ADG1209 Data Sheet 20 10 VDD=+15V LOAD=10kΩ 0 TVASS==25–°1C5V TA=25°C –20 B) 1 OSSTALK (d ––4600 ADJACENTCHANNELS THD + N (%) VVDDDD==++155VV,,VVSSSS==––51V5,VV,SV=S+=3+.55VVrrmmss R C 0.1 –80 NONADJACENT CHANNELS –100 –120 0.01 10k 100k F1RMEQUENCY1(0HMz) 100M 1G 05713-042 10 100 FREQUE1kNCY(Hz) 10k 100k 05713-036 Figure 21. ADG1208 Crosstalk vs. Frequency Figure 24. THD + N vs. Frequency 0 12 VDD=+15V VSS=–15V –20 10 TA=25°C K (dB) –40 CE (pF) 8 SOURCE/DRAIN ON SSTAL –60 ADJACENTCHANNELS CITAN 6 DRAIN OFF O A R P C –80 CA 4 –100 2 SOURCE OFF NONADJACENT CHANNELS –12010k 100k F1RMEQUENCY1(0HMz) 100M 1G 05713-053 0–15 –10 –5 VBIA0S(V) 5 10 15 05713-043 Figure 22. ADG1209 Crosstalk vs. Frequency Figure 25. ADG1208 Capacitance vs. Source Voltage, ±15 V Dual Supply –6.0 12 VDD=12V –6.5 10 TVASS==250°VC SOURCE/DRAIN ON –7.0 B) F) 8 SE (d –7.5 CE (p DRAIN OFF N N O –8.0 A 6 P T ON RES –8.5 CAPACI 4 –9.0 2 SOURCE OFF –9.5 –10.010k 100k F1RMEQUENCY1(0HMz) 100M 1G 05713-054 00 2 4 VBIA6S(V) 8 10 12 05713-045 Figure 23. On Response vs. Frequency Figure 26. ADG1208 Capacitance vs. Source Voltage, 12 V Single Supply Rev. E | Page 14 of 21

Data Sheet ADG1208/ADG1209 12 8 VDD=12V 10 SOURCE/DRAIN ON 7 TVASS==250°VC 6 SOURCE/DRAIN ON F) 8 F) E (p DRAIN OFF E (p 5 NC VDD=+5V NC DRAIN OFF TA 6 VSS=–5V TA 4 CI TA=25°C CI A A P P 3 CA 4 CA 2 SOURCE OFF 2 SOURCE OFF 1 0–5 –4 –3 –2 –1VBIA0S(V) 1 2 3 4 5 05713-055 00 2 4 VBIA6S(V) 8 10 12 05713-047 Figure 27. ADG1208 Capacitance vs. Source Voltage, ±5 V Dual Supply Figure 29. ADG1209 Capacitance vs. Source Voltage, 12 V Single Supply 8 8 VDD=+15V 7 TVASS==25–°1C5V 7 SOURCE/DRAIN ON 6 6 SOURCE/DRAIN ON F) F) E (p 5 E (p 5 DRAIN OFF C C N N TA 4 TA 4 VDD=+5V CI DRAIN OFF CI VSS=–5V PA 3 PA 3 TA=25°C A A C C 2 2 SOURCE OFF SOURCE OFF 1 1 0–15 –10 –5 VBIA0S(V) 5 10 15 05713-046 0–5 –4 –3 –2 –1VBIA0S(V) 1 2 3 4 5 05713-056 Figure 28. ADG1209 Capacitance vs. Source Voltage, ±15 V Dual Supply Figure 30. ADG1209 Capacitance vs. Source Voltage, ±5 V Dual Supply Rev. E | Page 15 of 21

ADG1208/ADG1209 Data Sheet TERMINOLOGY R t ON TRANSITION Ohmic resistance between D and S. Delay time between the 50% and 90% points of the digital inputs and the switch on condition when switching from one ΔR ON address state to another. Difference between the R of any two channels. ON T I (Off) BBM S Off time measured between the 80% point of both switches Source leakage current when the switch is off. when switching from one address state to another. I (Off) D V Drain leakage current when the switch is off. INL Maximum input voltage for Logic 0. I , I (On) D S V Channel leakage current when the switch is on. INH Minimum input voltage for Logic 1. V (V) D S I (I ) Analog voltage on Terminal D, Terminal S. INL INH Input current of the digital input. C (Off) S I Channel input capacitance for off condition. DD Positive supply current. C (Off) D I Channel output capacitance for off condition. SS Negative supply current. C , C (On) D S Off Isolation On switch capacitance. A measure of unwanted signal coupling through an off channel. C IN Charge Injection Digital input capacitance. A measure of the glitch impulse transferred from the digital t (EN) ON input to the analog output during switching. Delay time between the 50% and 90% points of the digital input Bandwidth and switch on condition. The frequency at which the output is attenuated by 3 dB. t (EN) OFF On Response Delay time between the 50% and 90% points of the digital input The frequency response of the on switch. and switch off condition. Total Harmonic Distortion Plus Noise (THD + N) The ratio of the harmonic amplitude plus noise of the signal to the fundamental. Rev. E | Page 16 of 21

Data Sheet ADG1208/ADG1209 TEST CIRCUITS V ID(ON) S D NC A S D VS IDS 05713-037 NC=NOCONNECT VD 05713-039 Figure 31. On Resistance Figure 33. On Leakage IS(OFF) ID(OFF) S D A A VS VD 05713-038 Figure 32. Off Leakage VDD VSS 3V tr<20ns tf<20ns VDD VSS ADDRESS 50% 50% DRIVE(VIN) A0 0V VIN 50Ω A1 S1 VS1 S2–S7 A2 t t TRANSITION TRANSITION S8 VS8 90% ADG12081 OUTPUT OUTPUT 2.4V EN D GND 300Ω 35pF 90% 1SIMILARCONNECTIONFORADG1209. 05713-022 Figure 34. Address to Output Switching Times, tTRANSITION VDD VSS 3V VDD VSS ADDRESS A0 DRIVE(VIN) S1 VS 0V VIN 50Ω A1 S2–S7 A2 S8 80% 80% ADG12081 OUTPUT OUTPUT 2.4V EN D GND 300Ω 35pF t BBM 1SIMILARCONNECTIONFORADG1209. 05713-023 Figure 35. Break-Before-Make Delay, tBBM Rev. E | Page 17 of 21

ADG1208/ADG1209 Data Sheet VDD VSS 3V VDD VSS ENABLE 50% 50% A0 DRIVE(VIN) S1 VS A1 S2–S8 0V A2 tON(EN) tOFF(EN) ADG12081 OUTPUT 0.9VO 0.9VO EN D OUTPUT VIN 50Ω GND 300Ω 35pF 1SIMILARCONNECTIONFORADG1209. 05713-024 Figure 36. Enable Delay, tON (EN), tOFF (EN) VDD VSS VDD VSS 3V A0 A1 VIN A2 ADG12081 VOUT ∆VOUT RS S D VOUT EN QINJ=CL×∆VOUT VS GND C1nLF VIN 1SIMILARCONNECTIONFORADG1209. 05713-025 Figure 37. Charge Injection Rev. E | Page 18 of 21

Data Sheet ADG1208/ADG1209 VDD VSS VDD VSS 0.1µF 0.1µF 0.1µF 0.1µF NETWORK NETWORK VDD VSS ANALYZER ANALYZER VDD VSS VOUT S 50Ω 5R0LΩ S1 50Ω VS D R D S2 50Ω VOUT RL VS 50Ω GND GND Figure 38. OfOf IFsFo lIaStOioLnA TION=20 log VVOSUT 05713-026 CHANNEL-TO-CHANNELCROSSTALK=20 logVVOSUT 05713-028 Figure 40. Channel to Channel Crosstalk 0.1µFVDD VSS 0.1µF VDD VSS 0.1µF 0.1µF NETWORK VDD VSS ANALYZER VDD VSS AUDIO PRECISION RS S 50Ω S VS IN VS D V p-p D R50LΩVOUT VIN RL VOUT GND 10kΩ GND INSERTIONLOSS=20 logVOVUOTUWTIWTHITOHUSTWSIWTCITHCH 05713-027 Figure 41. THD + N 05713-029 Figure 39. Bandwidth Rev. E | Page 19 of 21

ADG1208/ADG1209 Data Sheet OUTLINE DIMENSIONS 5.10 5.00 4.90 16 9 4.50 6.40 4.40 BSC 4.30 1 8 PIN 1 1.20 MAX 0.15 0.20 0.05 0.09 0.75 0.30 8° 0.60 B0.S6C5 0.19 SEATING 0° 0.45 PLANE COPLANARITY 0.10 COMPLIANT TO JEDEC STANDARDS MO-153-AB Figure 42. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU-16) Dimensions shown in millimeters DETAIL A (JEDEC 95) 4.10 0.35 4.00 SQ 0.30 PIN 1 3.90 0.25 INDICATOR PIN 1 0.65 13 16 (INSEDEIC DAETTAOIRL AAR)EA OPTIONS BSC 12 1 2.25 EXPOSED 2.10 SQ PAD 1.95 9 4 0.70 8 5 0.25 MIN TOP VIEW 0.60 BOTTOM VIEW 0.50 0.80 FOR PROPER CONNECTION OF 0.75 0.05 MAX THE EXPOSED PAD, REFER TO 0.70 THE PIN CONFIGURATION AND 0.02 NOM FUNCTION DESCRIPTIONS COPLANARITY SECTION OF THIS DATA SHEET. SEATING 0.08 PLANE 0.203 REF PKG-004025/5112 COMPLIANTTOJEDEC STANDARDS MO-220-WGGC. 04-15-2016-A Figure 43. 16-Lead Lead Frame Chip Scale Package [LFCSP] 4 mm × 4 mm Body and 0.75 mm Package Height (CP-16-23) Dimensions shown in millimeters Rev. E | Page 20 of 21

Data Sheet ADG1208/ADG1209 10.00 (0.3937) 9.80 (0.3858) 4.00 (0.1575) 16 9 6.20 (0.2441) 3.80 (0.1496) 1 8 5.80 (0.2283) 1.27 (0.0500) 0.50 (0.0197) BSC 1.75 (0.0689) 0.25 (0.0098) 45° 0.25 (0.0098) 1.35 (0.0531) 8° 0.10 (0.0039) 0° COPLANARITY SEATING 0.10 0.51 (0.0201) PLANE 0.25 (0.0098) 1.27 (0.0500) 0.31 (0.0122) 0.17 (0.0067) 0.40 (0.0157) COMPLIANTTO JEDEC STANDARDS MS-012-AC C(RINOEFNPETARRREOENNLCLTEIHN EOGSN EDLSIYM)AEANNRDSEI AORRNOESU NNAORDEET DAIN-PO MPFRIFLO LMPIIMRLELIATIMTEEER TFSEO; RIRN ECUQHSU EDI VIINMA LEDENENSSTIIOGSN NFS.OR 060606-A Figure 44. 16-Lead Standard Small Outline Package [SOIC_N] Narrow Body (R-16) Dimensions shown in millimeters and (inches) ORDERING GUIDE Model1 Temperature Range Package Description Package Option ADG1208YRUZ −40°C to +125°C 16-Lead Thin Shrink Small Outline Package [TSSOP] RU-16 ADG1208YRUZ-REEL7 −40°C to +125°C 16-Lead Thin Shrink Small Outline Package [TSSOP] RU-16 ADG1208YCPZ-REEL −40°C to +125°C 16-Lead Lead Frame Chip Scale Package [LFCSP] CP-16-23 ADG1208YCPZ-REEL7 −40°C to +125°C 16-Lead Lead Frame Chip Scale Package [LFCSP] CP-16-23 ADG1208YRZ −40°C to +125°C 16-Lead Narrow Body Small Outline Package [SOIC_N] R-16 ADG1208YRZ-REEL7 −40°C to +125°C 16-Lead Narrow Body Small Outline Package [SOIC_N] R-16 ADG1209YRUZ −40°C to +125°C 16-Lead Thin Shrink Small Outline Package [TSSOP] RU-16 ADG1209YRUZ-REEL7 −40°C to +125°C 16-Lead Thin Shrink Small Outline Package [TSSOP] RU-16 ADG1209YCPZ-REEL7 −40°C to +125°C 16-Lead Lead Frame Chip Scale Package [LFCSP] CP-16-23 ADG1209YRZ −40°C to +125°C 16-Lead Narrow Body Small Outline Package [SOIC_N] R-16 ADG1209YRZ-REEL7 −40°C to +125°C 16-Lead Narrow Body Small Outline Package [SOIC_N] R-16 1 Z = RoHS Compliant Part. ©2006–2016 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D05713-0-6/16(E) Rev. E | Page 21 of 21

Datasheet下载

Datasheet下载